Скобцовы Моделирование и тестирование

.pdf

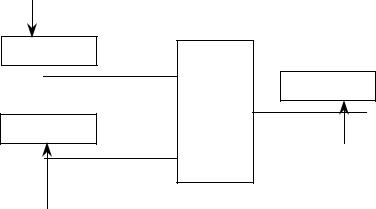

схему, остальные биты соответствуют неисправным схемам: второй –

неисправности f1, третий – f2, четвертый – f3, как это показано на рисунке

5.2.

f1 – неисправность А ≡ 0

1 1 1 1 |

& |

|

|

|||

|

|

A |

0 0 |

0 |

0 |

|

|

|

|

|

|

||

|

|

|

|

|

|

С |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

B |

f3 – неисправность С ≡ 1 |

||

|

|

|

|

|

|

|

f2 – неисправность В ≡ 1

Рис.5.2 Параллельное моделирование

Тогда внесение неисправности на входах выполняется следующим образом:

A=A& m02 = 1111&1011=1011 и

B=B m13 =0000 0010=0010.

Далее выполняется собственно логическая операция вентиля

C=A&B=1011&0010=0010, и затем вносится влияние неисправности на

выходе C=C m14 =0010 0001=0011.

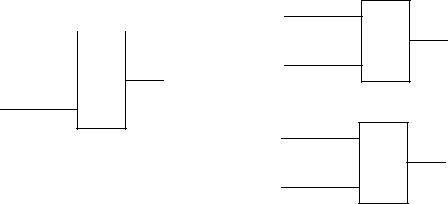

Далее приведем пример параллельного моделирования в двоичном алфавите неисправностей для схемы, представленной на рис.5.3. При этом будем использовать 16-разрядные машинные слова, соответствующие каждой линии схемы для хранения значений сигналов. Рассматриваются только одиночные константные неисправности (число неисправностей может быть сокращено с помощью методов, рассмотренных в предыдущем разделе, но здесь это не важно).

161

Таблица 5.1

|

Испр. |

a ≡ 0 |

b ≡ 1 |

c ≡ 1 |

d ≡ 0 |

e ≡ 1 |

f ≡ 0 |

f ≡ 1 |

|

g ≡ 0 |

g ≡ 1 |

h ≡ 0 |

h ≡ 1 |

i ≡ 0 |

i ≡ 1 |

j ≡ 0 |

j ≡ 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a=1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

b=0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

c=0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

d=1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

f=a&b |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

g=f c |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

h=c&d |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

e=0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

i=e h |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

j=g i |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+ |

+ |

|

+ |

|

+ |

|

|

+ |

|

+ |

|

+ |

|

+ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

162

a |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

f |

|

|

|

|

|

|

|

||||

1 |

|

|

|

|

|

|

|

|

|||||

|

|

G1 |

|

|

|

|

|

|

|

|

|

|

|

b |

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

g |

|

|

|

|

|

||||

0 |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

G2 |

|

|

|

1 |

j |

||

|

|

|

|

|

|

1 |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

G5 |

|

c |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

h |

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|||

d |

1 |

|

|

|

|

G3 |

|

|

1 |

i |

|

|

|

|

|

|

|

|

0 |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

G4 |

|

|

|

|

e |

0 |

|

|

|

|

|

|

|

0 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис.5.3 Параллельное моделирование схемы

Данные моделирования этой схемы для одного входного набора (a=1, b=0, c=0, d=1, e=0) приведены в табл.5.1, где строки таблицы соответствуют линиям этой схемы - машинным словам), а столбцы (биты) –

моделируемым неисправным схемам. При этом в левом столбце приведены имена линий схемы (и логические выражения для внутренних линий), во втором слева столбце логические значения исправной схемы для каждой линии, и последующих столбцах (разрядах машинных слов)

значения сигналов для каждой неисправной схемы. Например, третий слева столбец представляет значения сигналов на моделируемом входном наборе для схемы с неисправностью a ≡ 0. Очевидно, что для определения множества проверяемых неисправностей достаточно сравнить значения сигналов в последней строке, которая соответствует внешнему выходу схемы j. Поскольку исправная схема (второй столбец) имеет на внешнем выходе j=0, то проверяются все неисправности, для которых j=1: b ≡ 1, c ≡ 1,

e ≡ 1, f ≡ 1, g=1, h ≡ 1, i ≡ 1, j ≡ 1.

Мы рассмотрели пример параллельного моделирования схемы на одном тестовом наборе. Для моделирования на тестовой входной последовательности эту процедуру надо выполнить для каждого тестового набора. При этом аналогичным образом определяются неисправности,

проверяемые на наборе. Неисправности, проверяемые всей тестовой

163

последовательностью, находятся путём объединения всех неисправностей,

проверяемых на каждом тестовом наборе.

5.2.2 Параллельное моделирование в троичном алфавите

При параллельном методе моделирования можно использовать

различные виды кодирования троичного алфавита E3={0,1,u}, которые были представлены в разделе 3. Рассмотрим для определенности дизъюнктивный метод кодирования, представленный в табл. 5.2.

Напомним, что здесь каждая троичная переменная X* представлена двумя

двоичными переменными X 0 и X 1 . Соответственно моделирование

одного вентиля в троичном алфавите выполняется с помощью двух булевых функций – компонент F0, F1, приведенных в табл.5.4. При этом,

например, моделирование вентиля И F=A*&B* в троичном алфавите согласно табл.5.3 выполняется с помощью двух логических операций:

F 0 = A0 B0 , F1 = A1 & B1 . Таким образом, фактически моделирование одного вентиля в троичном алфавите, как бы, заменяется моделированием

двух вентилей в двоичном алфавите, что показано на рис. 5.4.

A0

1 F0

A* |

|

|

B |

0 |

|

& |

F*

B*

A1

& F1

B1

Рис.5.4 Моделирование вентиля И в троичном алфавите

164

Таблица 5.2 |

|

|

|

Таблица 5.3 |

|

|||

|

|

|

|

|

|

f* |

|

|

X* |

X 0 |

|

X 1 |

|

f 0 |

f 1 |

||

|

|

|

|

|

|

A*&B* |

|

|

0 |

1 |

|

0 |

A0 B0 |

A1&B1 |

|||

|

|

|

|

|

|

A* B* |

|

|

1 |

0 |

|

1 |

|||||

|

|

|

A0&B0 |

A1 B1 |

||||

|

|

|

|

|

|

|

|

|

U |

1 |

|

1 |

|

|

Ā* |

|

|

|

|

|

A1 |

A0 |

||||

|

|

|

|

|

|

|

|

|

Допустим, что выполняется параллельное моделирование с 4-

разрядными машинными словами. Пусть входы вентиля имеют текущие значения из троичного алфавита A*=1, B*=1. Тогда с учетом

дизъюнктивного кодирования имеем:

A0 = (0 0 0 0 0), A1 =(1 1 1 1 1), B0= (0 0 0 0 0), B1= (1 1 1 1 1).

Пусть в левом разряде моделируется исправная схема, во 2-м разряде

– неисправность A ≡ 0, в 3-м разряде - B ≡ 0, в 4-м разряде -A ≡ 1 и в 5-м

разряде - F ≡ 0. Тогда после внесения влияния неисправностей на входах

имеем:

A0 = (0 1 0 0 0), A1= (1 0 1 1 1),

B0 =(0 0 1 0 0), B1= (1 1 0 1 1).

После выполнения логических операций F 0 = A0 B0 , F1 = A1 & B1 и

внесения неисправности выхода вентиля получаем:

F0 = (0 1 1 0 1) F1 = (1 0 0 1 0).

Очевидно при переходе к троичному алфавиту затраты оперативной памяти возрастают в 2 раза, так как каждой линии схемы соответствует два машинных слова. Быстродействие уменьшается в два раза, так как вместо одной логической операции для стандартных вентилей согласно табл. 5.3

выполняется две операции.

Иногда число проходов ]N/P-1[, необходимое при параллельном методе удается несколько уменьшить за счет того, что несколько независимых неисправностей могут моделироваться в одном и том же

165

разряде. При этом неисправности должны располагаться на линиях схемы,

не влияющих друг на друга.

Существенным ограничением параллельного метода моделирования является то, что при нем функционирование логических элементов должно быть описано с помощью булевых функций. Это связано с тем, что основной выигрыш во времени при этом методе получается путем выполнением логических операций, которые в компьютере реализуются параллельно над всеми разрядами машинных слов. Если же элемент описан на функциональном уровне, то каждую сложную функцию или оператор языка регистровых передач надо описать с помощью булевых функций, что увеличивает сложность модели.

Следует отметить, что параллельный метод использует, как правило,

модель нулевой или единичной задержки логических элементов. Модель задержки с разными значениями для переднего и заднего фронтов также не может быть использована, так как в различных разрядах здесь моделируются различные неисправные схемы, в которых на одной и той же линии могут быть различные фронты изменения сигналов.

На практике часто применяется параллельный по наборам метод моделирования неисправностей. При этом подходе одна неисправная схема моделируется на многих наборах. По сравнению с предыдущем методом, выигрыш может быть достигнут за счёт того, что неисправность проверяется на одном из входных наборов, входящих в текущую группу.

Т.к. неисправность в этом случае уже проверилась, то нет смысла моделировать эту неисправность на оставшихся входных наборах.

5.2.3 Параллельное моделирование в многозначных алфавитах

До настоящего времени в многозначных алфавитах (со значностью больше 4) этот метод распространения не получил, так как при увеличении значности алфавита резко падает скорость моделирования в виду

166

сложности многозначных моделей логических элементов. Метод

кодирования и единая система моделей на базе четырех компонент f 0 , f D' , f D , f 1 позволяют существенно повысить скорость параллельного

метода моделирования в многозначных алфавитах и сделать ее приемлемой для практического применения. При параллельном методе моделирования влияние неисправностей распространяется параллельно для группы р-1 неисправностей (р - разрядность инструментальной ЭВМ).

При этом каждой линии схемы ставится в соответствие несколько машинных слов, число которых определяется количеством компонент в применяемом методе кодирования многозначных алфавитов. Для кодирования, представленного в табл. 3.1 , каждой линии схемы ставится в соответствие четыре машинных слова, как это показано на рис.5.5. При моделировании логических элементов (в данном случае конъюнкции f=ab)

используются функции f 0 , f D' , f D , f 1 табл.4.11. На рис.5.5 приведены

закодированные значения a=(01E1u0), b=(111H1u), из которых согласно

функциям f 0 , |

f D' , f D , |

f 1 |

для этого вентиля |

получаем |

значения, |

||

приведенные |

на |

рис.5.5, |

что |

согласно данному |

методу |

кодирования |

|

|

~ |

|

|

|

D' , f D , |

f 1 |

|

соответствует |

f =(01ЕHu0). При вычислении f 0 , f |

значения |

|||||

всех разрядов обрабатываются параллельно с помощью соответствующих поразрядных булевых операций. Напомним, что функции f 0 , f D' , f D , f 1

основных вентилей таковы, что при равенстве компонент входов a D' , a D , bD' , bD нулю сами функции f D' , f D также равны нулю. Это дает возможность не вычислять их в том случае, когда соответствующие компоненты входов нулевые. При этом, естественно, надо иметь эффективный способ проверки на равенство нулю компонент входов.

Структура модели логического элемента в многозначном алфавите,

учитывающей указанные свойства, представлена на рис.5.6. Заметим

167

также, что внесение константных неисправностей также снижает число

логических элементов, имеющих ненулевые компоненты f D' , f D .

Экспериментальные исследования показывают, что в процессе моделирования относительно небольшая часть логических элементов

имеет ненулевые |

|

компоненты f |

D' , |

f D . |

Это позволяет |

проводить |

||||||||||||||||||||||||||||

моделирование в многозначных алфавитах, |

в основном, вычисляя две |

|||||||||||||||||||||||||||||||||

компоненты |

f D' , f D , |

|

что |

существенно |

повышает |

|

скорость |

|||||||||||||||||||||||||||

моделирования. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

a |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

f |

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

b |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Слово a0 |

|

Слово aD’ |

|

|

Слово aD |

|

|

Слово a1 |

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Сигнал a |

|

1 |

0 |

1 |

0 |

1 |

1 |

|

|

0 |

0 |

1 |

0 |

1 |

0 |

|

|

0 |

0 |

0 |

0 |

1 |

0 |

|

|

0 |

1 |

1 |

1 |

1 |

0 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Слово b0 |

|

Слово bD’ |

|

|

Слово bD |

|

|

Слово b1 |

||||||||||||||||||||||||

Сигнал b |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

0 |

0 |

0 |

1 |

0 |

1 |

|

|

0 |

0 |

0 |

0 |

0 |

1 |

|

|

0 |

0 |

0 |

1 |

0 |

1 |

|

|

1 |

1 |

1 |

1 |

1 |

1 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Слово f 0 |

|

Слово f D’ |

|

|

Слово f D |

|

|

Слово f 1 |

||||||||||||||||||||||||

Сигнал f |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

1 |

0 |

1 |

1 |

1 |

1 |

|

|

0 |

0 |

1 |

0 |

1 |

0 |

|

|

0 |

0 |

0 |

1 |

1 |

0 |

|

|

0 |

1 |

1 |

1 |

1 |

0 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис.5.5 Структура данных при моделировании в многозначном алфавите

mod16(a,b)

{

Вычисление компонент |

f 0 , f 1 ; |

||

n |

n |

n |

n |

If( aD′ aD bD′ bD ≠ 0 ) |

|||

i=1 i |

i=1 i |

i=1 i |

i=1 i |

{

Вычисление компонент f 0 , f 1 ;

}

}

Рис.5.6 Моделирование элемента в многозначном алфавите

168

Внесение неисправностей при моделировании в многозначных алфавитах (включая троичный) обычно производится с помощью специальных масок. Для рассматриваемого метода кодирования это может быть выполнено по следующим формулам: x0=x0&M1 M2, xD’=xD’&M1, xD=xD&M1, xl=xl&M1 M3. Здесь все переменные векторные, их длина равна разрядности машинного слова. Маски М1, М2 и МЗ определяют номер разряда в машинном слове и тип вносимой неисправности. Допустим, что неисправность вносится в j-ом разряде. Тогда маска М1(М2,МЗ) содержит все единицы (нули) кроме j-ro разряда. Значения j-х разрядов М1, М2, MЗ

определяются типом вносимых неисправностей. Для исправной линии

М1(j)=1, М2(j)=0, МЗ(j)=0; для неисправностей const0 - М1(j)=0, M2(j)=1,

M3(j)=0; и для неисправностей const1 - М1(j)=0, M2(j)=0, M3(j)=1. Следует отметить, что техника внесения неисправностей с помощью масок достаточно удобна и для моделирования кратных константных и сложных логических неисправностей. Все неисправности, входящие в кратную,

должны заноситься в один и тот же разряд.

На рис.5.7 представлен псевдокод алгоритма параллельного моделирования неисправностей. Здесь, прежде всего, внешнее описание схемы (текстовое или графическое) транслируется в основную структуру данных - систему связанных таблиц, которая описана в разделе 2.7. Далее выполняется трансляция внешнего описания тестовых воздействий и инициализация табличной модели ДУ. Затем формируется список неисп-

равностей ДУ, подлежащих моделированию. При этом в случае первого сеанса в него заносятся все модельные неисправности данного ДУ с ана-

лизом и устранением эквивалентных дефектов. В противном случае список считывается с диска, куда он был записан во время предыдущего сеанса.

Далее выполняется основной цикл по неисправностям, в начале которого формируется текущая группа неисправностей, которая затем моделируется на всех тестовых наборах. Функция "смена_набора" вводит следующий

169

тестовый набор и заносит события (изменения сигналов на внешних входах ДУ) в очередь (QJ) на моделирование. Основной является функция

"моделирование_набора". В ней реализован событийный алгоритм моделирования в многозначном алфавите.

Параллельное_моделирование_неисправностей(схема,тест)

{

Ввод_схемы();

Ввод_теста();

Инициализация_схемы ();

Генерация_сниска_неисправностей();

while(есть неисправности) /* цикл по неисправностям*/

{

Формирование_группы_неисправностей();

while(есть тестовые наборы) /*цикл по тестовым наборам*/

{

Смена_набора(); /* ввод следующего набора */

Внесение_неисправностей_на_внешних_входах();

Моделирование_набора();

Внесение_неисправностей_на_внешних_выходах();

Проверка_обнаружения_неисправностей();

} /* конец цикла по наборам */

Печать_непроверенных_неисправностей();

} /* конец цикла по группам неисправностей */

Печать_полноты_теста();

Запись_непроверенных_неисправностей();

}

Моделирование_набора();

{

Инициализация();

while(есть события)

{

if(есть изменение сигнала)

{

170