Скобцовы Моделирование и тестирование

.pdf

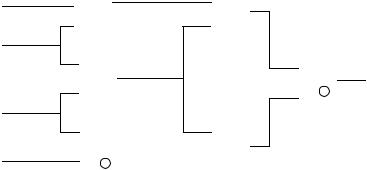

(ИЛИ)». Для того чтобы подобные ситуации могли обрабатываться в процессе логического моделирования в схему вводится дополнительный фиктивный логический элемент И (ИЛИ), как это показано на рис.1.16.

Здесь на рис.1.16 а) представлена исходная схема, а рис.1.16 б) –

преобразованная схема с фиктивным элементом. Следует отметить, что логическое значение на выходе фиктивного элемента при этом всегда правильное, но значения на его входах при такой модели не всегда соответствует реальной схеме. В этой модели входы фиктивного элемента могут иметь различные значения (например, A=0 и B=1 для схемы рис.1.16

б), хотя очевидно, что в реальной схеме они принимают одинаковое значение. При корректном моделировании после вычисления значения выхода фиктивного элемента С его надо присвоить также и обоим входам

A, B. На рис.1.16 б) это показано пунктирными стрелками. Следует отметить, что введение подобных фиктивных элементов нарушает соответствие между моделью и реальной схемой, что может, например,

привести к ошибочной интерпретации результатов моделирования неисправной схемы или построения тестов. Более корректно такие ситуации (и многие другие) моделируются на уровне электрических схем.

& |

A |

|

& |

A |

|

|

|

||

|

|

C |

|

1 |

|

|

|

|

|

|

|

|

|

C |

& |

B |

|

& |

B |

|

|

|

||

|

а) |

|

|

б) |

Рис.1.16 Моделирование монтажной логики фиктивным элементом

1.4Модели уровня ЯРП

Внастоящее время для описания функционирования дискретных устройств широко используются специализированные языки описания

31

цифровой аппаратуры – HDL, которые стали стандартным инструментом при проектировании ДУ. Сейчас вопрос стоит не в том - использовать или не использовать эти языки, а какой именно язык следует использовать при проектировании данного ДУ. Современные языки позволяют описывать ДУ на структурном (вентильном) и функциональном (поведенческом)

уровне. В настоящее время они больше используются для описания ДУ на функциональном или уровне регистровых передач. Использование таких языков позволяет существенно сократить срок проектирования и повысить размерность проектируемых ДУ. Следует отметить, что в настоящее время часто срок жизни (эксплуатации) цифровых систем меньше срока его проектирования. В настоящее время наиболее популярными являются языки проектирования SpecC, VHDL (Very high speed integrated circuits

HDL) и Verilog HDL.

Рассмотрим основные конструкции этих языков. В них входы,

выходы, внутренние состояния и регистры ДУ представляются соответствующими переменными. Как правило, эти переменные должны быть объявлены в начале описания устройства. Например, порты описываются следующим образом:

Port(x1,x2:in BIT; -входные

y:out BIT); -выходные.

Два регистра могут быть описаны следующим образом:

REGISTER R1[1->32], R2[16] ,

где в квадратных скобках указана их разрядность. Аналогичные описания существуют и для других типов устройств (переменных). Так память из 32-

разрядных 256 элементов описывается с помощью объявления

MEMORY[1->256:32].

Обработка и пересылка может быть описана следующим образом:

C A + B ,

32

где выполняется сложение содержимого двух регистров A и B и пересылка

результата в регистр С.

Для описания функционирования ДУ обычно используется

следующие группы операторов ЯРП.

1.Логические операторы: AND, OR, NOT, NAND, NOT, XOR, EQUIV. Эти операторы обычно выполняются над регистрами или некоторыми их разрядами.

2.Операторы сравнения: больше (>), меньше (<), больше или равно

( ≥ ), меньше или равно ( ≤ ), равно (=), не равно (!=). Эти операторы

выполняются над векторами или скалярными переменными. Результатом

является логическое значение 1 или 0.

3. Арифметические операторы: сложение (+), вычитание (-),

умножение (*), деление (/), инкремент, декремент (используются, в

основном, для моделирования функционирования счетчиков ).

4. Битовые операции: правый сдвиг (SR), левый сдвиг (SL),

циклический правый сдвиг (RR), циклический левый сдвиг (RL) и

конкатенация (сцепление). Эти операторы выполняются над векторными

переменными.

5. Операция пересылки A B содержимого регистра B в регистр

А. Эта операция может быть унарной (выполняется над одним операндом,

например, A !B ), или бинарной (выполняется над двумя операндами,

например, A B + С ). Единичная задержка неявно ассоциируется с операцией пересылки. Произвольная задержка должна быть указана явно

(например, A B - С DELAY 10).

6.Условные операторы:

1)бинарный: IF C THEN B1 ELSE B2 IFEND;

где С является условием, а B1 и B2 – блоки, состоящие из операторов.

2)оператор ветвления типа CASE:

33

TEST (E0);

CASE E0:B0;

CASE E1:B1;

CASE E2:B2;

. . .

CASE En:Bn;

TESTEND;

где E являются выражениями и B – блоки. Таким образом, может быть описан, например, дешифратор.

Конечные автоматы могут быть описаны двумя способами. При первом (функциональном) подходе языковыми средствами с помощью условных операторов описывается непосредственно таблица переходов и выходов автомата [46]. При втором (структурном) подходе фактически автомат представляется и описывается структурной моделью рис.1.6 [46].

В соответствии с трактовкой понятия времени ЯРП можно разделить на две категории: процедурные и непроцедурные языки. Процедурные ЯРП похожи на обычные языки программирования (такие как Паскаль, С и т.п.), где операторы и утверждения языка выполняются последовательно таким образом, что результат выполненного оператора становится доступным для следующих операторов. Например, при выполнении операторов A=B; С=A содержимое переменной (регистра) С станет равным содержимому переменной B. Поэтому некоторые процедурные ЯРП являются расширением обычных языков программирования (например, С, HDL). С другой стороны операторы и утверждения непроцедурных языков выполняются параллельно. В непроцедурных языках выполнение операторов A=B; B=A соответствует обмену содержимым регистров A и B.

Современные языки описания аппаратуры часто являются смешанными, то есть имеют как процедурные так и не процедурные средства описания и интерпретации.

34

2.ЛОГИЧЕСКОЕ МОДЕЛИРОВАНИЕ

2.1Состав и назначение программ логического моделирования

Логическое моделирование представляет собой процедуру проверки функционирования логической схемы с помощью компьютера. Его основная цель состоит в том, чтобы проверить функцию проектируемой логической схемы без ее физической реализации, поскольку после изготовления схемы внесение изменений в нее при современной технологии сделать нелегко и недешево. Верификация выполняется путем сравнения результатов моделирования, полученных для проектируемого ДУ, со спецификацией. При этом проверяются как логические функции,

так и временные соотношения.

Логическое моделирование включает в себя построение математической модели ДУ - системы соотношений, описывающей поведение исследуемого устройства с заданной точностью, и дальнейший анализ поведения этой модели на заданной последовательности входных воздействий. При решении задач анализа и диагностирования ДУ обычно используется структурная математическая модель объекта, отражающая совокупность компонентов объекта, связи между компонентами и связь объекта с внешней средой. Для выполнения логического моделирования необходимы следующие компоненты, представленные на рис.2.1: 1)

модель ДУ, 2) входные воздействия, 3) библиотека логических элементов,

4)результаты моделирования. Здесь внешнее описание схемы

(графическое либо текстовое на специализированном языке) транслируется во внутреннее представление модели ДУ, которое непосредственно используется в процессе моделирования. Входные воздействия также могут быть описаны графически с помощью временных диаграмм либо текстом на специализированном языке. Важнейшей компонентой является библиотека моделей логических элементов, состав которой во многом

35

определяет возможности системы моделирования. Результатом является изменение сигналов во времени для внешних и внутренних переменных модели в виде таблиц или временных диаграмм, которые записываются на

диск.

Внешнее описание схемы

Внутреннее

представление

схемы

Входные |

|

|

|

|

Библиотека |

|||

Программа |

||||||||

воздействия, |

|

|

|

|

элементов |

|||

|

|

моделирования |

|

|

||||

|

|

|||||||

управление |

|

|

|

|||||

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Результаты моделирова- ния

Рис.2.1 Структура системы логического моделировании

Логическое моделирование является важнейшей компонентой САПР цифровых систем. С помощью логического моделирования в системах автоматизированного проектирования и диагностирования ДУ исследуются следующие проблемы [47,48]:

−проверка правильности логического функционирования ДУ;

−проверка функционирования цепей установки ДУ;

−проверка временных характеристик ДУ;

36

−анализ состязаний сигналов;

−определение полноты теста и списка непроверенных неисправностей;

−определение диагностических свойств тестов;

−получение диагностической информации для локализации неисправностей ДУ.

При верификации ДУ с помощью логического моделирования необходимо решить следующие проблемы:

1)построение необходимых входных воздействий (генерация тестов);

2)определение корректности полученных результатов;

3)определение качества используемых входных воздействий

(например, полнота проверяющих тестов и т.п.).

Основным математическим аппаратом, применяемым в исследовании цифровых логических схем, является теория булевых функций. При этом функционирование ДУ моделируется в двоичном алфавите {0,1}, что достаточно точно отражает их поведение в статике для установившихся значений сигналов. Однако такие модели не учитывают переходные процессы, возникающие при смене значений входных сигналов и обусловленные временными характеристиками элементов.

Поэтому при исследовании переходных процессов получили распространение многозначные алфавиты, которые позволяют решать эти задачи с известной степенью адекватности логическими средствами без явного задания задержек элементов. Отметим, что в случае анализа переходных процессов мы имеем ДУ в два разные (предыдущий и настоящий) моменты времени и множество линий, на которых значения сигналов в эти моменты различны (или могут быть различны) вследствие изменения некоторых входных сигналов. С другой стороны, при синтезе тестов мы имеем одно ДУ в двух различных технических состояниях

(исправное и неисправное) и множество линий схемы, на которых

37

значения сигналов в этих состояниях различны (или могут быть различны)

вследствие наличия в некоторых элементах неисправностей. В обоих случаях мы исследуем логическую зависимость в ДУ: при моделировании вследствие изменения входных сигналов, при генерации тестов – эффект влияния неисправностей. Поэтому, в силу одинаковой математической природы при построении тестов также широко используются многозначные алфавиты. В обоих случаях анализ двух ДУ в двоичном

(иногда троичном) алфавите заменяется анализом одного устройства в многозначном алфавите.

2.2. Общие принципы логического моделирования

Исходной информацией для программ логического моделирования является описание схемы ДУ в виде сети, вершинами которой являются логические элементы, входы и выходы. Практически каждая система моделирования имеет свои языковые средства для описания схемы ДУ и входных воздействий (тестов).

Далее описание схемы транслируется в некоторое внутреннее машинное представление, которое позволяет эффективно выполнять собственно процесс моделирования. Существует два основных типа машинных моделей схемы: табличная и программная. В соответствии с этим используются два метода моделирования: интерпретативный и компилятивный. Интерпретативное моделирование использует модель схемы в виде ряда таблиц, связанных системой ссылок, является более универсальным и позволяет проводить более точный временной анализ.

Пример основной структуры данных, используемой при этом методе моделирования, можно найти в разделе 2.7.2. Компилятивный метод моделирования использует готовую скомпилированную машинную программу и поэтому является более быстродействующим за счёт сокращения операций поиска адресов нужных значений сигналов и

38

вызовов подпрограмм, которые составляют существенную часть в

интерпретативном методе.

Х1 |

1 |

|

|

|

|

|

|

Х5 |

|

|

Х8 |

|

|

||

& |

|

|

1 |

|

|

||||||||||

|

|

|

0 |

|

|

|

|

|

|||||||

Х2 |

0 |

|

|

|

|

|

|

|

0 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Х6 |

|

|

|

|

Х10 |

||

|

|

|

|

|

|

|

|

|

|

|

|

||||

Х3 |

|

|

& |

|

|

|

|

|

& |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

0 |

|

|

|

|

|

0 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Х4 |

1 |

|

|

& |

|

|

|

Х7 |

1 |

|

|

||||

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

Х9 |

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис.2.2 Пример логического моделирования схемы

Процесс логического моделирования состоит из подачи на внешние входы модели ДУ некоторого входного воздействия и последовательного от входов схемы к ее выходам вычисления значений выходов логических элементов и получения, таким образом, выходной реакции на заданное входное воздействие. На рис.2.2 представлен простой пример комбинационной схемы с результатами логического моделирования в двоичном алфавите для одного входного набора (соответствующий одному моменту времени).

Этот процесс может быть организован по-разному в зависимости от применяемых методов моделирования. Основными отличительными чертами методов логического моделирования являются: модель сигналов,

модель схемы в компьютере, способ учета времени распространения сигналов в ДУ, управление очерёдностью моделирования логических элементов [44,49]. В зависимости от применяемых моделей сигналов,

методы делятся: по алфавиту – на двоичные и многозначные; по используемой модели схемы в компьютере – на интерпретативные и компилятивные; по учёту распространения сигналов – на синхронные (без

39

учета задержек логических элементов) и асинхронные (с учетом задержек);

по очередности моделирования логических элементов – сквозные и событийные [1]. Классификация методов моделирования представлена на

рис.2.3.

Рис.2.3 Методы логического моделирования

Основными характеристиками алгоритмов логического моделирования является адекватность, быстродействие и объём памяти,

необходимый при реализации. При этом под адекватностью понимается степень соответствия результатов моделирования реальному поведению исследуемого ДУ. Для комбинационных ДУ все алгоритмы логического моделирования гарантируют высокую адекватность установившихся значений сигналов. Моделирование последовательностных ДУ может давать результаты различной степени адекватности из-за различных моделей задержек элементов, неопределенности начальных состояний и

40