- •1. Микропроцессоры и микроконтроллеры, их области применения и особенности архитектуры.

- •2. Структура и принцип действия микропроцессора классической архитектуры

- •3. Выполнение процессором командного цикла.

- •4. Машинный и командный цикл cisc микропроцессора

- •5. Структура команды. Способы адресации

- •6.Устройствапамяти, их основные параметры и классификация

- •7. Функциональная схема устройства оперативной памяти

- •8. Постоянные запоминающие устройства, их типы и области применения.

- •9. Применение пзу в качестве функционального преобразователя (фп).

- •10 . Организация подпрограмм и использование стековой области памяти.

- •11.Аппаратные средства интрфейса.

- •12.Програмные средства интерфейса для управления электроприводами

- •13. Параллельный и последовательный интерфейс. Области применения

- •14. Последовательный интерфейс spi микроконтроллеров

- •15. Последовательны интерфейс i2c микроконтроллеров

- •16. Принцип действия программируемого таймера.

- •17. Ввод и вывод информации с применением прерываний.

- •18.Работа вычислительного устройства в режиме прямого доступа к памяти.

- •19. Программная реализация интервалов времени.

- •20. Аппаратная реализация интервалов времени

- •21. Работа таймера в режимах захвата и сравнения

- •22.Цифро-аналоговое преобразование.

- •23.Аналого-цифровое преобразование. Сп.Формирования

- •24. Аналого-цифровые преобразователи. Принципы построения

- •25.Принцип действия ацп поразрядного уравновешивания

- •26. Принцип действия сигма-дельта ацп

- •27.Применение шим для цап

- •28. Микроконтроллер, его функциональная схема и применение в системе управления электроприводом

- •29. Микроконтроллер как динамическое звено.

- •30. Влияние времени выполнения программы микроконтроллером на запас устойчивости и динамические св-ва замкнутой системы

- •31. Выбор числа разрядов слова данных по требуемой точности системы управления.

- •32. Рекурсивные и нерекурсивные цифровые фильтры

- •33. Формирование алгоритма и программ расчёта выходных величин цифровых регуляторов

- •34. Цифровое дифференцирование и интегрирование.

- •36. Кэш-память, ее назначение и принцип действия

- •37. Процессоры с сокращенным набором команд (risc) и с полным набором команд (cisc). Примеры.

- •38. Гарвардская и разнесенная архитектуры микропроцессоров. Примеры.

- •39. Функциональная схема микроконтроллера msp430 и назначение входящих в него устройств.

- •40. Как таймер формирует шим

- •41.Режимы энергопотребления микроконтроллеров. Примеры

- •42. Архитектура risc – ядра arm7 16/32 разрядных микроконтроллеров.

- •43. Как используются преимущества системы команд микроконтроллеров архитектуры arm7 при составлении программы

- •44. Архитектура микроконтроллеров adsp-bf и общая характеристика системы команд.

- •45. Структура ядра adsp-bf и его регистры.

- •46. Применение микроконтроллера tms 320f28 в управлении электроприводами

- •47. Алгоритм расчета сигнала управления в замкнутой системе.

- •48. Преобразование унитарного кода импульсного датчика в двоичный код положения с использованием устройства захвата сравнения.

- •49. Преобразование унитарного кода импульсного датчика в двоичный код скорости при постоянстве интервала времени.

- •50. Преобразование унитарного кода импульсного датчика в двоичный код скорости при постоянстве интервала перемещения.

- •51. Применение программируемого таймера в системах управления эп.

- •52. Использование нечеткой логики для синтеза управления. Лингвист. Переменные.

- •53. Алгоритм нечеткого управления

- •54. Структура и принцип действия искусственного нейрона. Соединение в сеть

- •55. Применение искусственной нейронной сети в качестве устройства управления.

- •56. Применение генетических алгоритмов для оптимизации управления электроприводами.

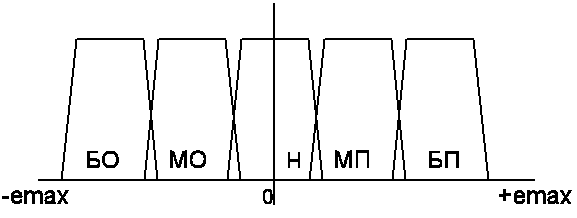

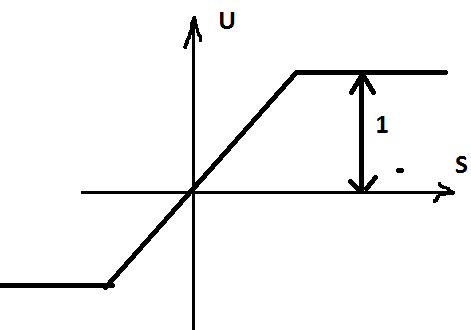

52. Использование нечеткой логики для синтеза управления. Лингвист. Переменные.

Нечеткое

множество – совокупность элементов,

для каждого из которых задана степень

принадлежности к этому множеству. А:

,

гдеx

– элемент,

,

гдеx

– элемент,

- степень принадлежности.

- степень принадлежности. .

Для классических элементов:

.

Для классических элементов: .

.

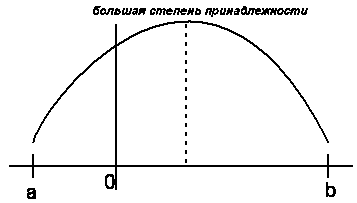

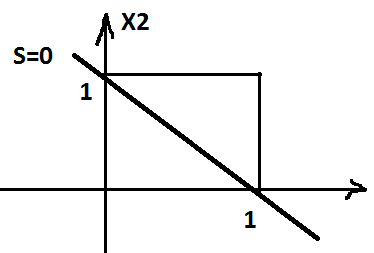

Для нечеткого множества границы а и b размыты, как показано на рисунке:

Функцию

принадлежности строят с помощью

экспертных оценок или на основании

содерж. анализа того или иного множества.

Логические операции для нечетких множеств:

А:

,

В:

,

В: .

.

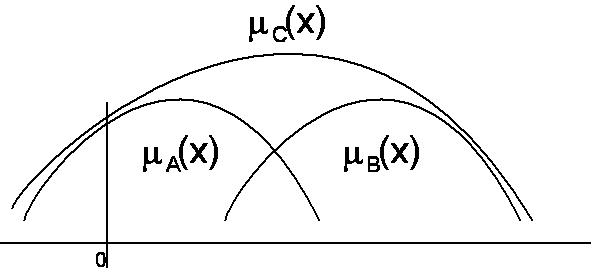

Операция

ИЛИ

:

:

Операция И:

Арифметические

операции:

С=А+В =>

С=А*В =>

Лингвистические

переменные дают большую погрешность.

Применение их позволяет заменить мат.

расчеты логическим выводом. Логические

действия легко алгоритмизируются и не

требуют большого количества разрядов.

Если заменить действующие числа

лингвистическими переменными , то для

формирования управляющего сигнала

возможно применение логических правил

вывода. БП – большое положительное, МП

– малое положительное, Н – нулевое, МО

– малое отрицательное, БО – большое

отрицательное. Когда введены

лингвистические переменные, тогда

каждое из них представляет собой

нечеткое множество.

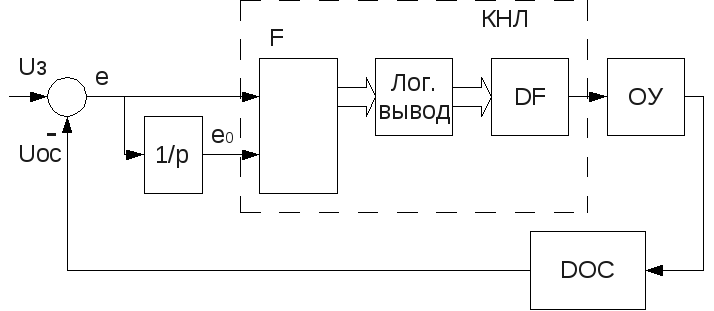

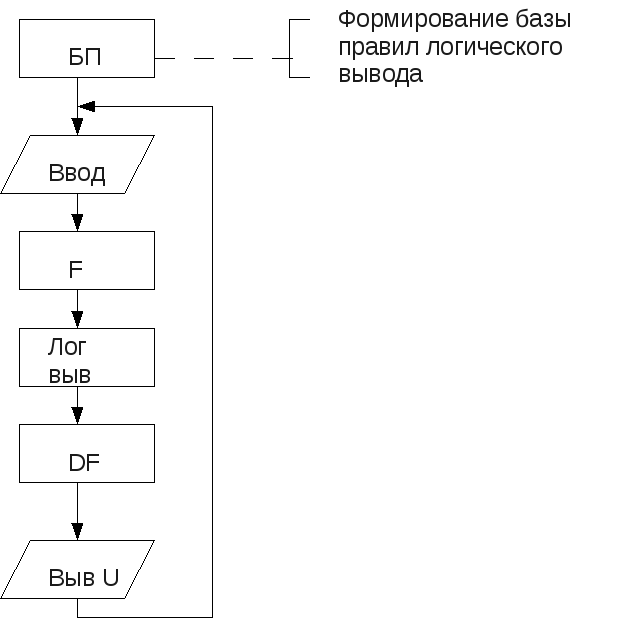

53. Алгоритм нечеткого управления

F-

фазификатор (преобразует непр.Сигнал

в лингвистические переменные)

DF — дефазификатор (лингвистические переменные в непрерывный сигнал)

КНЛ — контроллер нечеткой логики

БП

формируется исходя из цели управления.

Фаззификацией называется преобраз.

действительных значений входных

переменных в лингвистические значения.

Лингвистическое значение — интервал

и функция принадлежности для действительных

чисел. Логический вывод вып-ся на

основании базы правил. В результате

получается лингвистическое значение

сигнала управления с вычисленной

функцией принадлежности. Функция

принадлежности выходной величины

рассчитывается по функции принадлежности

входных лингвистических величин.

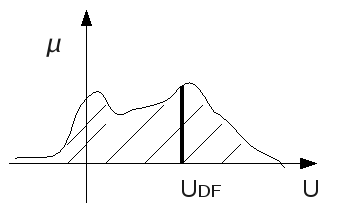

Дефаззификациейназ-ся преобразование лингвистической выходной переменной в действительное число.

Лингвистические значения: NB, NM, NZ, NL, PZ, PL, PM, PB. (на русском: ОБ, ОС, ОМ, ОН, ПН, ПМ, ПС, ПБ)

Если

-

то величина принадлежит интервалу.

-

то величина принадлежит интервалу.

Метод

центра тяжести:

Функция

принадлежности может помимо треугольной

формы иметь сложную форму: Метод середины

площади:

Стандарты для программируемых контроллеров:

IEC 1121-7, IEC 1131-3 (1993u).

FCL — fuzzycontrollanguage — язык нечеткого управления

Область применения языка: управление в системах с ОС и без неё (классификация и распознания, принятие решений, диагностика неисправностей и тд).

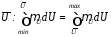

54. Структура и принцип действия искусственного нейрона. Соединение в сеть

Структура искусственного нейрона

W1,…..Wn

– весовые коэфф, Х1,Х2…..Хn

–входные векторы

∑-суммир звено

F(s) – активац ф-ция, U – вых сигнал.

УО – устройство обучения

Искусств нейрон имеет структуру адаптивно-настраиваемого регулятора

Искусств нейрон удобен для реализации на микропроц основе в виде искусств нейросети.

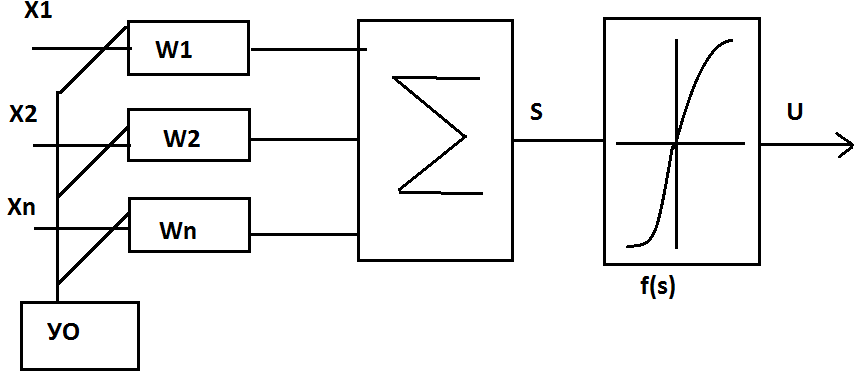

Персептрон имеет функц схему:

dk(w) – требуемое значение вых величины

ƞ

– определяет скорость сходимости

(обучения)

Wk+1=Wk+ƞ*(Uk-dk)*Xk

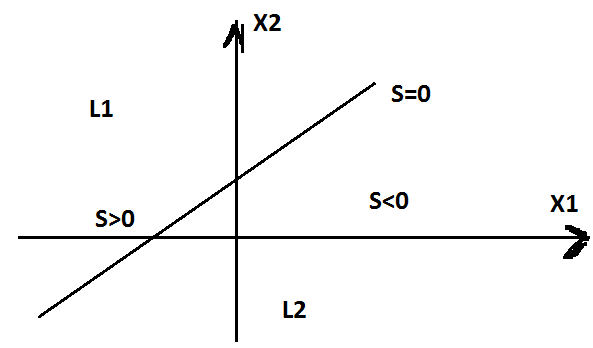

Персептрон

для классиф входных векторов путем

отнесения их к одному из классов L1,L2

X=(X0….Xn)^T – Входной вектор

S=X*W^T – скалярнпроизвед векторов

Значение

выхода искусств нейрона позволяет

определить к какой полуплоскости относ

вектор.

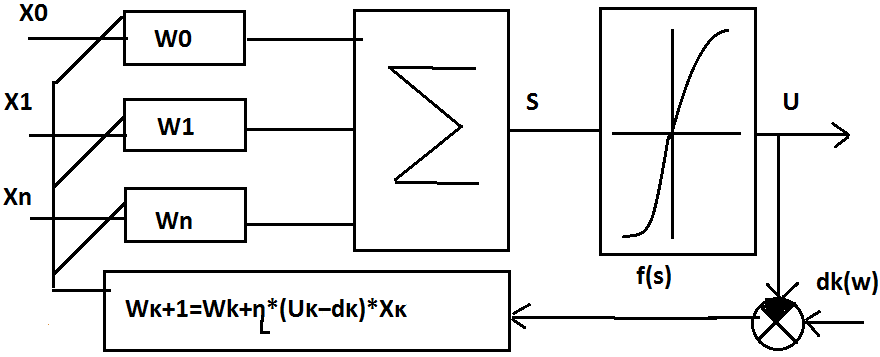

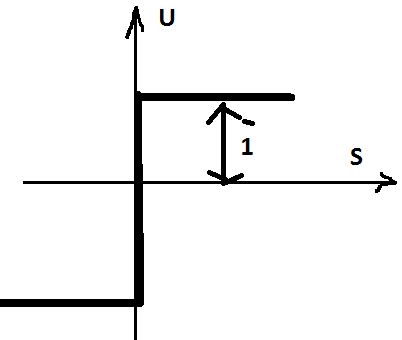

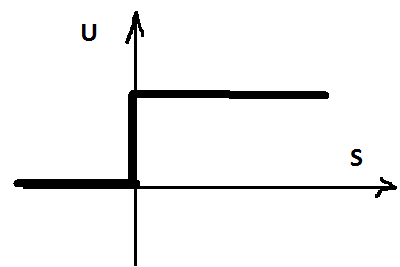

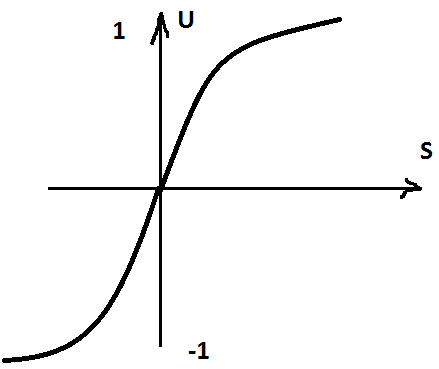

Активация функции может иметь разл вид:

U=max(0,signS)

U=sgnS

U=max(-1,min(S1))

U=1/(1+e^-αS)

U=th(αS)

U=th(αS)

От вида активации ф-ции зависит тип выполнлогич операции. Если f(s) имеет вид релейного элемента, то персептрон может выполнять операции в виде четкой логики.

Если f(s) в виде четкой гладкой кривой, то Персептрон может выполнять операции нечеткой логики.

Выбор алгоритма обучения зависит от задачи.

В

ИНС использ несколько алгоритмов

обучения:

- обучение с учителем: предполагает обучающее множество обуч векторов и каждый из них соотв свой вых сигнал.

- обучение без учителя: использтекущую о входах и выходах

Для выбора метода обучения может быть выбран генетический алгоритм.

Выполнение логических операций персептроном

Х0=±1

или др произвольным числом

Значения, кот могут принимать входн значения

С пом простейшего персептрона невозможно выполнискл ИЛИ

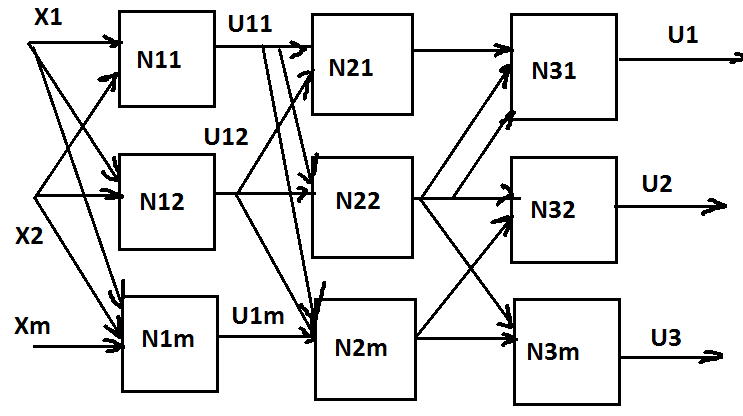

Соединение иск нейронов в сеть

Обычно

использ не более трех слоев нейронных

сетей. Искусств нейросеть имеет регулир

структуру. Кол-во процессорных элементов

равно кол-ву нейронов. Алгоритм обучения

примен к каждому нейрону.