- •1. Микропроцессоры и микроконтроллеры, их области применения и особенности архитектуры.

- •2. Структура и принцип действия микропроцессора классической архитектуры

- •3. Выполнение процессором командного цикла.

- •4. Машинный и командный цикл cisc микропроцессора

- •5. Структура команды. Способы адресации

- •6.Устройствапамяти, их основные параметры и классификация

- •7. Функциональная схема устройства оперативной памяти

- •8. Постоянные запоминающие устройства, их типы и области применения.

- •9. Применение пзу в качестве функционального преобразователя (фп).

- •10 . Организация подпрограмм и использование стековой области памяти.

- •11.Аппаратные средства интрфейса.

- •12.Програмные средства интерфейса для управления электроприводами

- •13. Параллельный и последовательный интерфейс. Области применения

- •14. Последовательный интерфейс spi микроконтроллеров

- •15. Последовательны интерфейс i2c микроконтроллеров

- •16. Принцип действия программируемого таймера.

- •17. Ввод и вывод информации с применением прерываний.

- •18.Работа вычислительного устройства в режиме прямого доступа к памяти.

- •19. Программная реализация интервалов времени.

- •20. Аппаратная реализация интервалов времени

- •21. Работа таймера в режимах захвата и сравнения

- •22.Цифро-аналоговое преобразование.

- •23.Аналого-цифровое преобразование. Сп.Формирования

- •24. Аналого-цифровые преобразователи. Принципы построения

- •25.Принцип действия ацп поразрядного уравновешивания

- •26. Принцип действия сигма-дельта ацп

- •27.Применение шим для цап

- •28. Микроконтроллер, его функциональная схема и применение в системе управления электроприводом

- •29. Микроконтроллер как динамическое звено.

- •30. Влияние времени выполнения программы микроконтроллером на запас устойчивости и динамические св-ва замкнутой системы

- •31. Выбор числа разрядов слова данных по требуемой точности системы управления.

- •32. Рекурсивные и нерекурсивные цифровые фильтры

- •33. Формирование алгоритма и программ расчёта выходных величин цифровых регуляторов

- •34. Цифровое дифференцирование и интегрирование.

- •36. Кэш-память, ее назначение и принцип действия

- •37. Процессоры с сокращенным набором команд (risc) и с полным набором команд (cisc). Примеры.

- •38. Гарвардская и разнесенная архитектуры микропроцессоров. Примеры.

- •39. Функциональная схема микроконтроллера msp430 и назначение входящих в него устройств.

- •40. Как таймер формирует шим

- •41.Режимы энергопотребления микроконтроллеров. Примеры

- •42. Архитектура risc – ядра arm7 16/32 разрядных микроконтроллеров.

- •43. Как используются преимущества системы команд микроконтроллеров архитектуры arm7 при составлении программы

- •44. Архитектура микроконтроллеров adsp-bf и общая характеристика системы команд.

- •45. Структура ядра adsp-bf и его регистры.

- •46. Применение микроконтроллера tms 320f28 в управлении электроприводами

- •47. Алгоритм расчета сигнала управления в замкнутой системе.

- •48. Преобразование унитарного кода импульсного датчика в двоичный код положения с использованием устройства захвата сравнения.

- •49. Преобразование унитарного кода импульсного датчика в двоичный код скорости при постоянстве интервала времени.

- •50. Преобразование унитарного кода импульсного датчика в двоичный код скорости при постоянстве интервала перемещения.

- •51. Применение программируемого таймера в системах управления эп.

- •52. Использование нечеткой логики для синтеза управления. Лингвист. Переменные.

- •53. Алгоритм нечеткого управления

- •54. Структура и принцип действия искусственного нейрона. Соединение в сеть

- •55. Применение искусственной нейронной сети в качестве устройства управления.

- •56. Применение генетических алгоритмов для оптимизации управления электроприводами.

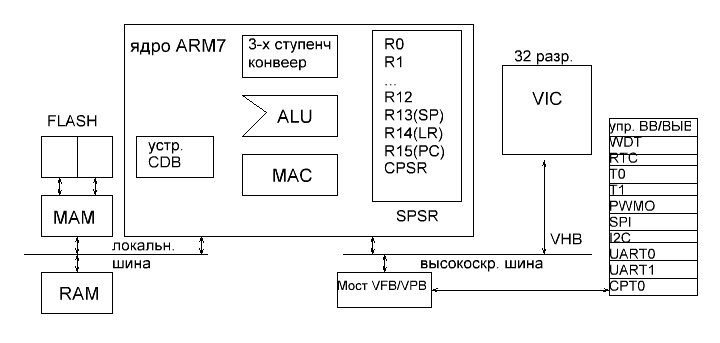

42. Архитектура risc – ядра arm7 16/32 разрядных микроконтроллеров.

Ядра ARM7 применяются во многих микроконтроллерах.

Эта архитектура построена по принципу Loadandstore –загрузка-сохранение LDR,STR.

LDR – из памяти в регистр R←М

STR – сохранение в памяти RM

Ядро

ARM имеет 15 регистров 32 разряда (R0÷R15).

Все операции выполняются внутри

процессора, а конечные результаты

сохраняются в памяти. Ядро ARM содержит

аппаратный сдвигатель MAC для циклических

сдвигов и содержит 3-х ступенчатый

конвейер. (выборка, декодер, выполнение).

Благодаря конвейеру если программа не имеет ветвлений, то в среднем за каждый такт выполняется 1 команда.

Недостаток любого конвейера: если есть ветвления, необходимо сбрасывать конвейер. Если в программе много ветвлений, то конвейер не повышает быстродействие.

Традицстр-ра команды: код операции – адрес

Стр-ра команды для ARM условие-код операции-адрес

Новая

структура команды повышает эффективность

конвеера. Но все команды теперь являются

условными. Если в префиксе записывается

AL – то без условия.

Ядро ARM ещё содержит ALU -аппарат.лог. устр-во.

MAC –аппаратный умножитель с накоплением

Устр. CDB – устр-во цикл. Сдвига

R0…R12 – регистры общего назначения

R13 – указатель стека

R14(LR) – регистр связи с подпрограммой

R15(PC)- прогр. Счётчик

CPSR – регистр состояния

SPSR – буферный регистр, который сохр. содержимое CPSR при изменении режима процессора.

VIC – контр.прерывания

Высокоскоростная шина на 60 Гц.

Мост соединяет высокоскоростную шину и интерфейсные устройства. Для того, чтобы не перегруж. высокоскор. Шину есть локальная шина. Она соед. С оперативной памятью и Flash памятью. Для ускорения доступа к Flash она разделена на 2 банка. MAM управляет расслоением памяти.

PWMO –ШИМ

SPI, I2C – 4-х и 2-х пров. послед.интерфейс

UART0;UART1;GPIO – послед интерфейс стандарты RS232

LR- LinkReg. – регистр связи (хранит адрес возврата из подпрограммы).

Указатель стека позволяет организовать вложенность программы.

43. Как используются преимущества системы команд микроконтроллеров архитектуры arm7 при составлении программы

Первоначальная система команд ARM содержала только 32разрядные инструкции. Однако для систем, критичных к стоимости и объёму памяти программ, к которым относятся практически все встраиваемые системы реального времени, большая длина инструкций оказалась «узким местом», ограничивающим распространение новой архитектуры.

FLASH память – один из наиболее дорогих компонентов системы, и снижение её объёмов – актуальная задача. Поэтому в 1995 г. система команд ARM дополнилась новым набором 16разрядных инструкций, получившим название Thumb.

Из всего набора инструкций ARM были отобраны наиболее употребляемые инструкции и перекодированы в 16 разрядные опкоды. При выборке такой инструкции процессор ARM с помощью простого аппаратного дешифратора восстанавливает истинный 32 разрядный код инструкции, который и выполняется процессором. Таким образом, стандартное 32 разрядное ядро без каких-либо переделок получило возможность работы с 16 битовыми инструкциями.

При разработке Thumb пришлось пожертвовать некоторыми инструкциями, было снижено по сравнению с ARM количество доступных регистров, режимов адресации, ограничен доступ к некоторым системным ресурсам (регистрам состояния, сопроцессорам).

Однако при необходимости процессор может легко сменить режим выбора инструкций, переходя из Thum в ARM и обратно. Имея это в виду, разработчик может гибко управлять поведением своей программы, используя наиболее эффективный для каждого случая набор команд

Одна из важнейших функций ARM ассемблера — условное выполнение. Каждая инструкция может исполняться условно и для этого используются суффиксы. Если суффикс добавляется к названию инструкции, то прежде чем выполнить ее, происходит проверка параметров. Если параметры не соответствуют условию, то инструкция не выполняется. Суффиксы:

MI — отрицательное число

PL — положительное или ноль

AL — выполнять инструкцию всегда

Суффиксов условного выполнения намного больше. Остальные суффиксы и примеры прочитать в официальной документации: ARM документация