- •Ф ізичні явища та принцип дії пт 39

- •Глава1 напівпровідникові прилади

- •1.1 Електронно-дірковий перехід

- •1.1.1 Загальні відомості.

- •1.1.2 Утворення переходу.

- •1.1.3 Контакт метал – напівпровідник.

- •1.2 Напівпровідникові діоди

- •1.2.1 Загальні відомості

- •Продовження таблиці 1.2

- •1.2.2 Характеристики, параметри, область застосування

- •1.2.3 Дослідження напівпровідникових діодів на комп'ютері

- •1.3 Біполярні транзистори

- •1.3.1 Загальні відомості

- •1.3.2 Фізичні явища й принцип дії бт за схемою із загальним емітером

- •1.3.3 Транзистори Шотки

- •1.3.4 Дослідження бт за допомогою комп'ютера

- •1.3.5 Розрахунок режиму спокою підсилювального каскаду на біполярному транзисторі

- •1.3.6 Дослідження підсилювачів електричних сигналів

- •1.4 Польові транзистори (пт)

- •1.4.1 Загальні відомості

- •1.4.2 Фізичні явища та принцип дії пт

- •1.4.2.1 Польові транзистори з керуючим переходом

- •1.4.2.2 Польові транзистори з ізольованим затвором

- •1.4.3 Лізмон-транзистори

- •1.4.4 Мнон - транзистори

- •1.4.6 Дослідження польових транзисторів на комп’ютері

- •Дослідження підсилювачів електричних сигналів

- •Напівпровідникові джерела й приймачі оптичного випромінювання

- •1.5.1 Загальні відомості

- •1.5.2 Оптопари (оптрони)

- •1.6 Перемикаючі прилади

- •1.6.1 Загальні відомості

- •Фізичні явища та характеристика

- •1.7 Інтегральні мікросхеми

- •1.7.1 Загальні положення

- •Глава 2 підсилювачі та генератори електричних сигналів

- •2.1 Загальні відомості.

- •Принцип побудови підсилювальних каскадів.

- •Підсилювальні каскади на біполярних транзисторах.

- •2.3.1 Підсилювальний каскад на біполярному транзисторі за схемою із загальним емітером

- •2.3.2 Підсилювальний каскад на біполярному транзисторі із загальним колектором (емітерний повторювач)

- •2.3.3 Дослідження підсилювачів на біполярних транзисторах

- •Завдання для домашньої підготовки

- •Порядок виконання роботи на комп'ютері

- •Підсилювальний каскад на польовому транзисторі

- •2.5 Багатокаскадні підсилювачі

- •2.6 Каскади посилення потужності

- •2.7 Зворотні зв’язки в підсилювачах

- •Підсилювачі постійного струму

- •2.8.1 Підсилювачі постійного струму на транзисторах.

- •2.8.2 Операційні підсилювачі

- •2.8.3 Дослідження операційних підсилбвачів

- •1 Завдання для домашньої підготовки

- •2 Порядок виконання роботи на комп'ютері

- •2.9 Генератори гармонійних коливань

- •2.9.1 Загальні відомості

- •2.9.4 Дослідження генераторів синусоїдальних коливань

- •Завдання для домашньої підготовки

- •Порядок виконання роботи на комп'ютері

- •2.10 Виборчі підсилювачі

- •2.11 Дослідження підсилювачів електричних сигналів

- •Глава 3 імпульсні пристрої

- •3.1 Загальна характеристика імпульсних сигналів і пристроїв

- •3.2 Ключовий режим роботи транзисторів

- •3.3 Логічні елементи

- •3.3.1 Загальні відомості

- •3.3.2 Логічні елементи в інтегральному виконанні

- •3.3.2.1 Діодно-транзисторні логічні елементи

- •3.3.2.2 Транзисторно логіка -транзисторна

- •3.3.2.3 Логічні елементи на мон-транзисторах

- •3.3.2.4 Логічні елементи на мен-транзисторах

- •3.3.2.5 Інтегральна інжекційна логіка

- •3.3.2.6 Логічні елементи емітерно-зв'язкової логіки

- •3.3.3 Дослідження логічних елементів на комп’ютері

- •3.4 Тригери

- •3.4.1 Загальні відомості

- •Продовження таблиці 3.3

- •3.4.2 Характерні явища для тригерів

- •3.4.3 Дослідження тригерів на комп'ютері

- •3.5 Компаратори і тригери шмітта, генератори імпульсів

- •3.5.1 Загальні відомості

- •3.5.2 Особливості й фізичні явища. Принцип дії.

- •3.5.2.1 Компаратор

- •3.5.2.2 Тригер Шмітта

- •3.5.2.3 Мультивібратори

- •3.5.2.4 Одновібратори

- •3.5.2.5 Блокінг-генератор

- •Генератори лінійно змінюваної напруги

- •3.5.3 Дослідження імпульсних пристроїв на операційних підсилювачах

- •Завдання для домашньої підготовки

- •1 Для компаратора

- •2 Для тригера Шмітта

- •2.1 Записати визначення тригера Шмітта.

- •3 Дослідження схеми мультивібратора

- •4 Для одновібратора:

- •4.1 Записати визначення одновібратора.

- •Порядок виконання роботи на комп'ютері

- •1 Дослідження схеми компаратора.

- •Дослідження схеми тригера Шмітта

- •3 Дослідження схеми мультивібратора

- •4 Дослідження схеми одновібратора

- •До пункту 3.5.2.2

- •До пункту 3.5.2.3

- •3.6 Інтегруючі і диференціюючі rc-ланцюги

- •3.6.1 Інтегруючий rc-ланцюг

- •3.6.2 Диференціюючий rc-ланцюг

- •Глава 4 елементи електронної пам’яті

- •Загальні відомості

- •4.2 Мікросхеми постійних запам'ятовувальних пристроїв

- •4.3 Мікросхеми програмувальних постійних запам'ятовувальних пристроїв

- •Контрольні питання

- •4.4 Принцип побудови динамічного запам'ятовувального елемента

- •Контрольні питання

- •4.5 Елемент флеш- пам'яті

- •4.6 Фероелектрична пам'ять

- •4.7 Магнітна пам'ять

- •4.8 Новий напрямок - спінтроніка

- •Глава 5 перетворювальні електронні пристрої

- •5.1 Загальні відомості

- •5.2 Однофазний однопівперіодний випрямляч

- •5.3 Однофазний двухпівперіодний випрямляч із нульовим виводом

- •5.4 Однофазний мостовий випрямляч

- •5.5 Випрямлячі - помножувачі напруги

- •5.6 Згладжуючі фільтри

- •5.6.1 Дослідження двлпівперіодних випрямлячів однофазного струму

- •Завдання для домашньої підготовки

- •Порядок виконання роботи на комп'ютері

- •5.7 Стабілізатори напруги

- •5.7.1 Параметричні стабілізатори напруги

- •5.7.2 Компенсаційні стабілізатори напруги

- •Контрольні питання

- •5.7.3 Дослідження стабілізаторів напруги

- •Завдання для домашньої підготовки

- •2 Порядок виконання роботи на комп'ютері

- •5.8 Керовані випрямлячі

- •5.9 Інвертори

- •Конвертори

- •Глава 6 Блоки живлення персональних компютерів

- •Додаток а електричні кола постійного струму Основні визначення і закони

- •1 Джерела електричної енергії (джерела живлення).

- •Розрахунок лінійних кіл постійного струму з одним джерелом живлення.

- •Розрахунок лінійних ланцюгів з декількома джерелами живлення.

- •Додаток б електричні кола змінного струму Поняття про змінний струм

- •Основні поняття синусоїдальної функції

- •Зображення синусоїдальної величини вектором

- •Кутова частота і фазові співвідношення

- •Початковий фазовий кут, або початкова фаза.

- •Прості електричні кола змінного струму

- •Список літератури

Продовження таблиці 3.3

1 |

2 |

3 |

D

|

|

|

Т

|

|

|

J-K

|

|

|

3.4.2 Характерні явища для тригерів

Перехід тригера з одного стійкого стану в інше відбувається при впливі керуючого сигналу й супроводжується стрибкоподібною зміною струмів і напруг. У цей час промисловість випускає тригери в інтегральному виконанні. Велику розмаїтість тригерів відрізняє функціональна ознака, що визначає поводження тригера при впливі сигналу керування, а також застосований спосіб керування. По функціональній ознаці розрізняють тригери типів R-S, D, Т, J-K і ін. По способу керування тригери підрозділяють на асинхронні й тактуючі. В асинхронних тригерах перемикання з одного стану в інше здійснюється безпосередньо з надходженням сигналу на інформаційний вхід. У тактируємих тригерах крім інформаційних входів є вхід тактових імпульсів. Їхнє перемикання здійснюється тільки при наявності розв'язного, тактуючого імпульсу. Тригери широко використовують при цифровій обробці інформації в пристроях вимірювальної техніки, автоматики й обчислювальної техніки як елементи пам'яті, лічильників і дільників імпульсів, регістрів і т.д.

3.4.2.1 R-S - тригери

Залежно від способу керування розрізняють асинхронні й тактувальні R-S -тригери.

Асинхронні

R-S - тригери є найпростішими, однак вони

одержали широке поширення в імпульсній

техніці. Схема такого тригера має два

виходи

![]() - прямій і

- прямій і

![]() - інверсний.

- інверсний.

Асинхронний R-S-Тригер, як і тригер будь-якого іншого типу, характеризується двома станами: логічної "1" і логічного "0". По інформаційному входу S здійснюється установка тригера в стан логічної "1", а по інформаційному вході R - установка (перевід) тригера у вихідний стан логічного "0". Цьому відповідають скорочені позначення входів і назва тригера: S - set ( установка), R - reset (повернення у вихідний стан).

S

S

S

&

Q t

Q t

R

R

t

t

&

Q

Q

Q t

Q t

R

Q

Q

t

a) б)

Рисунок 3.14 – Асинхронний R-S – тригер на елементах І-НІ:

а)- схема;

б) – часові діаграми

З аналізу діаграм роботи R-S – тригера виходить, що елементи І-НІ у схемі переключаються послідовно. Є інтервал часу, коли на обох виходах встановлюються однакові сигнали Q=1 і Q (рис.3.14,б, заштриховані області) – явище “ризик”.

3.4.2.2 D - тригери

D - тригери мають один інформаційний вхід і вхід синхронізації ( С-вхід) або тактовий вхід. Стану логічної "1" відповідає одиниця на вході тригера, а стану логічного "О" - нульовий рівень вхідного сигналу.

Перемикання

тригера з одного стійкого стану в інше

відбувається з появою синхронізуючого

(тактового) імпульсу на сході С. Припустимо,

що до моменту приходу вхідного сигналу

тригер перебував в стані логічного нуля

(![]() ,

,

![]() ).

).

В інтервалі часу коли діє вхідний сигнал D , стан тригера не змінюється. Поява тактового імпульсу приводить до перемикання тригера в стан логічної одиниці. Стан "1" тригера не зміниться до моменту часу , коли з'явиться сигнал на вході С та викличе перемикання тригера в стан логічного "0".

На рисунку 3.15 наведена схема D – тригера на елементах І-НІ і його часові діаграми роботи.

&

D1

&

D3

Q C t

Q C t

C t

C t

&

D2

&

D4

Q t

Q t

а) б)

Рисунок 3.15 - D – тригери:

а)– на елементах І-НІ;

б)- часові діаграми роботи.

3.4.2.3 Т-тригер

Характерною властивістю Т-Тригера є його перемикання в протилежний стан із приходом кожного чергового вхідного імпульсу. Через широке застосування в лічильниках імпульсів його часто називають тригером із лічильним запуском. Із приходом першого імпульсу на вхід Т тригер установлюється в стан "1".Другим імпульсом перемикається в стан "0" і т.д. Т-тригер здійснює поділення частоти вхідних імпульсів на два.

На рисунку 3.16 приведена схема Т – тригера на елементах І-НІ і його часові діаграми роботи.

&

D1

&

D3

S Т

C R

Q

Q

Т

Q

Т

Т

Q

Т

&

D2

&

D4

t

t

1

t

Q t

а) б)

Рисунок 3.16 – Асинхронний двоступінчастий Т-тригер:

а)– на елементах І-НІ;

б)- тимчасові діаграми роботи

Надійні структури лічильних тригерів будують з використанням двоступінчастих тригерів або тригерів з динамічним керуванням по фронту сигналу С.

А синхронний двоступінчастий Т-тригер включає в себе два синхронних R-S – тригери, при цьому на Т-вхід основної ступені подається зчитуємий сигнал, а входи R і S з’єднані відповідно з виходами Q і Q допоміжної ступені.

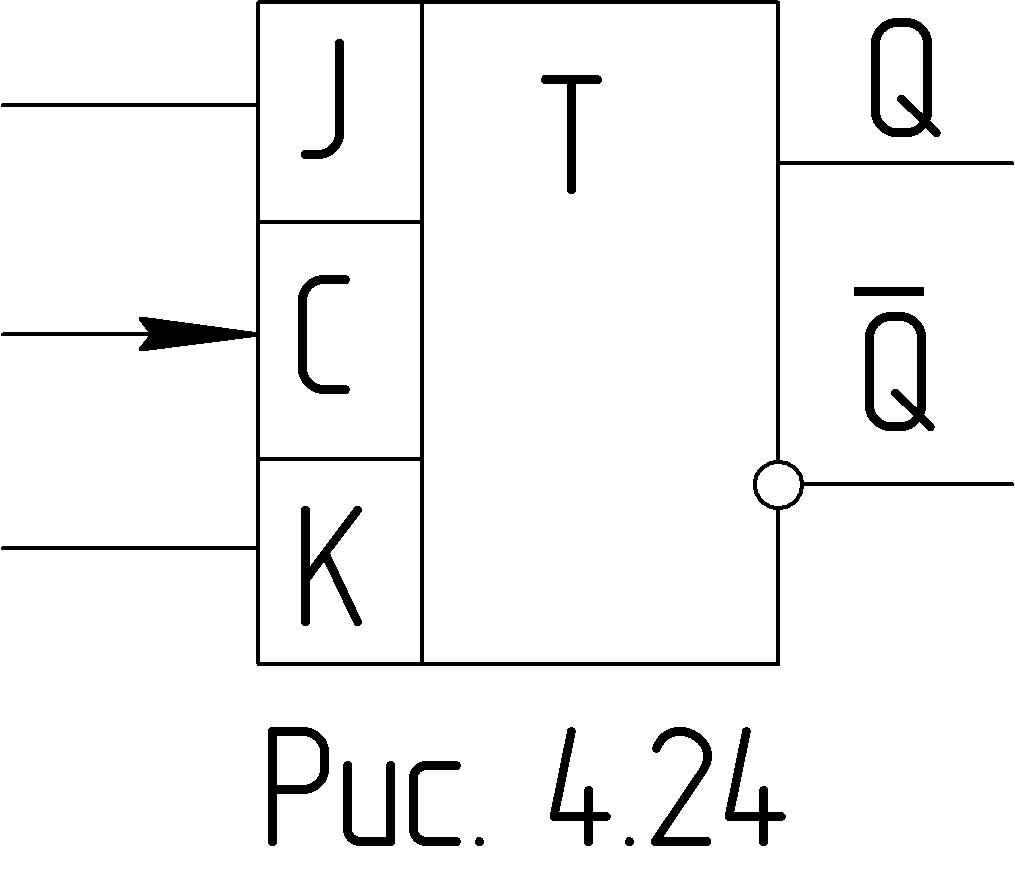

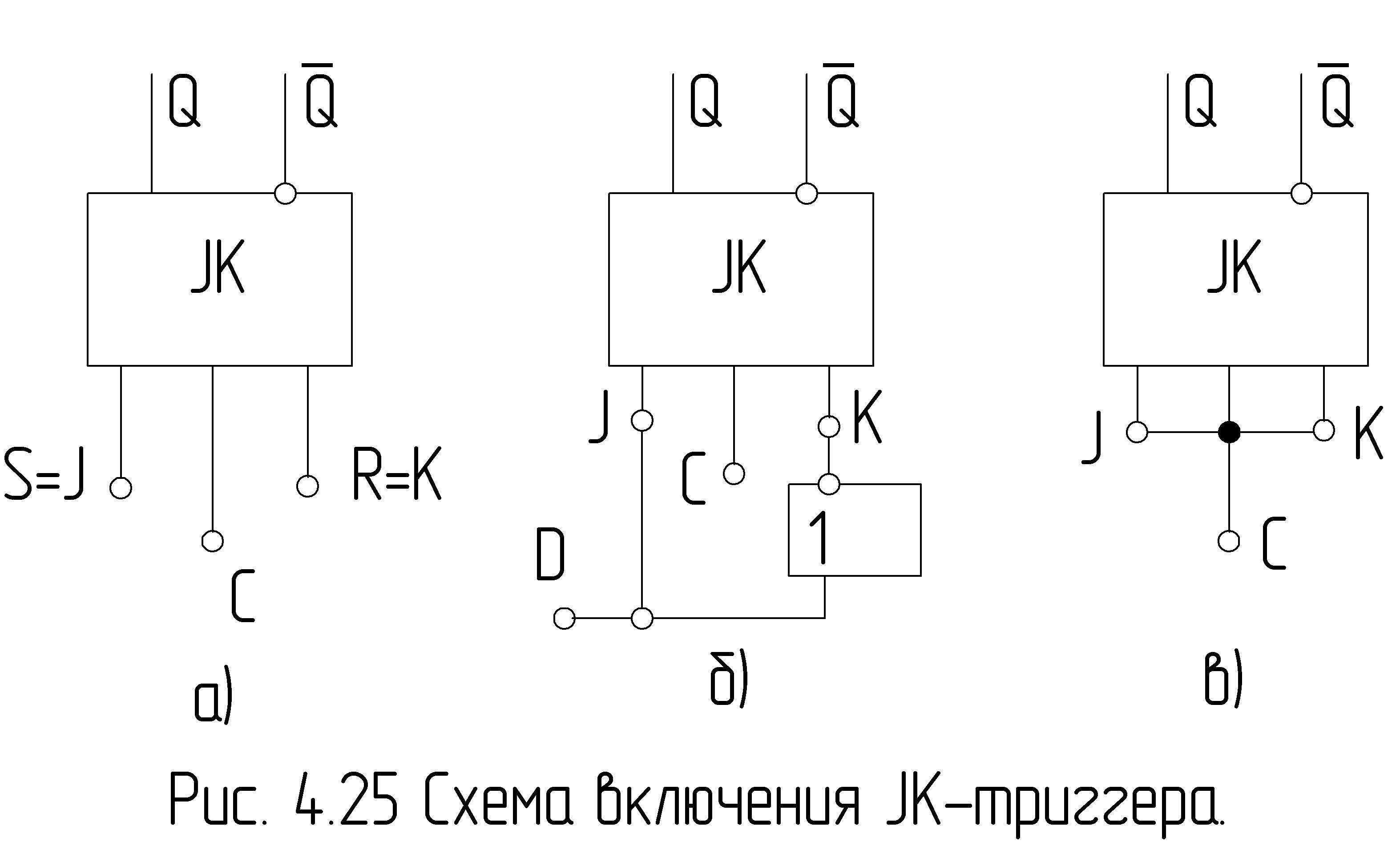

3.4.2.4 J-K-тригер

J-K-Тригер одержують на основі Т-Тригера шляхом використання в його вхідних ланцюгах елементів І, що дозволяє мати два або кілька додаткових входів J і К.

Наявність додаткових входів розширює функціональні можливості тригера, у зв'язку, із чим J-K-Тригер називають універсальним. При відповідному підключенні входів J-K-Тригер, зокрема може виконувати функції R-S -тригера, - D тригера й Т-тригера. R-S-Тригер одержують подачею на вхід J сигналу S, а на вхід ДО - сигналу R. Отриманий R-S-Тригер є тактируємим, D-Тригер створюється введенням інвертора в ланцюг входу К.

Тригер із лічильним запуском реалізується підключенням входів J і К к входу Т.

Деякі D, Т та J-K-Тригери інтегрального виконання мають додаткові входи S і R, як зображено на рис. 3.17.

а) б) в)

Рисунок 3.17 – Побудова на тригері J-K: а) тактуючого R-S тригера;

б) D тригера; в) T тригера.