- •1.Процессоры. Иерархия языков вт

- •4.Алу для деления чисел с фиксир(,)

- •8.Управл автоматы с мпу

- •15. Организация модулей пзу

- •19.Синхр способ продкл ву к см

- •24. Общие принципы построения risc-процессоров. Особенности Берклинской архитектуры.

- •32. Процессор Pentium IV

- •34. Последовательный интерфейс intel 8251(усапп)

- •42.ATmega 32

- •48. Понятие интерфейса. Виды арбитража

- •50.Арбитраж по || опросу.

- •20.Асинхр способ продкл ву к см

- •21. Ппи, подключение ву с помощью ппи

- •30.Процессор Intel 80386, 486, Pentium

- •17.Организация динамических модулей дозу

- •18.Покдл модулей дозу к см(прозр рег).Способы регенерации

- •45 Типовые структуры вс(п/я, многопорт озу, гиперкуб)

- •2.Алу для сложения чисел с фиксир (,)

- •3.Алу для * чисел с фикс(,)_методы ускор *.

- •5.Устройтсво для выполнения лог.Опер.Особеннсти арифм с плавающей (,)

- •6.Многофункциональное алу

- •7.Управляющие автоматы с жесткой логикой

- •9.Требования к кодам команди способы кодирования.

- •16.Организация модулей статического озу.

- •22.Организация кэш памяти.

- •23.Организация виртуальной памяти.

- •25.Старнфордсая структура

- •26.Машины упр потоками данных(df-машины)

- •31.Pentium II,Pentium Pro

- •35.Прогр контр прерываний.

- •37.Таймер

- •38.Орг эвм типа ibm pc at

- •46.Архитектура Сммр,Сvмр,См.

- •47.Сm структура.

- •49.Арбитраж по последовательному опросу.

- •44.Типовые структуры вс (Ош,кажд с кажд…)

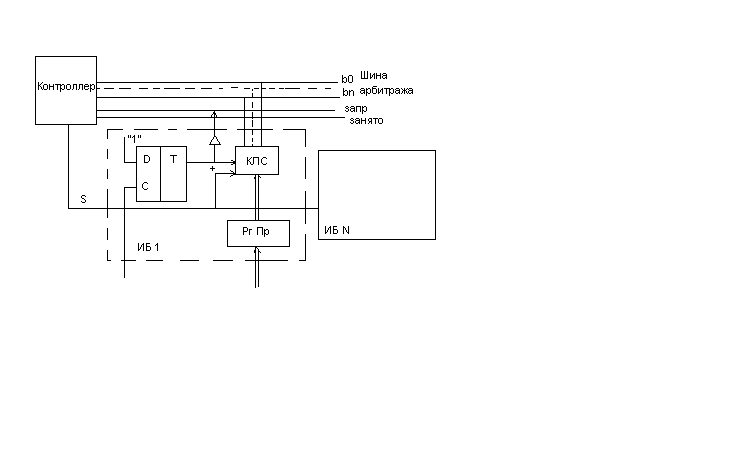

50.Арбитраж по || опросу.

Ш арбитража построена по принципу монтажного «или» любая 1 на выходе ставит bi в 1. В регистр приоритета записывается код приоритета (max приоритет все единички).

|

ai |

bi |

ci |

|

0 |

0 |

1 |

|

1 |

1 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

нет |

щий разряд.

3 строка – устр-во выбыло из кон-курса.

4 строка –невозм-я комбинация

КЛС работает в соответствии с таблицей. Если после анализа старшего разряда СN =1, это означает, что устр-во имеет высший приоритет из всех уч-щих в конкурсе и подключ-х к СМ. Если в процессе сравнения приоритетов Сi =0, устройство выбывает из конкурса. Анализ всех разрядов Ai во всех интерфейсных блоках идет параллельно. Высокое быстродействие, высокие затраты, в кач-ве арбитров исп-ся обычные однокристалки.

20.Асинхр способ продкл ву к см

При асинхр способе обмена Пр1(ЦП) записывает в RG1 код команды для Пр2(ВУ), после этого ЦП периодически обращаясь по фиксированному адресу CS4 и ч/з ШФ3 считывает слово состояние переферийного устройства.

Пр2, получв команду от Пр1 приступает к выполнению команды и сообщает об этом записью определенного кода в RG3 для Пр1. После того, как команда выполнится, Пр2 записывает результат в RG2, а затем записывает СС(в котором говорит, что результат получен и Пр1 может забрать его из RG2) в RG3.

Асинхр способ обмена исключает повторное считывание одной инф-и, ускоряет процесс обмена, паузы простаивания мин.

21. Ппи, подключение ву с помощью ппи

Микросхема КР580ВВ55. ППИ предн. для подкл. периферийных устройств к СМ.

Все 4 канала независимы друг от друга и могут использ. как на ввод так и на вывод инфы.

Порт- овокупность регистра и ШФ.

РУС –регистр управляющего слова.

|

|

ШДА |

ШД→В |

ШД→С |

ШД→РУС | ||||||||

|

CS |

0 |

0 |

0 |

0 | ||||||||

|

WRJO |

0 |

0 |

0 |

0 | ||||||||

|

RDJO |

1 |

1 |

1 |

1 | ||||||||

|

A0 |

0 |

1 |

0 |

1 | ||||||||

|

A1 |

0 |

0 |

1 |

1 | ||||||||

|

|

|

|

|

| ||||||||

|

|

|

|

|

| ||||||||

|

|

|

|

|

| ||||||||

|

|

|

|

|

| ||||||||

|

|

|

|

|

| ||||||||

|

|

|

|

|

| ||||||||

|

|

|

|

|

| ||||||||

|

|

ШД→А |

ШД→В |

ШД→С |

|

CS |

0 |

0 |

0 |

|

WRJO |

1 |

1 |

1 |

|

RDJO |

0 |

0 |

0 |

|

A0 |

0 |

1 |

0 |

|

A1 |

0 |

0 |

1 |

|

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

Режим задается в регистре управляющего слова (РУС).

D0-к С1 (0-ввод 1- вывод;) D1-к В (0-ввод 1- вывод;) D2- реж работы кВ и кС1 (0-реж “0”,1-реж “1”) D3-к С2 (0-ввод 1- вывод;) D4-к А (0-ввод 1- вывод;) D5D6-номер режима для кА и кС2 (00-“0”)(01-“1”)(1х-“2”) D7-1 признак РУС

Режим “0” предн. для синхронных обменов инфой, каждый из каналов независимо друг от друга может передавать или принимать сигналы в зависимости от РУС.

Режим “1” предн. для асинхронного обмена. В этом режиме данные передаются по каналам А и В, канал С исп-ся для формирования битов квитирования.

Если в режиме 0 или 1 требуется поменять направление передачи инфы ППИ необходимо перепрогр-ть(тратится время).

Для скоростного обмена инф-й исп-ся режим 2. В режиме 2 данные могут передаваться только по каналу А. Напр. передачи опред-ся сигналами RDJO, WRJO.