- •1.Процессоры. Иерархия языков вт

- •4.Алу для деления чисел с фиксир(,)

- •8.Управл автоматы с мпу

- •15. Организация модулей пзу

- •19.Синхр способ продкл ву к см

- •24. Общие принципы построения risc-процессоров. Особенности Берклинской архитектуры.

- •32. Процессор Pentium IV

- •34. Последовательный интерфейс intel 8251(усапп)

- •42.ATmega 32

- •48. Понятие интерфейса. Виды арбитража

- •50.Арбитраж по || опросу.

- •20.Асинхр способ продкл ву к см

- •21. Ппи, подключение ву с помощью ппи

- •30.Процессор Intel 80386, 486, Pentium

- •17.Организация динамических модулей дозу

- •18.Покдл модулей дозу к см(прозр рег).Способы регенерации

- •45 Типовые структуры вс(п/я, многопорт озу, гиперкуб)

- •2.Алу для сложения чисел с фиксир (,)

- •3.Алу для * чисел с фикс(,)_методы ускор *.

- •5.Устройтсво для выполнения лог.Опер.Особеннсти арифм с плавающей (,)

- •6.Многофункциональное алу

- •7.Управляющие автоматы с жесткой логикой

- •9.Требования к кодам команди способы кодирования.

- •16.Организация модулей статического озу.

- •22.Организация кэш памяти.

- •23.Организация виртуальной памяти.

- •25.Старнфордсая структура

- •26.Машины упр потоками данных(df-машины)

- •31.Pentium II,Pentium Pro

- •35.Прогр контр прерываний.

- •37.Таймер

- •38.Орг эвм типа ibm pc at

- •46.Архитектура Сммр,Сvмр,См.

- •47.Сm структура.

- •49.Арбитраж по последовательному опросу.

- •44.Типовые структуры вс (Ош,кажд с кажд…)

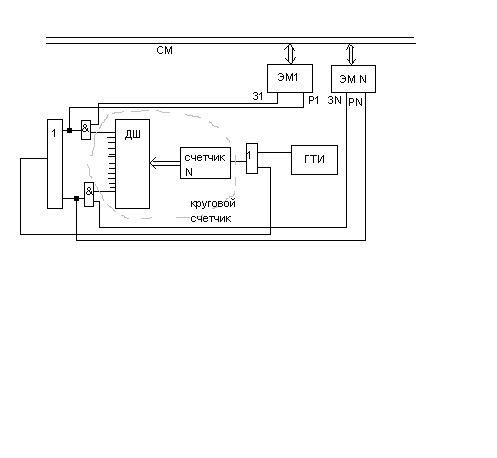

49.Арбитраж по последовательному опросу.

Счетчик имеет коэф-т пересчета N равный числу машин, нуждающихся в общем ресурсе. ДШ подключается к параллельному выходу счетчика, который в конкретный момент имеет только 1 возбужденный выход. Счетчик считает от 0 до N, переполняется, сбрасывается в 0, и 1-ца (маркер) на выходе ДШ бегает по кругу. Пусть ЭМ1 выставила запрос, когда маркер попадает на вход элемента i1 на выходе 1-ца, которая проходит ч/з «или» и блокирует поступление тактовых импульсов на вход счетчика. Одновременно выход элемента «и» есть разрешение для ЭМ1. Получив Р1 ЭМ1 работает с СМ. В каждый мом-т времени маркер может находится только на одном элементе «и» и разрешение м.б. выдано только одной ЭМ. По окончании с СМ ЭМ убирает запрос и на выходе «и» - 0. Вход счетчика разблокируется и маркер побежал дальше.

44.Типовые структуры вс (Ош,кажд с кажд…)

a)Структура с общей шиной:

+ )Простота,

легкая наращи-ваемость вычислителей.

)Простота,

легкая наращи-ваемость вычислителей.

С труктура

достаточно хорошо работает при связных

задачах.Коэфф

связности задач-

это отношение числа команд участвующих

в межмашинном обмене к общему числу

команд выполненных данной машиной (в

%). Число машин ограничивается пропускной

способностью шины.

труктура

достаточно хорошо работает при связных

задачах.Коэфф

связности задач-

это отношение числа команд участвующих

в межмашинном обмене к общему числу

команд выполненных данной машиной (в

%). Число машин ограничивается пропускной

способностью шины.

-) низкая надежность из-за наличия общего ресурса (шины)

б)Каждый с каждым :

+)Увеличение надежности, нет стояния в очереди к общим аппаратн рес-ам.

-)При наращивании числа машин аппаратные затраты увел в геометр прогрессии.

Реально в такой структуре число машин не более 10.

в )Смешанная

структура

:

)Смешанная

структура

:

1)Машины с дублированием шины

Обладает более высокой надежностью чем у стр-ры с общей шиной, т.к. канал продублирован.

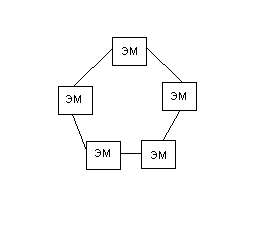

2)Кольцо

+)Легкая наращиваемость

При обрыве структура превращается в 1.

Кольцо и машина с дуплексной связью близки друг к другу по показателям надежности + удобство на-ращивания и при приемлемык аппар затратах.

3 )Различные

варианты древовидных структур

)Различные

варианты древовидных структур

Любая конкретная задача будет решаться эффективнее если под нее сделать специальный вычислитель. Обычно древовидные структуры определяются особенностью алгор-ма реализуемого данным вычислителем.

Структура с общей шиной при обмене инф м/у 2-мя машинами ведущая машина включает(переводит ведомую) в режим ПДП на время обмена инф =>

Процессоры, иерархия языков ВТ.

АЛУ для сложения чисел с фиксированной запятой.

АЛУ для умножения чисел с фиксированной запятой, методом ускоренного умножения.

АЛУ для деления чисел с фиксированной запятой.

Устройство для выполнения логических операций. Особенности арифметики с плавающей запятой.

Многофункциональные АЛУ.

Управляющий автомат с жесткой логикой.

Управляющий автомат с МПУ.

Требования к кодам команд и способы кодирования.

Архитектура, принципы работы и основные сигналы МП 8080:

11. Организация стека, временные диаграммы чтения и записи.

12. Организация и понятие прерываний на примере МП 8080.

13. Способы адресации и форматы команд

14. ШФ и Рг. Организация См на примере МП 8080

Организация модулей ПЗУ.

Организация модулей статического ОЗУ (8 и 16 р.).

Организация динамических модулей ЗУ (ДОЗУ).

Подключение модулей ДОЗУ к СМ и способы регенерации.

Синхронные способы подключения ВУ к СМ.

Асинхронные способы подключения ВУ к СМ.

ППИ. Подключение ВУ к СМ с помощью ППИ.

Организация КЕШ-памяти.

Организация виртуальной памяти.

Общие положения RISC-процессоров. Берклинская архитектура.

Общие положения RISC-процессоров. Стафордская архитектура.

Машины, управляющие потоком данных (DF-машины).

МП Intel 8086. Архитектура, сигналы, принцип работы

Режим мин. включения 8086

Режим мах. включения 8086

Процессоры Intel 80386,486. Pentium (все).

Pentium-2 (Pro).

Pentium-4.

Core 2 (Дио).

Последовательный интерфейс 8251(УСАПП).

Программируемый Контроллер прерываний

Контроллер ПДП 8237.

Таймер 8253

Организация ЭВМ РС\АТ.

ОЭВМ семейства MCS-51, архитектура...

MCS-51:Временные диаграммы, чт/зап вн. ОЗУ, осн сигналы

Подключение внешних модулей ЗУ и ВУ к ОЭВМ MCS-51.

ОЭВМ ATmega32.

Осн. Характеристики соврем. ОЭВМ (по табл) Производительнрость ЭВМ и сетей

Типовые структуры ВС (Ош, кажд с какжд …).

Типовые структуры ВС (п/я,многопортов ОЗУ,…).

Архитектура ВС Cmmp, Cvmp, Cm.

Архитектура ВС Bbur Chip, Минимакс, Сумма.

Понятие интерфейса. Виды арбитража.

Арбитраж по последовательному опросу.

Арбитраж по параллельному опросу.