- •1.Процессоры. Иерархия языков вт

- •4.Алу для деления чисел с фиксир(,)

- •8.Управл автоматы с мпу

- •15. Организация модулей пзу

- •19.Синхр способ продкл ву к см

- •24. Общие принципы построения risc-процессоров. Особенности Берклинской архитектуры.

- •32. Процессор Pentium IV

- •34. Последовательный интерфейс intel 8251(усапп)

- •42.ATmega 32

- •48. Понятие интерфейса. Виды арбитража

- •50.Арбитраж по || опросу.

- •20.Асинхр способ продкл ву к см

- •21. Ппи, подключение ву с помощью ппи

- •30.Процессор Intel 80386, 486, Pentium

- •17.Организация динамических модулей дозу

- •18.Покдл модулей дозу к см(прозр рег).Способы регенерации

- •45 Типовые структуры вс(п/я, многопорт озу, гиперкуб)

- •2.Алу для сложения чисел с фиксир (,)

- •3.Алу для * чисел с фикс(,)_методы ускор *.

- •5.Устройтсво для выполнения лог.Опер.Особеннсти арифм с плавающей (,)

- •6.Многофункциональное алу

- •7.Управляющие автоматы с жесткой логикой

- •9.Требования к кодам команди способы кодирования.

- •16.Организация модулей статического озу.

- •22.Организация кэш памяти.

- •23.Организация виртуальной памяти.

- •25.Старнфордсая структура

- •26.Машины упр потоками данных(df-машины)

- •31.Pentium II,Pentium Pro

- •35.Прогр контр прерываний.

- •37.Таймер

- •38.Орг эвм типа ibm pc at

- •46.Архитектура Сммр,Сvмр,См.

- •47.Сm структура.

- •49.Арбитраж по последовательному опросу.

- •44.Типовые структуры вс (Ош,кажд с кажд…)

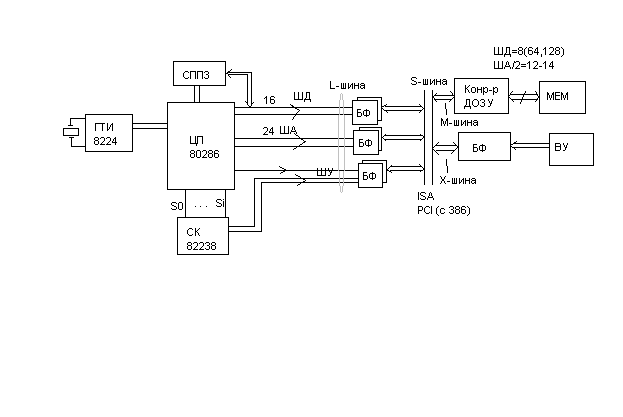

38.Орг эвм типа ibm pc at

8086 80186 80286 80386 80486

L-шина обладает пониженным напряж питания(напр пит ЦП)

S-шина нормальная магистраль 5В. Первое поколение- ISA шины следующее PCI. Как вариант PCI была шина VESA.

М-шина (шина подкл памяти)

Х-шина обращения к ВУ.

ША/2-потому что динамич память (адр строки, адр столбца)

Базовый магистральный кристалл VL82C100- контроллер ВУ (84 конт, 2 контр ПДП 82237, 2 контр прерываний, таймер)

VL82C101-сист контр(генератор тактовык импульсов 8224, сист контр 88238,СППЗ 80287) с пониженным питанмем.

VL82C102-контроллер ДОЗУ

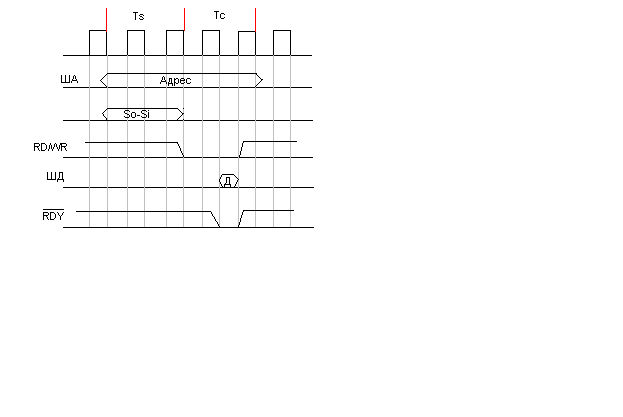

Протокол обмена по системной шине ISA (такой же как у про-цессора 1810ВМ86) каждый обмен выполн за 4 такта. 1 такт состояния 2 такт-командный.

Любая ЭВМ содержит: ЦП, ГТИ, модули ПЗУ, модули ОЗУ, таймер, контролер прерыв(м/б и ПДП), устр упр вв/выв (ППИ), устр последов вв/выв.

Если все эти устр-ва установить на одном кристалле то получится однокристальная ЭВМ (транспьютер).

46.Архитектура Сммр,Сvмр,См.

1)Сmmр – разработчики универ Карнеги Меллона (США).

Перед разр стояла задача создать высоконадежную структуру позволяющую постепенно деградировать.

Каждый проц может подкл к любому модулю память и взять любые задачи для выполнения.

Р(t)- вероятность безотк работы системы. 8-ми проц сист-ма с резервированием.

Надежность невысокая из-за общего коммутато-ра. Резервирование с кра-

т ностью

более 2-х оказалось нецелесеобразн.

ностью

более 2-х оказалось нецелесеобразн.

Система с распределенным коммутатором

Увеличение надежности ≈ на порядок., но резервир с кратностью >2 все равно не целесеобразно.

-)Сложность наращивания и сложное управление комму-татором.

2)Cvmp- разраб те же.

З адача

создать высоконадежный отказоустойчивый

вычислитель при этом пользователь не

должен знать что он высоконадежен.

адача

создать высоконадежный отказоустойчивый

вычислитель при этом пользователь не

должен знать что он высоконадежен.

Структура по принципу мажорирования, Эл-т сравнения V который пропускает рез-т в сис-му в случае его совпадения в 2-х машинах.

О сн

дост:Система

устой-чива к сбоям

сн

дост:Система

устой-чива к сбоям

Высоконадежный вычис-литель парирует сбои в машинах. Отказ одной машины пользователем не замечается.

Начиная с опр времени надежность Cmmp ста-новится выше надеж-ности Cvmp.

47.Сm структура.

1)Одномерный вариант.

+ )Легконастраиваемая

система. Каждая маш-на имеет доступ к

памяти любой другой машины.

)Легконастраиваемая

система. Каждая маш-на имеет доступ к

памяти любой другой машины.

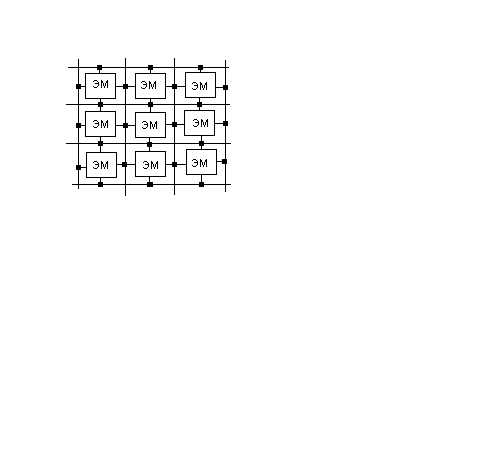

2)Двумерная структура

К аждая

машина имеет 4 порта.

аждая

машина имеет 4 порта.

(Inmos T424) –однокрист ЭВМ

(4 порта – 2 последов и 2 паралл,

8кб ОЗУ 8кб ПЗУ на кажд крист)

Высокая надежность простота распараллеливания алгоритмов.

Университет города Пердью предложил структуру BlueChip :

ЭВМ с программируемой структурой.

Г отовый

набор, а конкретную структуру прожигают

под конкретный алгоритм (заказ).

отовый

набор, а конкретную структуру прожигают

под конкретный алгоритм (заказ).

Новосибирская структура “Сумма” Минимакс

1,2 –интерфейсы последователь-ные ч/з них задается как коммута-ция по параллельным интерфейсам 3,4. Перепрогр структура под конкр решаемые задачи.

В “Сумме” и “Минимаксе” с помощью последов интерфейсов зада-ется коммутация по парал интерф и под каждый конкретный алгоритм система перепрограммируется.