- •1.Процессоры. Иерархия языков вт

- •4.Алу для деления чисел с фиксир(,)

- •8.Управл автоматы с мпу

- •15. Организация модулей пзу

- •19.Синхр способ продкл ву к см

- •24. Общие принципы построения risc-процессоров. Особенности Берклинской архитектуры.

- •32. Процессор Pentium IV

- •34. Последовательный интерфейс intel 8251(усапп)

- •42.ATmega 32

- •48. Понятие интерфейса. Виды арбитража

- •50.Арбитраж по || опросу.

- •20.Асинхр способ продкл ву к см

- •21. Ппи, подключение ву с помощью ппи

- •30.Процессор Intel 80386, 486, Pentium

- •17.Организация динамических модулей дозу

- •18.Покдл модулей дозу к см(прозр рег).Способы регенерации

- •45 Типовые структуры вс(п/я, многопорт озу, гиперкуб)

- •2.Алу для сложения чисел с фиксир (,)

- •3.Алу для * чисел с фикс(,)_методы ускор *.

- •5.Устройтсво для выполнения лог.Опер.Особеннсти арифм с плавающей (,)

- •6.Многофункциональное алу

- •7.Управляющие автоматы с жесткой логикой

- •9.Требования к кодам команди способы кодирования.

- •16.Организация модулей статического озу.

- •22.Организация кэш памяти.

- •23.Организация виртуальной памяти.

- •25.Старнфордсая структура

- •26.Машины упр потоками данных(df-машины)

- •31.Pentium II,Pentium Pro

- •35.Прогр контр прерываний.

- •37.Таймер

- •38.Орг эвм типа ibm pc at

- •46.Архитектура Сммр,Сvмр,См.

- •47.Сm структура.

- •49.Арбитраж по последовательному опросу.

- •44.Типовые структуры вс (Ош,кажд с кажд…)

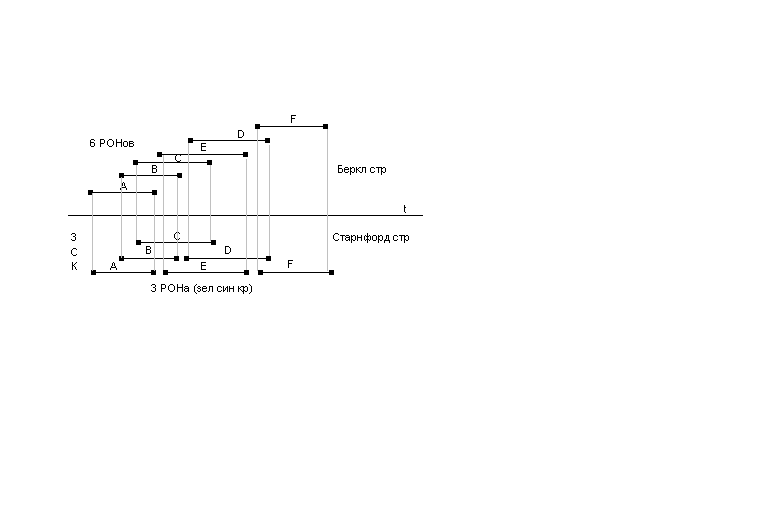

25.Старнфордсая структура

Разработчики ставили первой целью уменьшение аппаратных затрат (РОН) вследствие чего достигается увел такт частоты.

1)Построение оптимизирующего компилятора

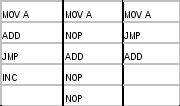

Его функции: а)Предотвращение (уменьшение) числа “ломок” конвейера. Конвейер ломается из-за неготовности результата выполнения предыдущей команды или при наличии команд условного и безусловного переходов. Конвейерная выборка команд дает выигрыш в производительности в основном не линейных участках программ. Чтобы конвейер не ломался компилятор должен загружать пустые команды NOP, более интеллектуальный компилятор должен менять последовательности команд (II) т.к. загр команда в конвейер все равно выполнится.

I II

2)Для оптимизации работы аппаратных ресурсов разработчики компилятора использовали метод окрашенных графов

Использование вышеуказанного подхода позволяет резко сократить число РОНов но увеличивает сложность оптимизир-го компилятор

Достоинства:

Беркл 1)Простота программ-я 2)Min число пересылок инф 3) Min число обращений к внешн ЗУ.

Старн 1)Min аппаратн затраты 2) Max тактовая частота

Недостатки:

Бекрл 1)Большие аппаратн затраты 2) Низкая тактовая частота

Старн 1) Сложность компилятора 2) Сложность прогр-я

Современные RISC проц-ры обычно испоьз от 32 до 128 РОНов. Тактовая частота 100MHz – 40-50 MHz.

26.Машины упр потоками данных(df-машины)

Осн особенность таких машин отсутствие в них счетчика команд.

Машина Массачуссетского технолог ун-та

Команда выполняется тогда когда готова командная ячейка.

УУ- ч/з схему селекции отправляет в процессорный блок те командные ячейки для которых определены операнды. Предпола-гается что все команды выполняются за 1 такт.(1 инт времени)

Использование микропроцессорной машины с применением командных ячеек позволяет распараллеливать исходный алгоритм где команды выполняются по мере готовности операндов (не нужен счетчик команд).

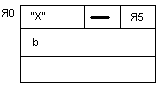

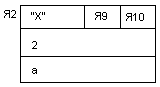

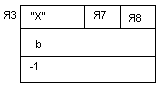

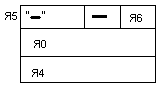

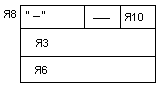

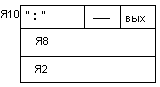

Пример: x1,2=(-b±(b2-4*a*c))/2*a

1

такт Я0 Я1 Я2 Я3

2 такт Я4

3 такт

Я5

такт Я0 Я1 Я2 Я3

2 такт Я4

3 такт

Я5

4 такт Я6 5 такт Я7,Я8 6 такт Я9,Я10

Коэфф распараллеливания Кр=11/6=1,8.

Машина управляемая по запросу- выполняет команды по мере необ

ходимости . Главная машина анализирует исходный алгоритм разбивает его на командные составляющие и поставляет запросы подчиненным машинам на формирование требуемых фрагментов алгоритма. Так же происх распараллеливание но фрагменты алго-ритма по мере выполнения возвращаются в главную машину.

31.Pentium II,Pentium Pro

УРК- устр распред команд.

Процессор имеет суперскалярную архитектуру и на кристалле располагается двухуровневая КЭШ. 16кб КЭШ команд и 16кб КЭШ данных. КЭШ 2-го ур-ня (общая)(128k-2mb). Одновременно работают до5-ти аппаратных ресурса (5 команд может выполн одновременно). Проц имеет 11-ти ступ конвейер т.е. все команды выполняются за 11 тактов. Команда из КЭШ памяти поступает в ДШК, УРК формирует блоки из кодов команд и операндов ктр загружаются в пул команд, ДШ команд из цикла выбирает те команды которые для которых определены операнды и есть свободные аппаратные ресурсы, команды выполн аппаратными ресурсами и возвращаются обратно в пул команд. Блок отката выбирает из пула команд выполненные ком-ды и восстанавливает последовательность выполнения команд в соотв с программой. Результат отправляется в КЭШ данных 1-го уровня.

Процессор относится к разряду машин управляемых потоком данных. Проц имеет несколько напряж питания : вычислительное ядро запитывается напряж-ем 2,3В, микросхема обвязки (внешний уровень) повышенным, мощность потребл достигает 40Вт. Прой имеет встроенный датчик температуры и встроенный АЦП, а также требует внешней системы охлаждения. Потребляемый ток 15-20 А.