- •18.2. Характеристики и параметры логических элементов

- •2. Транзисторно−транзисторная логика (ттл).

- •18.4. Транзисторно−транзисторная логика с диодами Шоттки (ттлш)

- •3. Логика на основе комплементарных ключей на моп-транзисторах (кмоп)

- •4. Шифраторы

- •5. Дешифраторы

- •6. Мультиплексоры

- •7. Демультиплексоры

- •8. Сумматоры

- •9, Вычитатели

- •10, Цифровые компараторы

- •11, Перемножители

- •16,,,,,,,,,Реверсивные счетчики.

- •18,,,,,,,,,,Сдвиговые регистры.

- •25.2. Сдвиговые регистры

- •17,,,,,,,,,,Разновидности регистров. Параллельные регистры.

- •19,,,,,,,,,,Реверсивные регистры.

- •20,,,,,,,,,,,Запоминающие устройства. Разновидности, характеристики.

- •21,,,,,,,,,,Структуры зу.

- •23,,,,,,,,,,,,,Пзу и ппзу.

- •24,,,,,,,,,,,,,,,,,,,,Flash-память.

- •25,,,,,,,,,,,,,,,,,,,Озу типа fram.

- •26.7. Построение плат памяти

- •26,,,,,,,,,,,,,,,,,,,Плис. Общие понятия. Разновидности.

- •27,,,,,,,,,,,,,,,,,,Программируемые логические матрицы (pla).

- •28,,,,,,,,,,,,,,,,Программируемая матричная логика (pal), базовые матричные кристаллы (ga).

- •27.4. Базовые матричные кристаллы (ga)

- •29,,,,,,,,,,,,,,,,,,,,Программируемые вентильные матрицы (fpga). Программируемые коммутируемые матричные блоки (cpld)

- •27.6. Программируемые коммутируемые матричные блоки (cpld)

- •30,,,,,,,,,,,,,,,,,,,,Программируемые аналоговые интегральные схемы (fpaa)

- •31,,,,,,,,,,,,,,Плис типа «система на кристалле» (SoC).

- •32,,,,,,,,,,,,,,Цап. Общие положения. Погрешности цап.

- •28.7. Параметры цап

- •33,,,,,,,,,,,,,,Цап с суммированием токов.

- •34,,,,,,,,,,,,Цап типа r-2r.

- •35,,,,,,,,,,,,,Сегментированные цап.

- •36,,,,,,,,,,,,,,,Цифровые потенциометры. Цап прямого цифрового синтеза.

- •28.6. Цап прямого цифрового синтеза

- •37,,,,,,,,,,,,,,,,,,Ацп. Общие положения. Параметры ацп. Погрешности ацп.

- •38,,,,,,,,,,,,, Разновидности ацп. Параллельные ацп.

- •39,,,,,,,,,,,,,,,Ацп поразрядного уравновешивания.

- •40,,,,,,,,,,,,Конвейерные ацп.

25,,,,,,,,,,,,,,,,,,,Озу типа fram.

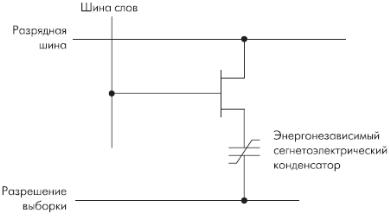

FRAM – оперативное энергонезависимое ЗУ, сочетающее высокое быстродействие и малую потребляемую мощность, присущие ОЗУ, со свойством хранения данных при отсутствии приложенного напряжения.

В сравнении с EEPROM и Flash-памятью время записи данных в ЗУ этого типа и потребляемая мощность намного меньше (менее 70 нс против нескольких миллисекунд), а ресурс по циклам записи намного выше (не менее 1011 против 105…106 циклов для EEPROM).

Сегнетоэлектрическое ЗУ хранит данные не только в виде заряда конденсатора (как в традиционных ОЗУ), но и виде электрической поляризации кристаллической структуры сегнетоэлектрика. Сегнетоэлектрический кристалл имеет два состояния, которые могут соответствовать логическим 0 и 1.

Термин FRAM еще не устоялся. Первые FRAM получили название – ферродинамические ОЗУ. Однако в настоящее время в качестве запоминающих ячеек используется сегнетоэлектрик и сейчас FRAM часто называют сегнетоэлектрическим ОЗУ.

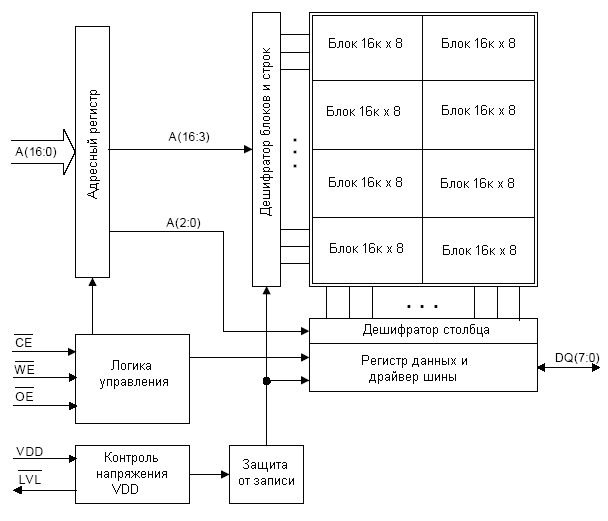

FM20L08 – энергонезависимая память с организацией 128К×8, которая считывается и записывается подобно стандартному статическому ОЗУ. Сохранность данных обеспечивается в течение 10 лет, при этом, нет необходимости задумываться о надежности хранения данных (неограниченная износостойкость), упрощается проектирование системы и исключается ряд недостатков альтернативного решения энергонезависимой памяти на основе статического ОЗУ с резервным батарейным питанием. Быстрота записи и неограниченное количество циклов перезаписи делают FRAM лидером по отношению к другим типам энергонезависимой памяти.

а)

26.7. Построение плат памяти

Емкость микросхемы памяти оценивается числом бит (или байт) информации, которую она может хранить. Это число соответствует количеству комбинаций, которое можно выставить на ее адресных входах. В большинстве случаев емкость одной микросхемы оказывается недостаточной, так что приходится использовать несколько микросхем.

Наименование вывода |

Описание |

A(16:0) |

Адресные входы |

|

Вход выбора микросхемы |

|

Чтение |

|

Запись |

DQ(7:0) |

Линии данных |

|

Выход схемы контроля напряжения |

VDD |

Напряжение питания 3.3В |

VSS |

Общий питания |

Для построения

памяти 1кБ применены 2 ИМС по

![]() разрядных слов каждая. В зависимости

от структуры шины конкретной МП системы,

примененных схем памяти для

разрядных слов каждая. В зависимости

от структуры шины конкретной МП системы,

примененных схем памяти для

построения реальной системы (платы памяти) требуется дополнительные ИМС.

А0 – А15 – адресные линии памяти.

А0 – А9 – внутренняя шина (внутренняя линия адреса).

D0 – D7 – двунаправленная линия, составляющая шину данных.

![]() – сигнал для вывода

данных из памяти на шину данных МП

системы.

– сигнал для вывода

данных из памяти на шину данных МП

системы.

![]() – сигнал для записи

данных из МП в память.

– сигнал для записи

данных из МП в память.

В небольших схемах

памяти буферы могут не использоваться.

А0 – А8

–

адресная шина с буферами непосредственно

на ИМС памяти. А9

служит для выбора одной из двух ИМС

памяти. Следовательно, адресуемая ячейка

находится в одной из двух 512 битовых

областей памяти. А9

поступает через схему «ИЛИ» на одну из

ИМС памяти, а

![]() через вторую схему «ИЛИ» на вторую схему

памяти, следовательно, когда выбрана

одна из ИМС, доступ ко второй закрыт.

через вторую схему «ИЛИ» на вторую схему

памяти, следовательно, когда выбрана

одна из ИМС, доступ ко второй закрыт.

Адреса А10 – А15 сравниваются с набором данных адресов, набранного посредством тумблеров S1 – S6. Выходной сигнал схемы сравнения содержит информацию о том, имеет ли место обращение к данной памяти. Если адресные сигналы совпадают с адресом полученным набором тумблеров, то на выходе схемы сравнения формируется сигнал логического «0», который разрешает выбор кристалла на данной плате памяти. Если не совпадают сигналы А10 – А15 с S1 – S6, то на выходе схемы сравнения формируется сигнал логической «1», запрещающий обращение к данной плате памяти. Если на линиях S1 – S6 все «0», то плата памяти будет реагировать на адреса от 0 до 1 кБ, если S1 = 1, S2 – S6 = 0 – на адреса 1кБ – 2кБ и т.д. Следовательно, наращивание памяти возможно до 64 кБ с помощью тумблеров S1 – S6.

Линии D0 – D7 связаны с кристаллами с помощью шинных приемопередатчиков (формирователей). Эти формирователи выполняют 2 функции: обеспечивают ввод (запись) данных и вывод (считывание) при соответствующих сигналах «чтение» и «запись».