- •?. Ттлш (транзистор Шотки)

- •5. Дешифраторы.

- •6. Мультиплексор

- •8. Сумматоры

- •10. Цифорвые компараторы.

- •14. Д и т триггеры

- •15. Счётчики

- •16. Реверсивные счетчики.

- •17. Разновидности регистров. Параллельные регистры.

- •18. Регистры сдвига.

- •20. Запоминающие устройства.

- •21. Струкруры зу.

- •23. Пзу и ппзу

- •24. Flash память

- •25. Озу типа fram

- •26. Плис.

- •28. Программируемая матричная логика

- •28. Базовый матричный кристалл

- •29. Программируемые коммутируемые матричные блоки

- •31 Плис на кристалле

- •32. Цап. Общие положения.

- •33. Цап с суммирование токов

- •35. Сегментированный цап.

- •36. Цифровые потенциометры. Цап прямого цифрового синтеза

- •37. Ацп. Общие положения. Параметры ацп. Погрешности ацп.

- •38.Параллельные ацп

- •39. Ацп поразрядного уравновешивания.

- •40. Конвеерные ацп

- •41. Дельта сигма ацп

1. Цифровой сигнал — сигнал, который может иметь только два состояния — «высокое» и «низкое», например, представляет собой последовательность нулей и единиц. Цифровой сигнал сложнее передавать на большие расстояния, чем аналоговый сигнал, поэтому его предварительно модулируют на стороне передатчика, и демодулируют на стороне приёмника информации. Использование в цифровых системах алгоритмов проверки и восстановления цифровой информации позволяет существенно увеличить надёжность передачи информации.

К основным статическим характеристикам элементов ЭВМ относятся входная, выходная и амплитудная передаточная (АПХ) характеристики. В статических характеристиках отсутствует время t в качестве аргумента функции.

К статическим параметрам относятся входные и выходные напряжения логических 0 и 1, входные и выходные токи логических 0 и 1. Один уровень напряжения, например высокий, в двоичных элементах принимается за единичный, а другой, например низкий— за нулевой.

Кроме того, к статическим параметрам относятся логический перепад и средняя (статическая) потребляемая мощность.

ЛЭ должны обладать помехоустойчивостью, т. е. нечувствительностью к действию помех определенной величины. Статическую помехоустойчивость определяют по АПХ.

2. Транзисторно-транзисторная логика (ТТЛ) — способ преобразования дискретной информации (в частности, выполнения логических операций) с помощью электронных устройств, построенных на основе биполярных транзисторов и резисторов. Название транзисторно-транзисторный возникло из-за того, что транзисторы используются как для выполнения логических функций (например, И, ИЛИ), так и для усиления выходного сигнала (в отличии от резисторно-транзисторной и диодно-транзисторной логики). ТТЛ получила широкое распространение и применяется в компьютерах, АСУТП, электронных музыкальных инструментах, а также в контрольно-измерительной аппаратуре. Благодаря широкому распространению ТТЛ входные и выходные цепи электронного оборудования часто выполняются совместимыми по электрическим характеристикам с ТТЛ.

ТТЛ-логика (как и ТТЛШ) является прямым наследником ДТЛ и использует тот же принцип действия. Причина появления ТТЛ - это появление интегральных микросхем (вместо гибридных). ТТЛ-транзистор (в отличии от обычного) имеет множество эмиттеров. Эти эмиттеры выполняют роль входных диодов (если сравнивать с ДТЛ), на базу подаётся опорное напряжение единицы которое сравнивается диодами с входным, коллектор транзистора - корпус (реже - питание).

ТТЛШ-логика отличается от ТТЛ наличием диодов Шоттки в цепях база коллектор, что исключает насыщение транзистора, а также наличием демпфирующих диодов Шоттки на входах (редко на выходах) для подавления импульсных помех, образующихся из-за не синусоидальной формы сигнала в логических цепях.

?. Ттлш (транзистор Шотки)

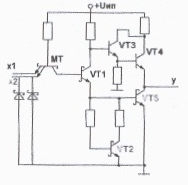

Элементы ТТЛ с диодами и транзисторами Шотки широко используются в качестве элементной базы быстродействующих цифровых микросхем. Вместо обычных транзисторов в этих элементах используется транзистор Шотки, параллельно его коллекторному переходу включен диод Шоттки(ДШ) |

|

Для контакта Шотки обычно используются металлы А1 или Pt Si, которые обеспечивают напряжение отпирания диода U*ш≈0,4 .. 0,5 В<U*. В случае открытого транзистора ДШ из-за действия ООС по напряжению препятствует снижению напр м/у К и Э ниже 0,3В => транзистор переключается в 3 раза быстрее. ТТЛШ серии – 530, 531, 555. Маломощный ТТЛШ по быстродействию эквивалентно стандартным ТТЛ.

|

|

Основные параметры и характеристики те же что и в ТТЛ, но быстродействие у ТТЛШ в 3-4 раза лучше.

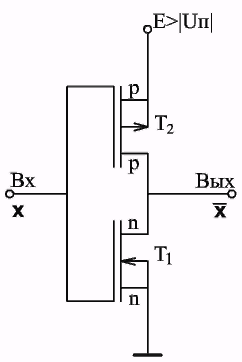

3. КМОП – комплементарная МОП, предполагает одновременное использование МОП транзисторов и с p- и с n-проводимостью. Второй закрытый транзистор – резистор с большим R и не влияет на уровень выходных сигналов. В статике мощность потребления = 0, а в динамике = 2U2ипснf (зависимость от f). Работа схемы не зависит от уровня Uип(3-15В). Достоинства: высокая помехоустойчивость, допустимый уровень помех около 40-45% от Uип. Недостатки: низкое быстродействие (около 50 нс). Серия К564, К561, К764, К765. Большие возможности. Коэффициент нагрузочной способности N=15-20.

Реализация функции НЕ

В качестве нагрузочного транзистора Т2 используется р - канальный транзистор, а в качестве управляющего Т1, с каналом n -типа. КМОП инвертор работает на полож. логике. Т2 всегда закрыт по току. Мощность КМОП - инвертора меньше нем МОП - инвертора, т.е. от источника напряжения почта не происходит потр. энергии. |

Реализация функции ИЛИ - НЕ

Комплементарные пары: Т1 - Т3 , Т2 - Т4. Функцию ИЛИ реализует параллельное соединение n-канапьных транзисторов. Если хотя бы один из транзисторов в последовательной цепочке Тз-Т4 закрыт, то на выходе ноль. |

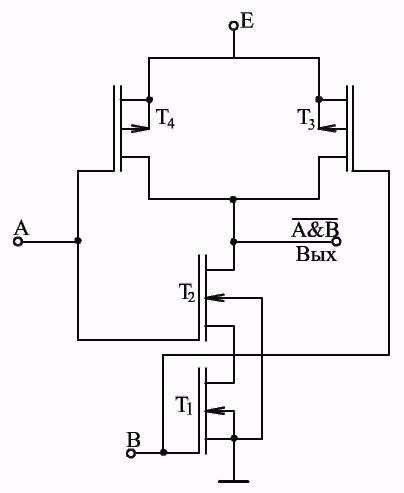

Реализация функции И - НЕ

Комплементарные пары: Т1 - Т3 , Т2 - Т4. Функцию И реализует последовательное соединение n-канальных транзисторов. Если хотя бы один из транзисторов в параллельном соединении Тз-Т4 открыт, то на выходе единица. |

4. Шифратор выполняет функцию, обратную дешифратору. Классический шифратор имеет m входов и n выходов, и при подаче сигнала на один из входов (обязательно на один, и не более) на выходе появляется двоичный код номера возбужденного входа. Число входов и выходов такого шифратора связано соотношением m=2n. Шифратор можно использовать, например, для отображения в виде двоичного кода номера нажатой кнопки или положения многозначного переключателя.

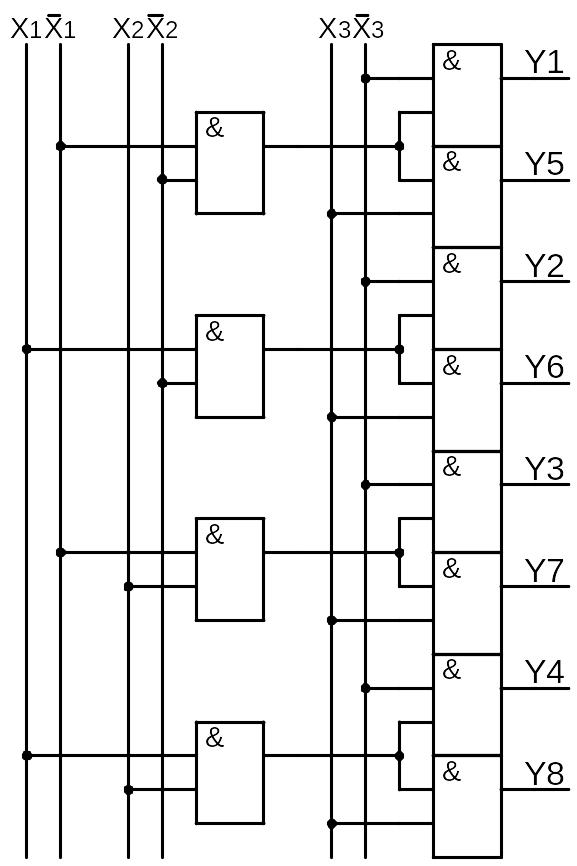

5. Дешифраторы.

Дешифратор – Узел ЭВМ осуществляющий микроперацию преобразования входного n-разрядного числа в выходной сигнал на одной из m выходных линий, где m=2^n Деш-р. – узел комбинационного типа. Если Деш-р все комбинации полностью, то он называется полным.

Три вида дешифраторов: Линейные, Пирамидальные, Многоступенчатые

|

Параметры дешифраторов: - Время дешифрации - Кол-во используемых логич. элм-ов tдеш = t&(n вх) V = 2^n - для n-входовых эл-ов V*= 2^n (n-1) – для 2-х входовых эл-ов Схема линейного дешифратора. |

|

tдеш = t&(n-1) V* = 2(2n-2) Удобно строится на 2-х входовых элементах. Основные достоинства: использование только двухвходных элементов. Недостаток: низкое быстродействие.

|