- •Розділ 1. Елементи алгебри-логіки

- •1:1 Релейні та логічні елементи. Їх характерні особливості. Узагальнена схема та особливості релейного пристрою.

- •1:2 Визначення логічної змінної та логічної функції. Таблиця істинності.

- •1:3 Конституенти одиниці та нуля. Основні логічні функції.

- •1:4 Основні закони алгебри-логіки (без доведення).

- •1:5 Диз’юнктивна нормальна форма та довершена диз’юнктивна нормальна форма. Їх властивості.

- •1:6 Кон’юнктивна нормальна форма та довершена кон’юнктивна нормальна форма. Їх властивості.

- •1:7 Функції однієї змінної.

- •Розділ 2. Синтез однотактних схем

- •2.1 Алгоритм синтезу однотактних схем за допомогою таблиць істинності і карт Карно.

- •2.3 Синтез схеми перетворення коду Грея у двійковий код

- •2.4 Синтез схеми перетворення двійкового коду у двійково-десятковий.

- •2.5 Застосування постійних запам’ятовуючих пристроїв для реалізації комбінаційних функцій.

- •Розділ 3. Синтез багатотактних схем

- •3.1 Таблиця переходів, як змістовний опис роботи багатотактної схеми.

- •3.2 Послідовність синтезу багатотактної схеми на основі таблиць переходів і карт Карно.

- •3.5 Змагання в безконтактних схемах і способи запобігання їм.

- •3.6 Особливості синтезу схем методом таблиць переходів і карт Карно з технологічними затримками.

- •3.7 Схема і принцип дії тактового розподільника

- •3.8 Математичний опис роботи схеми керування на основі тактового розподільника.

- •3.9 Алгоритм синтезу схеми керування на основі тактового розподільника.

- •3.10 Циклограми, як графічний метод зображення умов роботи схеми. Основні поняття та визначення.

- •3.11 Алгоритм складання рівняння для вихідного елемента на основі методу циклограм.

- •3.12 Сутність та приклад першої перевірки реалізованості циклограми.

- •3.13 Сутність та приклад другої перевірки реалізованості циклограми.

- •3.15 Уведення самоблокування для циклограм, що мають кілька періодів вмикання.

- •3.17 Загальні відомості про тригери. Подання умов роботи схеми за допомогою графу переходів. Основні поняття та визначення.

- •3.18 Послідовність синтезу багатотактних схем на основі rs-тригерів.

- •3.19 Запис умов вмикання та вимикання тригерів за відомим графом переходів.

- •3.20 Особливості синтезу синхронних багатотактних багатовходових схем.

- •3.21 Особливості синтезу синхронних одновходових схем.

- •3.22 Будова і принцип дії мультиплексора-селектора.

Розділ 2. Синтез однотактних схем

2.1 Алгоритм синтезу однотактних схем за допомогою таблиць істинності і карт Карно.

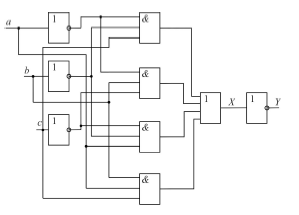

Синтез однотактної схеми можна виконати у такій послідовності:

1) за заданими умовами роботи скласти таблицю істинності;

2) за таблицею істинності записати логічні формули для вихідних змін-

них у ДДНФ або у ДКНФ;

3) якщо є можливість, записані функції мінімізувати.

Приклад 1. Виконати логічний синтез схеми, виходячи з таких умов

роботи: схема має три вхідні сигнали а,b,с і два вихідні Х і Y; вихідний

сигнал Х = 1, якщо непарна кількість вхідних сигналів дорівнює одиниці;

вихідний сигнал Y = 1, якщо парна кількість вхідних сигналів дорівнює

одиниці (нуль вважати парним числом).

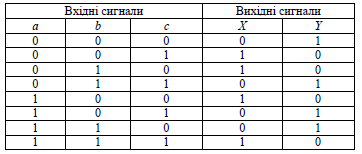

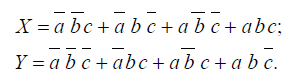

За заданими умовами роботи складаємо таблицю істинності

Якої:

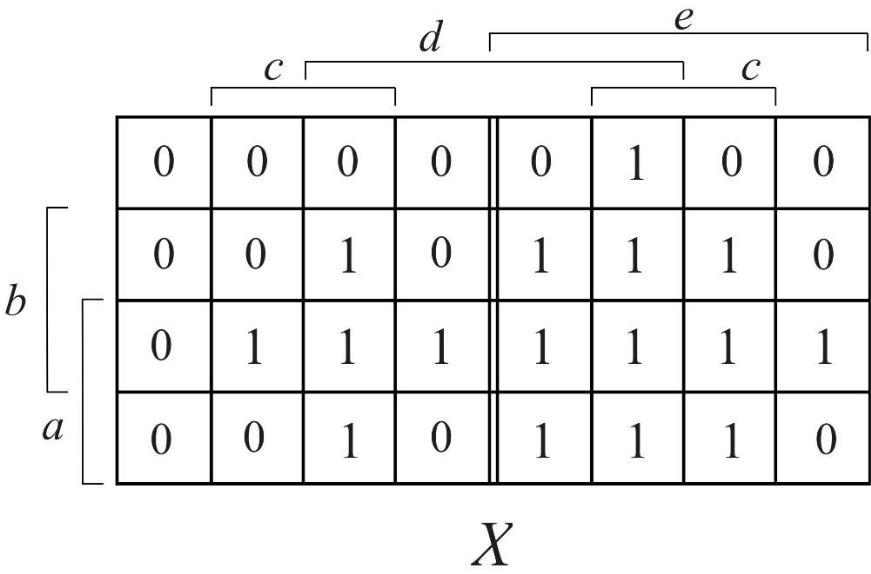

Приклад 2. Схема має п’ять вхідних сигналів а, b, c, d, е і один

вихідний Х. Вихідний сигнал реалізує принцип вибору за більшістю, тобто

він дорівнює тому значенню, якого набуває більшість вхідних сигналів.

Виконати логічний синтез схеми

Карта Карно для змінної Х

Побудуємо карту Карно для п’ятьох змінних і запишемо одиниці у тих

клітинках карти, для яких одночасно три, чотири або п’ять змінних

дорівнюють одиниці (рис. 2.2). Виконавши мінімізацію функції Х за картою

Карно, отримаємо

X=cde+bce+bcd+bde+abe+abd+abc+acd+ace+ade.

2.2 Синтез однотактних схем на суматорах.

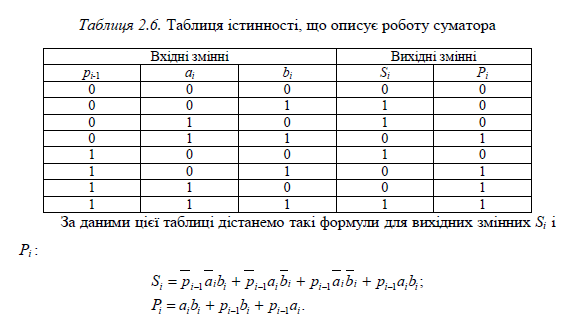

Суматорами називають пристрої, які виконують операцію

арифметичного підсумовування кодів чисел. Значення вихідних сигналів

суматора визначається тільки значеннями вхідних сигналів у певний момент

часу. Тому робота суматора повністю описується таблицею істинності, за

якою можна визначити логічні формули для побудови схеми суматора.

Незалежно від системи числення, у якій подано коди чисел, у кожному

розряді виконується додавання трьох цифр: цифри і-го розряду першого

доданка, цифри і-го розряду другого доданка і цифри перенесення із

сусіднього молодшого розряду. В результаті додавання отримують цифри

суми для цього розряду і перенесення в наступний розряд. Отже, суматор –

це комбінаційна схема, яка має три вхідні та два вихідні сигнали. Уведемо

такі позначення: аі, bі – доданки; рі-1– сигнал перенесення з попереднього

розряду; Sі – сума; Рі – сигнал перенесення в наступний розряд. Тоді,

виходячи з правил підсумовування двійкових чисел, отримаємо таблицю

істинності (табл. 2.6).

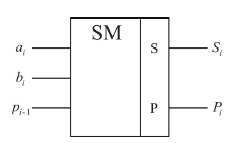

Умовне зображення суматора

2.3 Синтез схеми перетворення коду Грея у двійковий код

Код Грея

характеризується тим, що послідовне збільшення або зменшення числа на

одиницю призводить до зміни цифри тільки в одному розряді. Код Грея

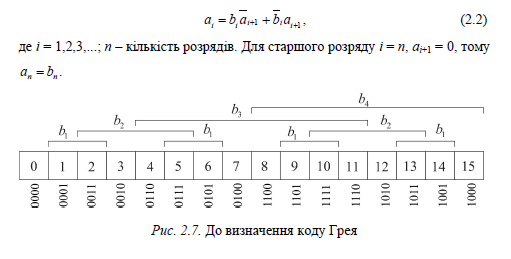

можна дістати, використавши рис. 2.7, побудований за типом карти Карно.

Вхідними сигналами є розряди коду Грея (b4 – старший розряд, b1 –

молодший). У клітинках карти записано десяткові цифри, зображення яких у

коді Грея безпосередньо випливає з рисунка: значення цифри у відповідному

розряді коду Грея дорівнює одиниці, якщо проти клітинки над дужкою стоїть

позначення сигналу цього розряду, і дорівнює нулеві, якщо дужки з

позначенням сигналу немає. Наприклад, число 7 кодується набором сигналів

0100, 8 –-1100, 9 – 1101 тощо.

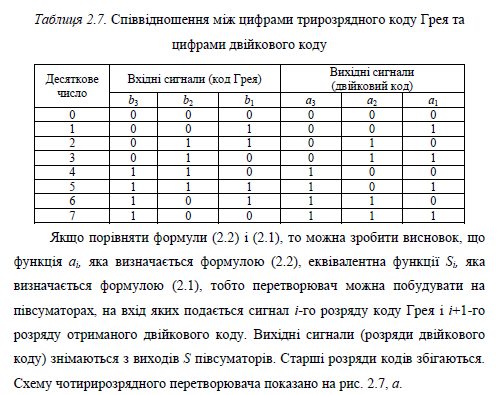

Для визначення формул, за якими можна побудувати перетворювач,

складемо таблицю істинності (табл. 2.7). Таблицю складено для

трирозрядних кодів, але вона дає змогу отримати загальну формулу для

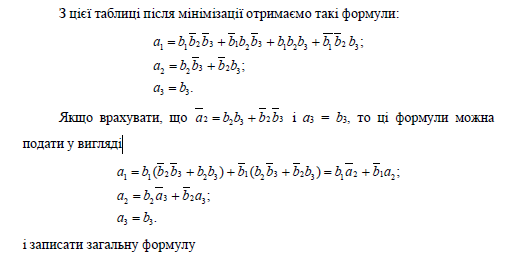

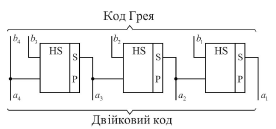

побудови перетворювача з будь-якою кількістю розрядів.