- •161 “Електротехніка, електроніка і мікропроцесорна техніка”

- •Херсон – 2013 р.

- •Лекція 1. Вступ. Основні поняття і співвідношення в електричних колах. План

- •Зміст і структура дисципліни.

- •Прості кола постійного струму. Електричні схеми, елементи схем.

- •Закон Ома для ділянки кола.

- •Напруга на клемах джерела.

- •Енергетичні співвідношення. Закон Джоуля–Ленца. Баланс потужностей.

- •Лекція 2. Режими роботи електричних кіл. Розрахунок кіл постійного струму. План

- •Режими роботи електричних кіл.

- •Режими холостого ходу і короткого замикання.

- •Точки характерних режимів на зовнішній характеристиці джерела.

- •Джерело ерс та джерело струму.

- •Розрахунок кіл постійного струму. Способи з’єднання споживачів

- •З’єднання елементів живлення.

- •Послідовне з’єднання елементів.

- •Паралельне з’єднання елементів.

- •Змішане з’єднання елементів.

- •Розрахунок простих кіл електричного струму.

- •Розрахунок складних кіл. Закони Кірхгофа.

- •Перетворення трикутника опорів в еквівалентну зірку.

- •Лекція 3. Методи розрахунку складних електричних кіл. План

- •Розрахунок складних кіл постійного струму. Використання законів Кірхгофа для розрахунку складних кіл.

- •Метод суперпозиції.

- •Метод контурних струмів.

- •Метод вузлових напруг.

- •Зауваження щодо аналогій з фізичними системами іншої природи.

- •Метод еквівалентного генератора.

- •Опір r схеми визначається методом еквівалентних перетворень схеми до загального опору відносно клем a, b при відключеному навантаженні і заморочених внутрішніх ерс.

- •Лекція 4. Нелінійні опори та перехідні процеси. План

- •Нелінійні опори в колах постійного струму. Основні поняття.

- •Графічний метод розрахунку простих кіл з нелінійними опорами.

- •Коло з двома послідовними нелінійними опорами.

- •Коло з двома паралельними нелінійними опорами.

- •Змішане з’єднання нелінійних опорів

- •Приклад розрахунку схеми стабілізації струму.

- •Перехідні процеси в електричних колах Закони комутації

- •Загальні принципи аналізу перехідних процесів

- •Лекція 5. Основні поняття змінного струму План

- •Змінний струм Передмова

- •Основні поняття

- •Діюче (ефективне, середньоквадратичне) значення.

- •Середнє значення змінного струму.

- •Зображення синусоїдальних величин векторами Векторна діаграма

- •Елементи кіл змінного струму

- •Активний опір на змінному струмі.

- •Індуктивність на змінному струмі. Котушка індуктивності.

- •Котушка індуктивності на змінному струмі

- •Конденсатор на змінному струмі.

- •Конденсатор на змінному струмі

- •Символічний метод

- •Нагадування про комплексні числа Форми запису комплексних чисел

- •Дії над комплексними числами

- •Уявлення параметрів електричного змінного струму через комплексні числа

- •Лекція 6. Аналіз кіл синусоїдального струму. План

- •Розрахунок кіл синусоїдального струму. Закони Кірхгофа

- •Опір і провідність в комплексній формі.

- •Активна, реактивна і повна потужність.

- •Розрахунок складних кіл змінного струму.

- •Значення cos.

- •Лекція 7. Електричні коливання. План

- •Аналіз електричного стану розгалужених кіл. Коливальний контур.

- •Резонанс напруг.

- •Резонанс струмів.

- •Лекція 8. Трифазні кола. План

- •Трифазна система ерс. Передмова

- •Устрій генератора трифазного струму

- •Незв’язана система трифазних струмів

- •Основні схеми з’єднання в трифазних колах з’єднання за схемою «зірка»

- •Потужність трифазного кола.

- •Розрахунок трифазного кола. Трипровідна система із симетричним навантаженням.

- •Чотирипровідна система при несиметричному навантаженні.

- •З’єднання за схемою “трикутник” з’єднання споживачів за схемою “трикутник”.

- •З’єднання обмоток генератора за схемою «трикутник».

- •З’єднання «зірка – трикутник»

- •З’єднання «трикутник – трикутник»

- •З’єднання «трикутник – зірка»

- •Устрій однофазного трансформатора

- •Режими роботи трансформатора

- •Холостий хід трансформатора

- •Навантажений режим трансформатора. Робота трансформатора.

- •Рівняння намагнічуючих сил трансформатора.

- •Векторна діаграма навантаженого трансформатора.

- •Схеми заміщення.

- •Лекція 10. Особливості використання трансформаторів.

- •Зміна вторинної напруги трансформатора

- •Трифазні трансформатори

- •Устрій трифазного трансформатора

- •Групи з'єднання обмоток трифазного трансформатора.

- •Навантажувальна здатність трансформатора Номінальні параметри трансформатора

- •Дослід короткого замикання

- •Дослід холостого ходу

- •Коефіцієнт корисної дії (к.К.Д.) трансформатора.

- •Автотрансформатори

- •Лекція 11. Асинхронні електричні машини.

- •Принцип дії асинхронної машини

- •Магнітне поле, що обертається

- •Режими роботи асинхронної машини

- •Конструкція ротора

- •Механічні характеристики асинхронного двигуна.

- •Баланс активних потужностей асинхронного двигуна. Баланс активних потужностей асинхронного двигуна можна уявити таким рівнянням

- •Асинхронний лінійний двигун (лад).

- •Однофазний асинхронний двигун.

- •Лекція 12. Синхронні генератори.

- •ОтриманнясинусоїдальноїЕрс.

- •Багатополюсні генератори.

- •Робочий процес синхронного генератора Холостий хід.

- •Реакція якоря.

- •Зовнішня і регулювальна характеристики.

- •Синхронний двигун

- •Принцип роботи синхронного двигуна.

- •Лекція 13. Машини постійного струму. План

- •Машини постійного струму.

- •Устрій та принцип дії генератора постійного струму

- •Магнітна система.

- •Ерс генератора.

- •Збудження генератора.

- •Генератор з паралельним збудженням.

- •Реакція якоря.

- •Комутація.

- •Зовнішня характеристика.

- •Виникнення електромагнітного обертаючого моменту.

- •Лекція 14. Вступ до електроніки. Напівпровідники.

- •Вступ до розділу «Електроніка».

- •Електричні властивості напівпровідників. Уявлення про основи зонної теорії твердого тіла.

- •Власна провідність.

- •Домішкова провідність.

- •Лекція 15. Використання властивостей електронно-діркового переходу.

- •Напівпровідниковий діод і його застосування. Напівпровідниковий діод

- •Спрямляючі діоди

- •Схеми спрямовувачів.

- •Стабілітрони.

- •Варикап.

- •Тунельний та інші види діодів.

- •Лекція 16. Транзистори.

- •Класи транзисторів.

- •Устрій та принцип дії біполярного транзистора.

- •Режими роботи біполярного транзистора.

- •Способи включення та характеристики схем включення.

- •Статичні і динамічні характеристики схем включення.

- •Хрест-характеристика транзистора

- •Лекція 17.Підсилювачі.

- •Підсилювачі.

- •Характеристики підсилювачів

- •Зворотний зв'язок.

- •Електронний генератор синусоїдальних електричних коливань

- •Лекція 18. Мп – нові масові засоби цифрової техніки

- • Вступ до модуля “Мікропроцесорна техніка”.

- •Вступ до модуля “Мікропроцесорна техніка”.

- •Уявлення про інтегральні схеми

- •Уявлення про мікропроцесорні засоби

- •Типова структура мікропроцесорного пристрою

- •Лекція 19. Арифметичні основи мікропроцесорних систем.

- •Загальні відомості про уявлення інформації в мп-системах

- •Додаткова інформація

- •Кодування чисел в мп-системах

- •Лекція 20. Логічні основи мп-систем.

- •Логічні операції

- •Логічні елементи мп-систем

- •За способом кодування двійкових змінних електронними сигналами електронні елементи можуть бути імпульсними, потенціальними, імпульсно-потенціальними, фазовими.

- •Лекція 21. Схемна реалізація логічних елементів.

- • Схемна реалізація логічних функцій на прикладі функцій “не”, “і”, “або”, 3і–не”, “3або–не” та ін.

- •Лекція 22. Тригери.

- •Типи тригерів за способом функціонування.

- •Синхронний однотактний rs–тригер.

- •Синхронний двотактний rs–тригер.

- •Лекція 23. Регістри.

- •Регістри прийому і передачі інформації.

- •Приклади схемної реалізації зсуваючого регістру

- •Лекція 24. Виконання порозрядних логічних операцій при передачі інформації між регістрами.

- •Виконання порозрядних операцій «логічне додавання», «логічне множення».

- •Виконання порозрядної операції «складання за mod 2».

- •Лекція 25 Лічильники.

- •Лічильник як вузол мп-системи. Призначення та класифікація

- •Лічильник з безпосередніми зв’язками з послідовним переносом.

- •Лічильник з паралельним переносом.

- •Реверсивний лічильник з послідовним переносом.

- •Лекція 26. Схеми дешифраторів.

- •Дешифратори. Класифікація.

- •Лекція 27.Шифратори, мультиплексори та демультиплексори.

- •Шифратори і перетворювачі кодів

- •Мультиплексори

- •Демультиплексор

- •Лекція 28.Суматор.

- •Суматор як вузол мп-системи. Призначення та класифікація.

- •Однорозрядний комбінаційний суматор.

- •Однорозрядний накопичуючий суматор.

- •Багаторозрядні суматори

- •Лекція 29. Пам’ять мікропроцесорних систем.

- •Запам’ятовуючі пристрої мікропроцесорних систем. Оперативні запам’ятовуючі пристрої.

- •Запам’ятовуючі пристрої мікропроцесорних систем

- •Оперативні запам’ятовуючі пристрої

- •Постійні запам’ятовуючі пристрої

- •Лекція 30. Мікропроцесор.

- •Типова структура мікропроцесора.

- •Основні сигнали процесора.

- •А0а15 – виводи мп, які приєднуються до ша мп-системи;

- •D0d7 – двонапрямлені виводи мп, які приєднуються до шд мп-системи;

- •Лекція 31. Мікропроцесорні системи.

- •Особливості побудови мп-систем

- •Мікропроцесорні засоби в системах керування

- •Лекція 32. Перетворювачі сигналів.

- •Принцип перетворення напруги в цифровий код.

- •Аналого-цифрові перетворювачі (ацп).

- •Перетворювачі напруги в код.

- •Перетворювачі кута повороту в код.

- •Цифрово-аналогові перетворювачі.

- •Перетворювач коду в напругу.

- •Перетворювач коду в кут повороту.

- •Література

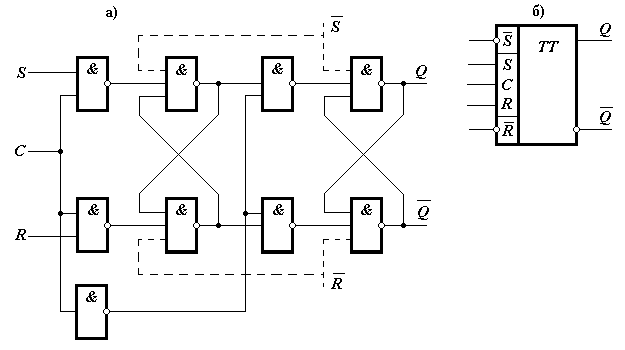

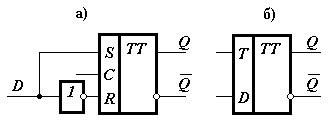

Синхронний двотактний rs–тригер.

Двотактний

RS–тригер

на елементах І–НЕ:

а)

– схема двотактного RS–тригера;

б) – умовне графічне позначення.

При

передачі інформації між тригерами, яка

здійснюється за спільним синхросигналом,

важливо, щоб інформація в наступний в

ланцюгу тригерів елемент була передана

до надходження іншої інформації з

попереднього елемента. Короткочасну

затримку інформації при передачі

забезпечує двотактний принцип обміну

інформацією. Схема тригера, побудованого

за цим принципом, наведена на рис. (а).

Вона складається з двох однотактних

RS–тригерів та інвертора в колі

синхронізації. При надходженні на вхід

RS–тригера синхроімпульсу С = 1

вхідна інформація заноситься тільки

в перший однотактний RS–тригер, а другий

тригер при цьому буде зберігати

інформацію, що відноситься до попереднього

періоду представлення. По закінченню

дії імпульсу синхронізації (коли С

= 0,

а ![]() =

1) перший RS–тригер перейде в режим

зберігання, а другий перепише з нього

нове значення стану. На відміну від

однотактних тригерів, які змінюють

значення вихідного сигналу під

час дії

синхроімпульсу, двотактний тригер

змінить свій стан тільки після

закінчення дії

імпульсу

синхронізації. Тому з двотактних

тригерів можна будувати схеми, що мають

зв’язки між виходами одних тригерів

і синхронними входами інших.

=

1) перший RS–тригер перейде в режим

зберігання, а другий перепише з нього

нове значення стану. На відміну від

однотактних тригерів, які змінюють

значення вихідного сигналу під

час дії

синхроімпульсу, двотактний тригер

змінить свій стан тільки після

закінчення дії

імпульсу

синхронізації. Тому з двотактних

тригерів можна будувати схеми, що мають

зв’язки між виходами одних тригерів

і синхронними входами інших.

Для

встановлення тригера в стан 0 або 1 без

використання синхроімпульсів в схему

введені додаткові входи ![]() і

і

![]() несинхронізованого

встановлення. Зв’язки з цими входами

показані на рис. а

пунктиром.

несинхронізованого

встановлення. Зв’язки з цими входами

показані на рис. а

пунктиром.

Схеми RS–тригерів складають основу для побудови інших тригерних схем типу T–, D– і JK–тригерів.

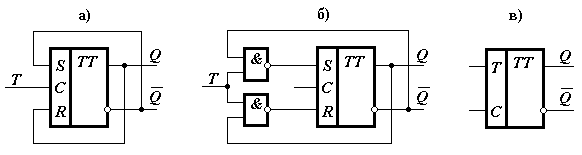

Т–тригер.

Це тригер з лічильним входом (однорозрядний лічильник). Він може бути побудований з використанням двотактного синхронного RS–тригера. Т–тригер реалізує функцію виду

![]()

тобто одиничний вхідний сигнал Т повинен міняти стан тригера на протилежний, а нульовий – залишати стан тригера без змін.

Схеми Т–тригера:

а) – схема двотактного несинхронного Т–тригера на основі двотактного RS–тригера; б) – схема синхронного двотактного Т–тригера; в) – умовне графічне позначення двотактного синхронного Т–тригера.

Схема двотактного несинхронного Т–тригера, утвореного з RS–тригера, наведена на рис. а. В цій схемі надходження сигналу Т = 1 на вхід С призводить до запису в двотактний RS–тригер стану, протилежного попередньому. Сигнал на виході тригера зміниться тільки після завершення дії сигналу Т = 1, що виключає виникнення генерації в схемі із зворотнім зв’язком.

На рис. б представлена схема синхронного двотактного Т–тригера, а на рис. в – його умовне позначення. Одиничний вхідний сигнал Т уявляється високою напругою при С = 1. Запис інформації в тригер здійснюється при С = 1, причому зміна стану, як звичайно в двотактних тригерах, відбувається після закінчення дії імпульсу синхронізації С = 1. При Т = 1 стан тригера змінюється на протилежний, а при Т = 0 – не змінюється.

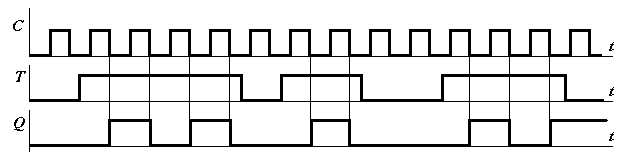

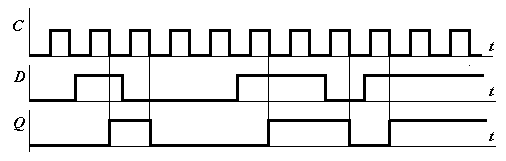

Часова діаграма роботи Т–тригера :

Як видно з часової діаграми Т–тригер можна використовувати як асинхронний тригер з лічильним входом, якщо на інформаційний вхід Т подати константу 1, а логічну змінну подавати на вхід С.

Синхронні і асинхронні тригери з лічильним входом застосовуються в цифрових пристроях і мікропроцесорних системах для побудови схем лічильників.

D–тригер.

D–тригер

на основі двотактного RS–тригера:

а) – функціональна

схема; б) – умовне графічне позначення.

Одним з інтегральних тригерів, що має широке використання, є D–тригер з одним входом. Найпростіший варіант побудови двотактного D–тригера показаний на рис. а. У момент дискретного часу t під дією синхросигналу інформація, що надходить на вхід D, приймається в RS–тригер, але на виході Q з’являється із затримкою на час дії синхросигналу в момент часу t +1 – Q(t + 1) = D(t). Отже D–тригер може використовуватись як синхронний елемент затримки на один такт (на час дії одного синхросигналу). Часова діаграма роботи D–тригера:

D–тригер відповідає RS–тригеру, що працює тільки в режимі встановлення, тобто або з комбінаціями сигналів R = 1 і S = 0, або з комбінаціями сигналів R = 0 і S = 1. Для організації зберігання інформації використовується вхід С (режим зберігання С = 0).

JK–тригер.

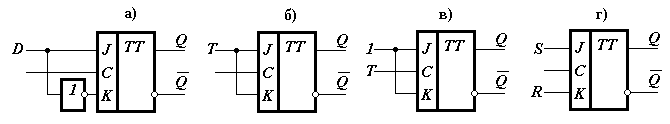

Розповсюдженим типом тригера в системах інтегральних логічних елементів є універсальний двотактний JK–тригер а) – схемна реалізація; б) – умовне позначення:

Входи

J

і

K

відповідають входам S

і

R RS–тригера,

тобто сигнал 1 на вході J

встановлює тригер в стан 1, а сигнал 1

на вході K

встановлює його в стан 0 незалежно від

попереднього стану. Але на відміну від

RS–тригера в JK–тригері сигнали 1 можуть

одночасно прийти на входи J

і

K.

При цьому стан тригера завжди буде

змінюватись на протилежний, тобто при

J

= K

= 1 схема поводить себе як Т–тригер з

лічильним входом. Сигнали J

і

K

можуть бути результатом кон’юнкції

кількох сигналів J

= J1

J2

J3

і

K

=

K1

K2

K3.

Крім того тригер має входи несинхронізованого

встановлення ![]() і

і

![]() ,

за допомогою яких при С

= 0 тригер можна встановити в стан 1 через

подачу сигналів

,

за допомогою яких при С

= 0 тригер можна встановити в стан 1 через

подачу сигналів ![]() = 1,

= 1,

![]() =

0 або в стан 0 через подачу сигналів

=

0 або в стан 0 через подачу сигналів

![]() = 0,

= 0,

![]() =

1.

=

1.

Функцію

переходів JK–тригера Q(t + 1)

можна

представити у вигляді булевих функцій

від змінних, що відповідають попередньому

стану t

і вхідним сигналам тригера при ![]() =

= ![]() =1

(тобто сигнали на несинхронізованих

входах не впливають на стан тригера):

=1

(тобто сигнали на несинхронізованих

входах не впливають на стан тригера):

![]()

Функціонування

JK–тригера може бути описано таблицею

переходів. Наводиться таблиця переходів

(таблиця 4) при ![]() =

= ![]() =1

під

дією синхронізованих входів (С

= 1).

=1

під

дією синхронізованих входів (С

= 1).

Таблиця 4. Таблиця переходів JK–тригера.

|

t |

t + 1 |

Коментар | |

|

J |

K |

Q | |

|

0 |

0 |

Q(t) |

Зберігання 0 або 1 |

|

0 |

1 |

0 |

Встановлення 1 |

|

1 |

0 |

1 |

Встановлення 0 |

|

1 |

1 |

|

Інверсія стану |

JK–тригер зручний тим, що при різних варіантах підключення його входів можна отримати схеми, що функціонують як D–, T– і RS–тригери. Схеми варіантів включення універсального JK–тригера: а) – як D–тригер; б), в) – як Т–тригер; г) – як RS–тригер