- •Chapter 1 Intel® Advanced Vector Extensions

- •1.1 About This Document

- •1.2 Overview

- •1.3.2 Instruction Syntax Enhancements

- •1.3.3 VEX Prefix Instruction Encoding Support

- •1.4 Overview AVX2

- •1.5 Functional Overview

- •1.6 General Purpose Instruction Set Enhancements

- •2.1 Detection of PCLMULQDQ and AES Instructions

- •2.2 Detection of AVX and FMA Instructions

- •2.2.1 Detection of FMA

- •2.2.3 Detection of AVX2

- •2.3.1 FMA Instruction Operand Order and Arithmetic Behavior

- •2.4 Accessing YMM Registers

- •2.5 Memory alignment

- •2.7 Instruction Exception Specification

- •2.7.1 Exceptions Type 1 (Aligned memory reference)

- •2.7.2 Exceptions Type 2 (>=16 Byte Memory Reference, Unaligned)

- •2.7.3 Exceptions Type 3 (<16 Byte memory argument)

- •2.7.5 Exceptions Type 5 (<16 Byte mem arg and no FP exceptions)

- •2.7.7 Exceptions Type 7 (No FP exceptions, no memory arg)

- •2.7.8 Exceptions Type 8 (AVX and no memory argument)

- •2.8.1 Clearing Upper YMM State Between AVX and Legacy SSE Instructions

- •2.8.3 Unaligned Memory Access and Buffer Size Management

- •2.9 CPUID Instruction

- •3.1 YMM State, VEX Prefix and Supported Operating Modes

- •3.2 YMM State Management

- •3.2.1 Detection of YMM State Support

- •3.2.2 Enabling of YMM State

- •3.2.4 The Layout of XSAVE Area

- •3.2.5 XSAVE/XRSTOR Interaction with YMM State and MXCSR

- •3.2.6 Processor Extended State Save Optimization and XSAVEOPT

- •3.2.6.1 XSAVEOPT Usage Guidelines

- •3.3 Reset Behavior

- •3.4 Emulation

- •4.1 Instruction Formats

- •4.1.1 VEX and the LOCK prefix

- •4.1.2 VEX and the 66H, F2H, and F3H prefixes

- •4.1.3 VEX and the REX prefix

- •4.1.4 The VEX Prefix

- •4.1.4.1 VEX Byte 0, bits[7:0]

- •4.1.4.2 VEX Byte 1, bit [7] - ‘R’

- •4.1.5 Instruction Operand Encoding and VEX.vvvv, ModR/M

- •4.1.6 The Opcode Byte

- •4.1.7 The MODRM, SIB, and Displacement Bytes

- •4.1.8 The Third Source Operand (Immediate Byte)

- •4.1.9.1 Vector Length Transition and Programming Considerations

- •4.1.10 AVX Instruction Length

- •4.2 Vector SIB (VSIB) Memory Addressing

- •4.3 VEX Encoding Support for GPR Instructions

- •5.1 Interpreting InstructIon Reference Pages

- •5.1.1 Instruction Format

- •5.1.2 Opcode Column in the Instruction Summary Table

- •5.1.3 Instruction Column in the Instruction Summary Table

- •5.1.4 Operand Encoding column in the Instruction Summary Table

- •5.1.5 64/32 bit Mode Support column in the Instruction Summary Table

- •5.1.6 CPUID Support column in the Instruction Summary Table

- •5.2 Summary of Terms

- •5.3 Instruction SET Reference

- •MPSADBW - Multiple Sum of Absolute Differences

- •PALIGNR - Byte Align

- •PBLENDW - Blend Packed Words

- •PHADDW/PHADDD - Packed Horizontal Add

- •PHADDSW - Packed Horizontal Add with Saturation

- •PHSUBW/PHSUBD - Packed Horizontal Subtract

- •PHSUBSW - Packed Horizontal Subtract with Saturation

- •PMOVSX - Packed Move with Sign Extend

- •PMOVZX - Packed Move with Zero Extend

- •PMULDQ - Multiply Packed Doubleword Integers

- •PMULHRSW - Multiply Packed Unsigned Integers with Round and Scale

- •PMULHUW - Multiply Packed Unsigned Integers and Store High Result

- •PMULHW - Multiply Packed Integers and Store High Result

- •PMULLW/PMULLD - Multiply Packed Integers and Store Low Result

- •PMULUDQ - Multiply Packed Unsigned Doubleword Integers

- •POR - Bitwise Logical Or

- •PSADBW - Compute Sum of Absolute Differences

- •PSHUFB - Packed Shuffle Bytes

- •PSHUFD - Shuffle Packed Doublewords

- •PSHUFLW - Shuffle Packed Low Words

- •PSIGNB/PSIGNW/PSIGND - Packed SIGN

- •PSLLDQ - Byte Shift Left

- •PSLLW/PSLLD/PSLLQ - Bit Shift Left

- •PSRAW/PSRAD - Bit Shift Arithmetic Right

- •PSRLDQ - Byte Shift Right

- •PSRLW/PSRLD/PSRLQ - Shift Packed Data Right Logical

- •PSUBB/PSUBW/PSUBD/PSUBQ -Packed Integer Subtract

- •PSUBSB/PSUBSW -Subtract Packed Signed Integers with Signed Saturation

- •PSUBUSB/PSUBUSW -Subtract Packed Unsigned Integers with Unsigned Saturation

- •PXOR - Exclusive Or

- •VPBLENDD - Blend Packed Dwords

- •VPERMD - Full Doublewords Element Permutation

- •VPERMPD - Permute Double-Precision Floating-Point Elements

- •VPERMPS - Permute Single-Precision Floating-Point Elements

- •VPERMQ - Qwords Element Permutation

- •VPSLLVD/VPSLLVQ - Variable Bit Shift Left Logical

- •VPSRAVD - Variable Bit Shift Right Arithmetic

- •VPSRLVD/VPSRLVQ - Variable Bit Shift Right Logical

- •VGATHERDPD/VGATHERQPD - Gather Packed DP FP values Using Signed Dword/Qword Indices

- •VGATHERDPS/VGATHERQPS - Gather Packed SP FP values Using Signed Dword/Qword Indices

- •VPGATHERDD/VPGATHERQD - Gather Packed Dword values Using Signed Dword/Qword Indices

- •VPGATHERDQ/VPGATHERQQ - Gather Packed Qword values Using Signed Dword/Qword Indices

- •6.1 FMA InstructIon SET Reference

- •Chapter 7 Instruction Set Reference - VEX-Encoded GPR Instructions

- •7.1 Instruction Format

- •7.2 INSTRUCTION SET REFERENCE

- •BZHI - Zero High Bits Starting with Specified Bit Position

- •INVPCID - Invalidate Processor Context ID

- •Chapter 8 Post-32nm Processor Instructions

- •8.1 Overview

- •8.2 CPUID Detection of New Instructions

- •8.4 Vector Instruction Exception Specification

- •8.6 Using RDRAND Instruction and Intrinsic

- •8.7 Instruction Reference

- •A.1 AVX Instructions

- •A.2 Promoted Vector Integer Instructions in AVX2

- •B.1 Using Opcode Tables

- •B.2 Key to Abbreviations

- •B.2.1 Codes for Addressing Method

- •B.2.2 Codes for Operand Type

- •B.2.3 Register Codes

- •B.2.4 Opcode Look-up Examples for One, Two, and Three-Byte Opcodes

- •B.2.4.1 One-Byte Opcode Instructions

- •B.2.4.2 Two-Byte Opcode Instructions

- •B.2.4.3 Three-Byte Opcode Instructions

- •B.2.4.4 VEX Prefix Instructions

- •B.2.5 Superscripts Utilized in Opcode Tables

- •B.3 One, Two, and THREE-Byte Opcode Maps

- •B.4.1 Opcode Look-up Examples Using Opcode Extensions

- •B.4.2 Opcode Extension Tables

- •B.5 Escape Opcode Instructions

- •B.5.1 Opcode Look-up Examples for Escape Instruction Opcodes

- •B.5.2 Escape Opcode Instruction Tables

- •B.5.2.1 Escape Opcodes with D8 as First Byte

- •B.5.2.2 Escape Opcodes with D9 as First Byte

- •B.5.2.3 Escape Opcodes with DA as First Byte

- •B.5.2.4 Escape Opcodes with DB as First Byte

- •B.5.2.5 Escape Opcodes with DC as First Byte

- •B.5.2.6 Escape Opcodes with DD as First Byte

- •B.5.2.7 Escape Opcodes with DE as First Byte

- •B.5.2.8 Escape Opcodes with DF As First Byte

APPLICATION PROGRAMMING MODEL

CHAPTER 2

APPLICATION PROGRAMMING MODEL

The application programming model for AVX2 is the same as Intel AVX and FMA. The VEX-encoded general-purpose instructions generally follows legacy general-purpose instructions. They are summarized as follows:

•Section 2.1 through Section 2.8 apply to AVX2, AVX and FMA. The OS support and detection process is identical for AVX2, AVX, F16C, and FMA

•The numeric exception behavior of FMA is similar to previous generations of SIMD floating-point instructions. The specific details are described in Section 2.3.

CPUID instruction details for detecting AVX, FMA, AESNI, PCLMULQDQ, AVX2, BMI1, BMI2, LZCNT and INVPCID are described in Section 2.9.

2.1DETECTION OF PCLMULQDQ AND AES INSTRUCTIONS

Before an application attempts to use the following AES instructions: AESDEC/AESDECLAST/AESENC/AESENCLAST/AESIMC/AESKEYGENASSIST, it must check that the processor supports the AES extensions. AES extensions is supported if CPUID.01H:ECX.AES[bit 25] = 1.

Prior to using PCLMULQDQ instruction, application must check if CPUID.01H:ECX.PCLMULQDQ[bit 1] = 1.

Operating systems that support handling SSE state will also support applications that use AES extensions and PCLMULQDQ instruction. This is the same requirement for SSE2, SSE3, SSSE3, and SSE4.

2.2DETECTION OF AVX AND FMA INSTRUCTIONS

AVX and FMA operate on the 256-bit YMM register state. System software requirements to support YMM state is described in Chapter 3.

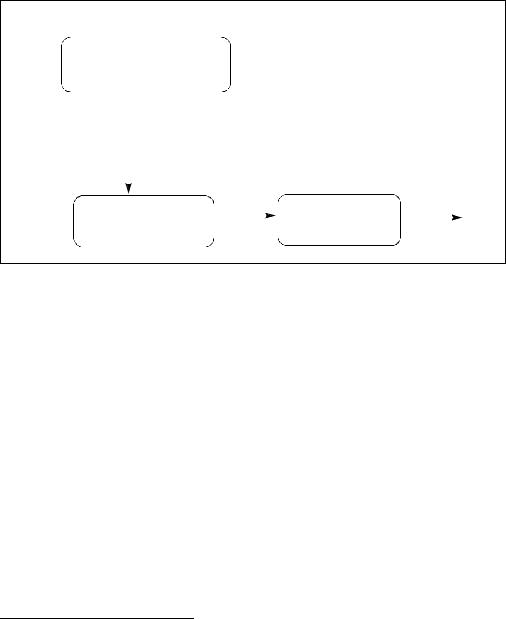

Application detection of new instruction extensions operating on the YMM state follows the general procedural flow in Figure 2-1.

Ref. # 319433-011 |

2-1 |

APPLICATION PROGRAMMING MODEL

Check feature flag

CPUID.1H:ECX.OXSAVE = 1?

|

OS provides processor |

|

extended state management |

Yes |

Implied HW support for |

|

XSAVE, XRSTOR, XGETBV, XFEATURE_ENABLED_MASK |

|

|

Check enabled state in |

|

Check feature flag |

|

|

|

|

|

||

XFEM via XGETBV |

State |

for Instruction set |

ok to use |

|

enabled |

|

Instructions |

||

|

|

|||

Figure 2-1. General Procedural Flow of Application Detection of AVX

Prior to using AVX, the application must identify that the operating system supports the XGETBV instruction, the YMM register state, in addition to processor’s support for YMM state management using XSAVE/XRSTOR and AVX instructions. The following simplified sequence accomplishes both and is strongly recommended.

1)Detect CPUID.1:ECX.OSXSAVE[bit 27] = 1 (XGETBV enabled for application use1)

2)Issue XGETBV and verify that XFEATURE_ENABLED_MASK[2:1] = ‘11b’ (XMM state and YMM state are enabled by OS).

3)detect CPUID.1:ECX.AVX[bit 28] = 1 (AVX instructions supported).

(Step 3 can be done in any order relative to 1 and 2)

The following pseudocode illustrates this recommended application AVX detection process:

----------------------------------------------------------------------------------------

INT supports_AVX() { ; result in eax

mov eax, 1 cpuid

1.If CPUID.01H:ECX.OSXSAVE reports 1, it also indirectly implies the processor supports XSAVE, XRSTOR, XGETBV, processor extended state bit vector XFEATURE_ENALBED_MASK register. Thus an application may streamline the checking of CPUID feature flags for XSAVE and OSXSAVE. XSETBV is a privileged instruction.

2-2 |

Ref. # 319433-011 |

APPLICATION PROGRAMMING MODEL

and ecx, 018000000H

cmp ecx, 018000000H; check both OSXSAVE and AVX feature flags jne not_supported

; processor supports AVX instructions and XGETBV is enabled by OS mov ecx, 0; specify 0 for XFEATURE_ENABLED_MASK register XGETBV; result in EDX:EAX

and eax, 06H

cmp eax, 06H; check OS has enabled both XMM and YMM state support jne not_supported

mov eax, 1 jmp done

NOT_SUPPORTED: mov eax, 0

done:

}

-------------------------------------------------------------------------------

Note: It is unwise for an application to rely exclusively on CPUID.1:ECX.AVX[bit 28] or at all on CPUID.1:ECX.XSAVE[bit 26]: These indicate hardware support but not operating system support. If YMM state management is not enabled by an operating systems, AVX instructions will #UD regardless of CPUID.1:ECX.AVX[bit 28]. “CPUID.1:ECX.XSAVE[bit 26] = 1” does not guarantee the OS actually uses the XSAVE process for state management.

These steps above also apply to enhanced 128-bit SIMD floating-pointing instructions in AVX (using VEX prefix-encoding) that operate on the YMM states. Application detection of VEX-encoded AES is described in Section 2.2.2.

2.2.1Detection of FMA

Hardware support for FMA is indicated by CPUID.1:ECX.FMA[bit 12]=1.

Application Software must identify that hardware supports AVX as explained in Section 2.2, after that it must also detect support for FMA by CPUID.1:ECX.FMA[bit 12]. The recommended pseudocode sequence for detection of FMA is:

----------------------------------------------------------------------------------------

INT supports_fma() { ; result in eax

mov eax, 1 cpuid

and ecx, 018001000H

Ref. # 319433-011 |

2-3 |

APPLICATION PROGRAMMING MODEL

cmp ecx, 018001000H; check OSXSAVE, AVX, FMA feature flags jne not_supported

; processor supports AVX,FMA instructions and XGETBV is enabled by OS mov ecx, 0; specify 0 for XFEATURE_ENABLED_MASK register

XGETBV; result in EDX:EAX and eax, 06H

cmp eax, 06H; check OS has enabled both XMM and YMM state support jne not_supported

mov eax, 1 jmp done

NOT_SUPPORTED: mov eax, 0

done:

}

-------------------------------------------------------------------------------

Note that FMA comprises of 256-bit and 128-bit SIMD instructions operating on YMM states.

2.2.2Detection of VEX-Encoded AES and VPCLMULQDQ

VAESDEC/VAESDECLAST/VAESENC/VAESENCLAST/VAESIMC/VAESKEYGENASSIST instructions operate on YMM states. The detection sequence must combine checking for CPUID.1:ECX.AES[bit 25] = 1 and the sequence for detection application support for AVX.

Similarly, the detection sequence for VPCLMULQDQ must combine checking for CPUID.1:ECX.PCLMULQDQ[bit 1] = 1 and the sequence for detection application support for AVX.

This is shown in the pseudocode:

----------------------------------------------------------------------------------------

INT supports_VAES() { ; result in eax mov eax, 1

cpuid

and ecx, 01A000000H

cmp ecx, 01A000000H; check OSXSAVE, AVX and AES feature flags jne not_supported

2-4 |

Ref. # 319433-011 |

APPLICATION PROGRAMMING MODEL

; processor supports AVX and VEX.128-encoded AES instructions and XGETBV is enabled by OS

mov ecx, 0; specify 0 for XFEATURE_ENABLED_MASK register XGETBV; result in EDX:EAX

and eax, 06H

cmp eax, 06H; check OS has enabled both XMM and YMM state support jne not_supported

mov eax, 1 jmp done

NOT_SUPPORTED: mov eax, 0

done:

}

INT supports_VPCLMULQDQ() { ; result in eax

mov eax, 1 cpuid

and ecx, 018000002H

cmp ecx, 018000002H; check OSXSAVE, AVX and PCLMULQDQ feature flags jne not_supported

; processor supports AVX and VPCLMULQDQ instructions and XGETBV is enabled by OS

mov ecx, 0; specify 0 for XFEATURE_ENABLED_MASK register XGETBV; result in EDX:EAX

and eax, 06H

cmp eax, 06H; check OS has enabled both XMM and YMM state support jne not_supported

mov eax, 1 jmp done

NOT_SUPPORTED: mov eax, 0

done:

}

-------------------------------------------------------------------------------

Ref. # 319433-011 |

2-5 |