- •Основы цифровой электроники

- •1.1. Логические функции

- •1.1.1Аксиомы и теоремы алгебры логики

- •1.1.2Операция сумма по модулю два

- •1.2. Логические элементы

- •Комбинационные схемы

- •1.3. Некоторые системы счисления

- •1.4. Дешифратор

- •1.5. Шифратор

- •1.6. Демультиплексор

- •1.7. Увеличение разрядности дешифраторов и демультиплексоров

- •1.8. Мультиплексор

- •1.9. Преобразователи кода

- •1.10. Сумматоры

- •Последовательностные схемы

- •1.11. Триггеры

- •1.11.1Асинхронный rs-триггер

- •1.11.2Синхронный rs-триггер

- •1.11.4Синхронный (динамический) d-триггер

- •1.11.5Универсальный jk-триггер

- •1.11.7Взаимные преобразования триггеров

- •1.12. Счетчики

- •1.13. Регистры

1.6. Демультиплексор

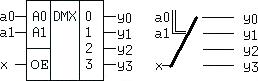

Устройство передающее сигнал с информационного входа “х” на один из выходов, причем номер этого выхода равен десятичному эквиваленту двоичного кода на адресных входах, называется демультиплексором (ДМ). В качестве ДМ используется дешифратор, у которого на вход ОЕ подается информационный сигнал х. Например, если на адресные входы подать код a1a0=10(BIN)=2(DEC), то сигнал х появится на выходе у2, а на остальных выходах yi=0.

В самом деле, если х=0 (ОЕ=0), то на всех выходах ДМ также нули, в том числе у2=0. А если х=1 (ОЕ=1), то вследствие того, что ala0=2 будет активизирован выход у2=1. Следовательно при ala0=10(BIN)=2(DEC) сигнал на выходе у2=х, что соответствует определению демультиплексора. На рис.2.4 даны условное обозначение ДМ "1 в 4" и его механический аналог.

Рис.2.4

1.7. Увеличение разрядности дешифраторов и демультиплексоров

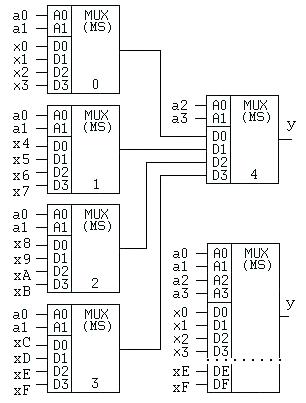

На рис.2.5 показано соединение двух ДШ "3 в 8" для получения одного ДШ "4 в 16", или двух демультиплексоров "1 в 8" для получения одного "1 в 16".

Рис.2.5

При

пассивном значении ОЕ=1 на всех выходах

yi

будет "1" независимо от значений

сигналов ai.

Если ОЕ=0 (активный уровень), то какой из

дешифраторов работает, зависит только

от сигнала а3. Так если а3=0, то на обоих

разрешающих входах ДШ (А) ОЕ и & будут

активные уровни, а на разрешающем входе

ОЕ дешифратора (В) сигнал

![]() ,

равный единице, переведет все выходы в

состояние 1, т.е. работоспособным будет

ДШ (А). Когда а3=1, наоборот работоспособным

становится дешифратор (В), потому что

по входу ОЕ дешифратора (А) этот сигнал

запрещает его выходы. Таким образом,

комбинации сигналов а3 и а2..а0 образуют

последовательность двоичного кода 0000

... 0111 (0 ... 7) для дешифратора (А) и

последовательность 1000 ... 1111 (8 ... 15) для

ДШ (В). Поэтому нумерация выходов yi,

получившегося ДШ

"4 в

16" –

сквозная от 0 до 15. На рис.2.5 справа

приведено условное обозначение,

получившегося дешифратора-демультиплексора

(в справочниках они так часто и называются

и помещаются в один раздел).

,

равный единице, переведет все выходы в

состояние 1, т.е. работоспособным будет

ДШ (А). Когда а3=1, наоборот работоспособным

становится дешифратор (В), потому что

по входу ОЕ дешифратора (А) этот сигнал

запрещает его выходы. Таким образом,

комбинации сигналов а3 и а2..а0 образуют

последовательность двоичного кода 0000

... 0111 (0 ... 7) для дешифратора (А) и

последовательность 1000 ... 1111 (8 ... 15) для

ДШ (В). Поэтому нумерация выходов yi,

получившегося ДШ

"4 в

16" –

сквозная от 0 до 15. На рис.2.5 справа

приведено условное обозначение,

получившегося дешифратора-демультиплексора

(в справочниках они так часто и называются

и помещаются в один раздел).

1.8. Мультиплексор

Мультиплексоры – цифровые многопозиционные переключатели или, по другому, коммутаторы. У мультиплексора может быть, например, 16 входов и один выход. Это означает, что, если к этим 16 входам присоединены 16 источников цифровых сигналов – генераторов последовательных цифровых слов, то байты от любого из генераторов можно передавать в единственный выходной провод. Для этого нужный нам вход требуется выбрать, подав на четыре входа селекции (т.е. выбора номера канала; напомним, что 24= 16) двоичный код адреса. Так, для передачи на выход данных от канала номер 9 следует установить код адреса 1001. Мультиплексоры способны выбирать, селектировать определенный канал. Поэтому их иногда называют селекторами. Используется и двойное название: селекторы-мультиплексоры.

Таким образом:

Мультиплексор (или селектор-мультиплексор) передает сигнал с одного из информационных входов xi на единственный выход у, причем номер этого входа равен десятичному эквиваленту двоичного кода на адресных входах.

Если

имеется вход разрешения выхода ОЕ(![]() ),

то "0 (1)" на этом входе должен

перевести выход в пассивное состояние

(см. последнюю строчку таблицы): если

выход мультиплексора тристабильный,

то на этом выходе установится

высокоимпедансное z-состояние.

Рассмотрим мультиплексор "4 в 1",

имеющий четыре информационных и,

соответственно, два адресных входа.

),

то "0 (1)" на этом входе должен

перевести выход в пассивное состояние

(см. последнюю строчку таблицы): если

выход мультиплексора тристабильный,

то на этом выходе установится

высокоимпедансное z-состояние.

Рассмотрим мультиплексор "4 в 1",

имеющий четыре информационных и,

соответственно, два адресных входа.

Десятичное число |

Входы |

Вых |

Логическая функция |

||||||||

a1 |

а0 |

ОЕ |

|

х0 |

x1 |

х2 |

х3 |

у |

|

||

0 |

0 |

0 |

1 |

0 |

х0 |

X |

X |

X |

х0 |

|

|

1 |

0 |

1 |

X |

x1 |

X |

X |

x1 |

|

|

||

2 |

1 |

0 |

X |

X |

х2 |

X |

х2 |

|

|

||

3 |

1 |

1 |

X |

X |

X |

х3 |

х3 |

|

|

||

X |

X |

X |

0 |

1 |

X |

X |

X |

X |

0 |

1 |

у=0 или z ( =1 или z) |

Величина

х может принимать любые значения.

Количество входных переменных равно

7, и полная таблица истинности должна

иметь 128 строк. В приведенной таблице в

4-х основных строках упаковано 64 исходных

(с учетом значений х0 ... х3), а в последней

строке – остальные 64 строчки. Анализ

верхней строки приводит к выводу, что

у=х0, если a1=0

И а0=0 И ОЕ=1 независимо от переменных

x1…х3,

поэтому для данного входного набора

можно записать:

![]() .

Аналогично записывается у для остальных

трех наборов переменных. Общее решение

тогда будет иметь вид:

.

Аналогично записывается у для остальных

трех наборов переменных. Общее решение

тогда будет иметь вид:

![]() (2.2)

(2.2)

Применяя аксиомы двойного отрицания и двойственности к правой части уравнения, получим:

![]() (2.3)

(2.3)

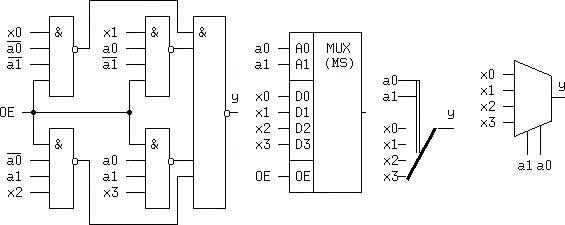

Выражению (2.3) соответствует схема, приведенная на рис.2.6 слева, а ее условное обозначение и механический аналог – в центре. В зарубежной литературе можно встретить обозначение, показанное справа. Если на адресные входы подать комбинацию a1a0 = 11(BIN) = 3(DEC), то к выходу у будет подключен вход D3, при условии, что ОЕ=1. Мультиплексор может иметь инверсный выход, а также третье состояние этого выхода, которое отмечается на схеме ромбом с поперечной чертой.

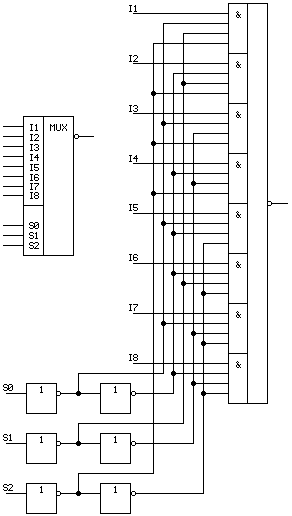

На следующем рисунке 2.7 показан способ соединения пяти мультиплексоров "41" в один мультиплексор "161".

Рис.2.6

Рис.2.7

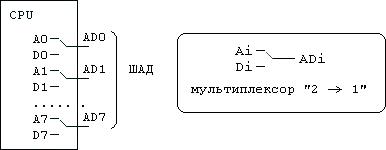

Мультиплексоры находят широкое применение в технике связи, а также в вычислительной технике, например многие выводы у микропроцессоров "мультиплексированы", т.е. к одному выходу подключается несколько внутренних источников различных сигналов. Это могут быть внутренние сигналы линий шины данных (D7..D0) и шины адреса (А7..А0), передаваемые поочередно на общие выводы AD7..AD0 совмещенной шины адрес/данные (ШАД), что позволяет сократить общее число выводов микропроцессора (на рисунке в 2 раза). Используются 8 мультиплексоров "21"

Примеры мультиплексоров, выпускаемых промышленно

Рис.2.8

![]()

Данная формула следует из таблицы соответствия адресных входов подключаемым входам данных (рекомендуется закончить эту формулу самостоятельно).

2. Микросхема 555КП7 – мультиплексор, отличающийся от КП5 наличием входа разрешения С и дополнительным неинвертирующим выходом. Логическая функция Y соответствует приведенной выше функции КП5 и выполняется при низком уровне сигнала на входе С (вид функции и УГО рекомендуется выполнить самостоятельно).