- •Основы цифровой электроники

- •1.1. Логические функции

- •1.1.1Аксиомы и теоремы алгебры логики

- •1.1.2Операция сумма по модулю два

- •1.2. Логические элементы

- •Комбинационные схемы

- •1.3. Некоторые системы счисления

- •1.4. Дешифратор

- •1.5. Шифратор

- •1.6. Демультиплексор

- •1.7. Увеличение разрядности дешифраторов и демультиплексоров

- •1.8. Мультиплексор

- •1.9. Преобразователи кода

- •1.10. Сумматоры

- •Последовательностные схемы

- •1.11. Триггеры

- •1.11.1Асинхронный rs-триггер

- •1.11.2Синхронный rs-триггер

- •1.11.4Синхронный (динамический) d-триггер

- •1.11.5Универсальный jk-триггер

- •1.11.7Взаимные преобразования триггеров

- •1.12. Счетчики

- •1.13. Регистры

1.13. Регистры

Регистр – это линейка из нескольких триггеров, в которой в отличие от счетчиков-делителей нет внутренних запрещающих обратных связей. Регистры применяются для накопления и сдвига данных.

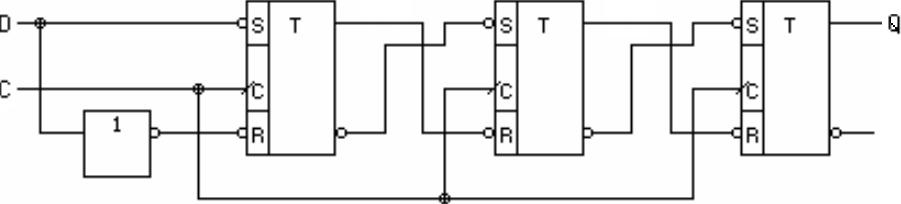

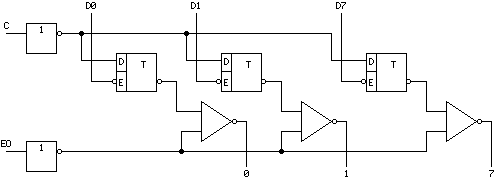

В

простейшем сдвиговом регистре триггеры

соединены последовательно: выходы q и

![]() предыдущего динамического RSC-триггера

(у такого триггера, в отличие от

рассмотренного в п.3.1.2, запись информации

осуществляется только в момент переднего

фронта на входе С) передают бит данных

на входы R и S последующего. Все тактовые

входы С триггеров соединены параллельно.

При таком включении единица, записанная

в виде напряжений низкого и высокого

уровней по входам R и S первого триггера,

после подачи одного тактового импульса

перейдет во второй триггер, затем во

время следующего тактового импульса

она попадет в третий триггер и так

проследует далее, до конца регистра

(см. рисунок ниже).

предыдущего динамического RSC-триггера

(у такого триггера, в отличие от

рассмотренного в п.3.1.2, запись информации

осуществляется только в момент переднего

фронта на входе С) передают бит данных

на входы R и S последующего. Все тактовые

входы С триггеров соединены параллельно.

При таком включении единица, записанная

в виде напряжений низкого и высокого

уровней по входам R и S первого триггера,

после подачи одного тактового импульса

перейдет во второй триггер, затем во

время следующего тактового импульса

она попадет в третий триггер и так

проследует далее, до конца регистра

(см. рисунок ниже).

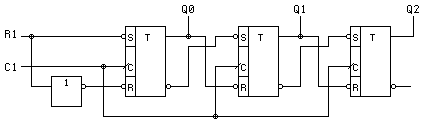

Аналогично продвигается по регистру многоразрядное слово: оно поразрядно вводится на входы R и S первого триггера. Простейший регистр имеет один вход и один выход – последовательные. Вход управления также единственный – тактовый. Если ко входу каждого триггера добавить разрешающую логику, можно получить дополнительные, так называемые параллельные входы одновременной загрузки байта в регистр. Здесь, как правило, используются дополнительные защелки, где фиксируются данные, поступившие на входы после прихода тактового импульса. В такую схему добавляется вход разрешения записи.

Можно предусмотреть также логическую схему параллельного отображения на выходах состояния каждого триггера:

Тогда после заполнения регистра от последовательного или параллельных входов, по команде разрешения выхода накопленное цифровое слово можно отобразить поразрядно сразу на всех параллельных выходах. Для удобства поочередной выдачи данных от таких регистров – буферных накопителей в шину данных обрабатывающего устройства – процессора – параллельные выходы регистров снабжаются выходными буферными усилителями, имеющими третье, разомкнутое z-состояние. По многопроводной шине данных процессор получит цифровое слово – байт от выходов того регистра, которому дана команда разрешения выдачи.

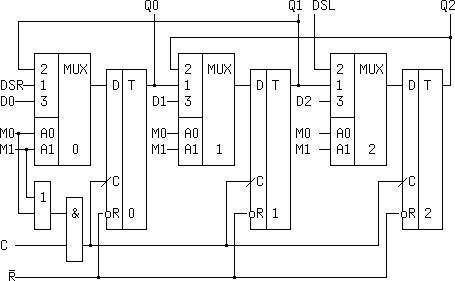

Регистры,

как реверсивные счетчики, могут быть

двунаправленными, загруженное слово

можно сдвигать по линейке триггеров

как вправо, так и влево. Для включения

режимов сдвига влево или вправо служит

специальный вход команды. Название

“реверсивный регистр сдвига” и

указывает, что сдвиг

данных от разряда к разряду может

производиться, как в одну сторону, так

и в другую. Одна

из возможных схем трехразрядного

реверсивного регистра с двумя

последовательными информационными

входами (для сдвига информации влево

DSL

и вправо DSR),

с параллельными входами записи (D0..D2),

синхровходом С, входом

![]() установки в 0 всех триггеров и двумя

входами выбора режима М1,М0, приведена

на рисунке:

установки в 0 всех триггеров и двумя

входами выбора режима М1,М0, приведена

на рисунке:

К D-входу любого разряда, за исключением крайних, подключены, через входы 1 и 2 мультиплексора, выходы и левого, и правого соседних триггеров. Если М1=0, а М0=1, то к входам D подключены первые входы мультиплексоров, и информация в каждый триггер, кроме нулевого, записывается от левого соседа (происходит сдвиг вправо). Вход DSR служит в этом режиме для последовательного ввода информации. Если М1=1, М0=0, то ко входам D подключены вторые входы мультиплексоров и информация в каждый триггер, кроме последнего записывается от правого соседа (происходит сдвиг влево). Для последовательного ввода данных в этом режиме используется вход DSL. При М1=М0=1 происходит параллельная запись Qi=Di положительным фронтом тактового сигнала. Для хранения информации необходимо подать комбинацию М1=М0=0. В этом случае к D-входам триггеров подключатся нулевые входы мультиплексоров (на схеме не показаны). Чтобы не произошло несанкционированной записи схема ИЛИ-И запрещает в этом режиме прохождение синхроимпульсов. По такой схеме выполнен 8-разрядный регистр 1533ИР13. Реверсивный регистр может использоваться для быстрого (всего за n тактов) деления и умножения двоичных чисел на 2n, где n-число сдвигов. Например, вместо числа 5, после сдвига влево на 2 разряда, стало число 20:

Существуют многорежимные регистры. Их входные и выходные линии данных объединены и образуют так называемый порт данных. Это означает, что от шины данных процессора приходит один провод (а не два), который по команде служит или входным или выходным. Число сигнальных входов и выходов микросхемы за счет портовой организации можно уменьшить в 2 раза.

Однотипные регистры могут различаться функциями отдельных входов: синхронным или асинхронным сбросом, инверсными или прямыми входами, наличием выводов наращивания.

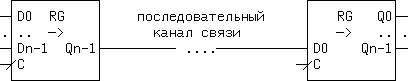

Одно из применений регистров сдвига с параллельной загрузкой кода заключается в преобразовании параллельного: формата данных в последовательный в передающем устройстве, передаче этих данных по однопроводной линии — связи (вторая линия должна быть, как минимум "землей" или экраном) и обратном преобразовании последовательной информации в параллельную в приемном устройстве:

Такая схема применяется в коммуникационных портах ЭВМ (СОМ-порты), в микросхеме К580ИК51, а также в модемах.

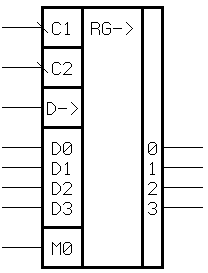

1. Микросхема 155ИР1 – четырехразрядный сдвиговой регистр. Он имеет последовательный вход данных D–>, четыре параллельных входа D0…D3, а также четыре выхода 0…3 от каждого из внутренних триггеров. Регистр имеет два тактовых входа: С1 для работы по последовательному входу и С2 для работы по параллельным входам. От любого из пяти входов данных код поступит на выходы синхронно с отрицательным перепадом, поданным на выбранный тактовый вход. Выбор режима работы регистра осуществляется подачей соответствующего сигнала на вход разрешения М0: при уровне лог.0 на этом входе разрешается последовательная работа, при лог.1 – параллельная.

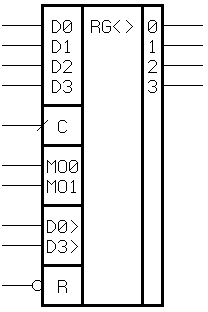

2. Микросхема 555ИР11 – универсальный четырехразрядный сдвиговый регистр, с помощью которого можно строго синхронно сдвигать цифровое слово вправо или влево. Т.о. это двунаправленный регистр.

Поскольку режимы хранения, загрузки и сдвига синхронные, следует фиксировать момент подачи вводных команд управления режимами до прихода тактового перепада.

Если на вход R подается напряжения уровня лог.0, происходит асинхронный сброс данных, т.е. на выходах 0…3 устанавливаются напряжения низкого уровня.

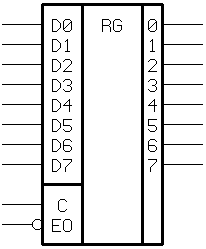

Схема регистра состоит из двух частей. Первая часть – это восемь нетактируемых D-триггеров со входом параллельной записи С. Пока С=1, данные от параллельных входов D-триггеров D0…D7 отображаются на выходах 0…7, т.е. проходят через первую часть регистра свободно. При С=0 происходит защелкивание данных в D-триггерах.

Вторая часть устройства управляется по входу разрешения EO (Output Enable). Ее восемь ключевых выходных усилителей имеют третье Z-состояние. Если ЕО=0, данные из триггеров регистра пройдут на выходы 0…7. Если ЕО=1, выходы разомкнутся. Последнее свойство позволяет подключать данный регистр к общей для ряда внешних устройств восьмиразрядной шине данных.