- •Основы цифровой электроники

- •1.1. Логические функции

- •1.1.1Аксиомы и теоремы алгебры логики

- •1.1.2Операция сумма по модулю два

- •1.2. Логические элементы

- •Комбинационные схемы

- •1.3. Некоторые системы счисления

- •1.4. Дешифратор

- •1.5. Шифратор

- •1.6. Демультиплексор

- •1.7. Увеличение разрядности дешифраторов и демультиплексоров

- •1.8. Мультиплексор

- •1.9. Преобразователи кода

- •1.10. Сумматоры

- •Последовательностные схемы

- •1.11. Триггеры

- •1.11.1Асинхронный rs-триггер

- •1.11.2Синхронный rs-триггер

- •1.11.4Синхронный (динамический) d-триггер

- •1.11.5Универсальный jk-триггер

- •1.11.7Взаимные преобразования триггеров

- •1.12. Счетчики

- •1.13. Регистры

1.11.2Синхронный rs-триггер

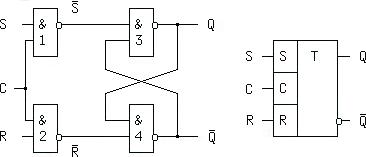

Если вместо входных инверторов 1 и 2 (см. рис.3.2) использовать элементы И-НЕ и их не задействованные входы соединить вместе, получится синхронный RS-триггер со статическим управлением (синхронизируемый уровнем). Схема и условное обозначение приведены на рис.3.4.

Рис.3.4

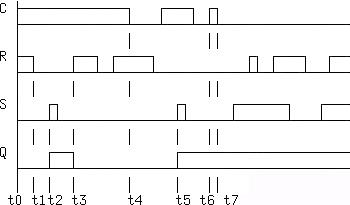

Нетрудно убедиться, что при С=0 независимо от значении S и R выходы сохраняют старые значения и триггер находится в режиме памяти. При С=1 он функционирует, как асинхронный RS-триггер. Триггеры со статическим управлением называют, также "прозрачными", т.к. при активном уровне синхросигнала С информация с входов беспрепятственно проходит на выходы. Временные диаграммы такого триггера приведены на рис.3.5.

Рис.3.5

До момента времени t4 сигнал С=1 и выходное значение определяется комбинациями сигналов R и S. В течение интервала времени t0…t1 на входе R действует 1, а сигнал S=0, поэтому Q тоже равно 0. Начиная с момента tl и до момента t2 R=S=0 и действует режим памяти (Q не изменяется). В момент t2 R=0, а S=1 и триггер устанавливается в состояние Q=1. С момента окончания импульса S и до момента t3 триггер хранит эту единицу, а в момент t3 сбрасывается, т.к. R=1, a S=0. Аналогично можно проанализировать и все остальные состояния выхода.

1.11.3D-L-триггер со статическим управлением

D-L-триггер имеет как минимум два входа: информационный вход D(ata) и вход управления записью/запоминанием (защелкиванием) L(oad)/L(atch) – отсюда его второе имя: "защелка". Последний вход часто обозначают символом С (Clock). Выходной сигнал Q принимает значение равное входному Q(t+dt)=D при L=1 и сохраняет предыдущее значение Q(t+dt)=Q(t) при L=0. Таблица состояний триггера имеет вид:

Текущее состояние |

Последующее состояние |

Название режима |

|||

L |

D |

Q(t) |

Q(t+dt) |

|

|

0 |

x |

Q |

Q |

|

Хранение информации(режим памяти) |

1 |

0 |

x |

0 |

1 |

Установка в "0" (сброс, очистка) |

1 |

1 |

x |

1 |

0 |

Установка в "1" (установка) |

Триггеры типа D-L описываются следующей функцией переходов:

![]()

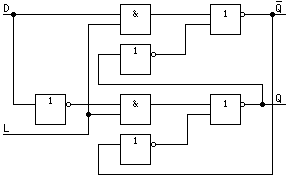

Такие триггеры также называются «прозрачными», т.к. при L=1 выходной сигнал триггера Q+=D, т.е. осуществляется прямая передача входного сигнала D на выход. Основное назначение D-L-триггеров – фиксация информации, подаваемой на вход D. Действительно, из функции переходов следует, что при переходе сигнала загрузки L в нулевое состояние на выходе триггера фиксируется последнее значение D до указанного перехода. Логически эквивалентная схема D-L-триггера имеет вид:

Рис.3.6

УГО

рассмотренного типа триггеров следующее:

Рассмотренные триггеры являются по-настоящему фиксирующими: в отличие от RS-триггеров, в которых изменение состояния производится, по сути, самими данными, в D-L-триггерах управление и данные разделены. Это позволяет организовывать «окна», т.е. временные промежутки, в течение которых осуществляется считывание потока данных. Другое возможное применение данных триггеров – построение интервальных счетчиков.