- •Основы цифровой электроники

- •1.1. Логические функции

- •1.1.1Аксиомы и теоремы алгебры логики

- •1.1.2Операция сумма по модулю два

- •1.2. Логические элементы

- •Комбинационные схемы

- •1.3. Некоторые системы счисления

- •1.4. Дешифратор

- •1.5. Шифратор

- •1.6. Демультиплексор

- •1.7. Увеличение разрядности дешифраторов и демультиплексоров

- •1.8. Мультиплексор

- •1.9. Преобразователи кода

- •1.10. Сумматоры

- •Последовательностные схемы

- •1.11. Триггеры

- •1.11.1Асинхронный rs-триггер

- •1.11.2Синхронный rs-триггер

- •1.11.4Синхронный (динамический) d-триггер

- •1.11.5Универсальный jk-триггер

- •1.11.7Взаимные преобразования триггеров

- •1.12. Счетчики

- •1.13. Регистры

1.10. Сумматоры

Сумматоры – устройства, осуществляющие основную арифметическую операцию – суммирование чисел в двоичном коде. Простейший случай – суммирование двух одноразрядных чисел: 0+0=0, 1+0=1, 0+1=1 и 1+1 =10. В последнем случае выходное число 10 (в десятичной записи это 2) оказалось двоичным двухразрядным. Появившаяся в старшем разряде суммы единица называется единицей переноса.

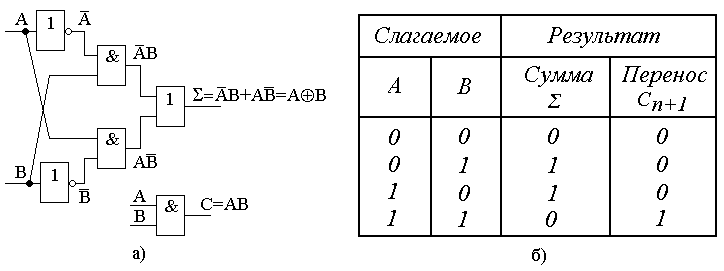

На первой лекции были перечислены состояния схемы «исключающее ИЛИ». Эти состояния соответствуют рассмотренному примеру (кроме случая 1l=0 – суммирование по модулю 2). К схеме «исключающее ИЛИ» несложно добавить выход переноса, т.е. генератор старшего разряда. Для этого оба суммируемых одноразрядных числа следует подать на схему И, выход которой даст необходимый старший разряд переноса 11=1. На рис. 2.11,а показана реализация схемы суммирования двух одноразрядных чисел, состоящая из элементов исключающее или и и. Схема имеет два выходных провода: суммы и переноса. Такая схема называется полусумматором.

Рис.2.11

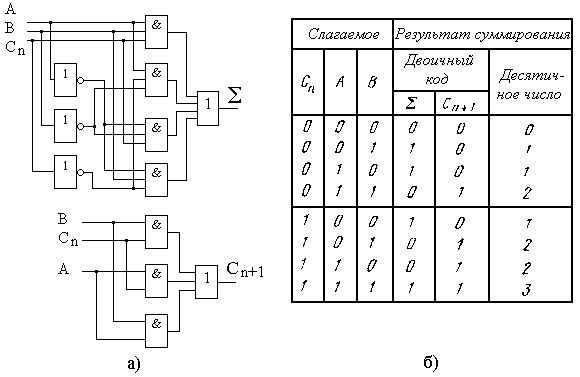

Полный сумматор должен иметь вход для приема сигнала переноса Cn (здесь n – число разрядов в суммируемых словах). Схема полного сумматора двух одноразрядных слов и таблица его состояний показаны на рис.2.12. В последнем столбце таблицы результаты суммирования даны в десятичной форме. В присутствии входной единицы переноса Cn сумма чисел А и В увеличивается на 1.

Рис.2.12

Полные сумматоры многоразрядных чисел составляются из одноразрядных и могут складывать многоразрядные числа двумя способами: параллельным или последовательным.

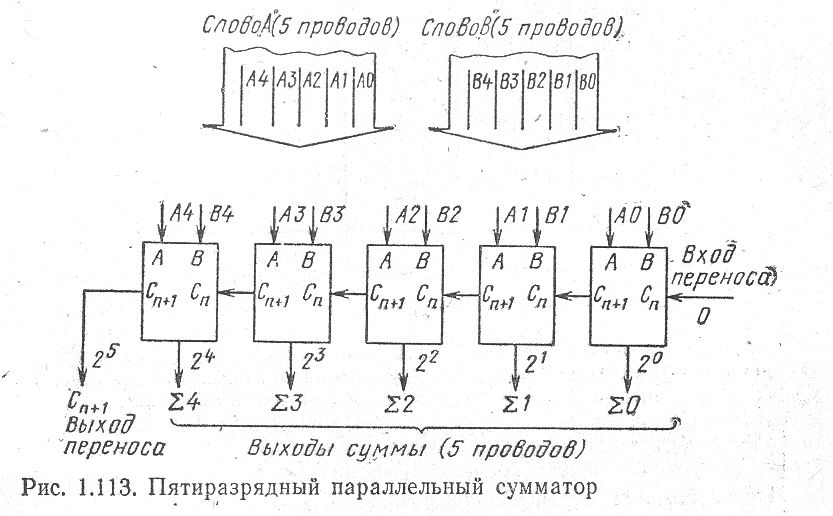

На рис.2.13 показана структура пятиразрядного параллельного сумматора.

Рис.2.13

Здесь поразрядно (в параллель) суммируются два пятиразрядных слова: разряд A0 с разрядом B0, A1 с B1 и так далее до A5 с B5. При этом в каждом элементарном сумматоре получаются парциальные суммы 0, 1 – 5 и сигналы внутреннего переноса Cn+1. Которые последовательно поступают на вход переноса Cn более старiего сумматора. Шестой выходной провод содержит сигнал переноса Cn+l=С6 (единица в шестом разряде). Таким образом, полная выходная сумма сумматора составляет 111111, т. е. 63 в десятичном эквиваленте.

Данное устройство нетрудно сделать любой длины, однако суммирование будет закончено лишь тогда, когда истечет время распространения сигналов переноса Сn через всю цепь одноразрядных сумматоров. Большое время распространения сигнала ограничивает применение параллельных сумматоров. Такой перенос иногда называют пульсирующим.

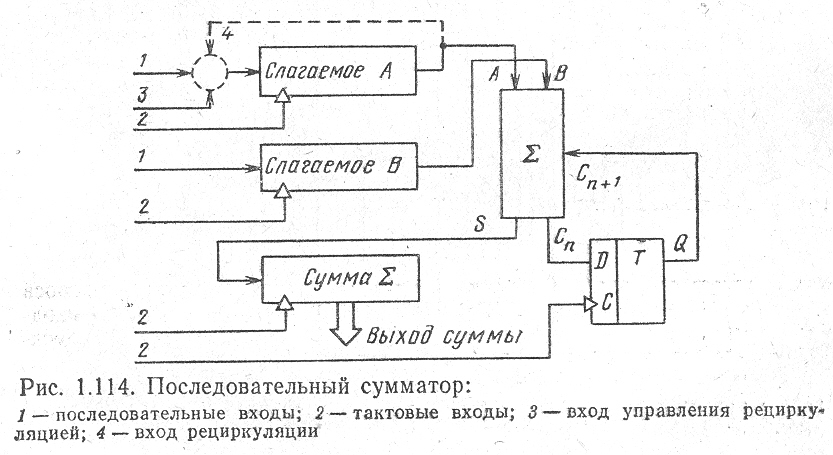

Последовательный двоичный сумматор (рис.2.14) содержит три n-разрядных регистра: регистры слагаемых A и B и регистр суммы. Суммируемые слова загружаются в регистры А и В поразрядно. С такой же скоростью один такт – один разряд происходит и суммирование, т. е. заполнение регистра суммы .

Рис.2.14

Дополнительный D-триггер необходим для запоминания на один такт разряда Сп для переноса его в разряд Сn+l. Регистры последовательных сумматоров могут иметь параллельную загрузку. Если необходимо, чтобы переменные числа В прибавлялись к постоянному числу А, регистр числа А надо запустить в режиме рециркуляции (штриховая линия на рис.2.14).