- •Основы цифровой электроники

- •1.1. Логические функции

- •1.1.1Аксиомы и теоремы алгебры логики

- •1.1.2Операция сумма по модулю два

- •1.2. Логические элементы

- •Комбинационные схемы

- •1.3. Некоторые системы счисления

- •1.4. Дешифратор

- •1.5. Шифратор

- •1.6. Демультиплексор

- •1.7. Увеличение разрядности дешифраторов и демультиплексоров

- •1.8. Мультиплексор

- •1.9. Преобразователи кода

- •1.10. Сумматоры

- •Последовательностные схемы

- •1.11. Триггеры

- •1.11.1Асинхронный rs-триггер

- •1.11.2Синхронный rs-триггер

- •1.11.4Синхронный (динамический) d-триггер

- •1.11.5Универсальный jk-триггер

- •1.11.7Взаимные преобразования триггеров

- •1.12. Счетчики

- •1.13. Регистры

1.5. Шифратор

Шифраторы выполняют обратную операцию: переводят сигнал, поданный только в один входной провод (например, в провод 9), в выходной параллельный двоичный код (в данном случае 1001), который появится на выходах шифратора. Подобный элемент можно назвать преобразователем позиционного кода в параллельный.

Номер входа |

Входы |

Выходы |

||||

х0 |

x1 |

х2 |

хЗ |

y1 |

у0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

2 |

0 |

0 |

1 |

0 |

1 |

0 |

3 |

0 |

0 |

0 |

1 |

1 |

1 |

В приоритетном Ш производится преобразование максимального десятичного номера активного входа в двоичный эквивалент этого номера. Для такого Ш входные сигналы, лежащие снизу от единичной диагонали, по определению могут иметь любое значение ("х" может быть 0 или 1). Следовательно, полная таблица истинности вместо нижних трех строчек должна содержать вообще-то еще 2+4+8=14 строк. Комбинация 0000 на входах не определена.

Номер входа |

Входы |

Выходы |

||||

х0 |

x1 |

х2 |

хЗ |

y1 |

у0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

х |

1 |

0 |

0 |

0 |

1 |

2 |

х |

х |

1 |

0 |

1 |

0 |

3 |

х |

х |

х |

1 |

1 |

1 |

y1 = х2+х3 и у0 = х1 + х3 .

У приоритетного шифратора выражение для у1 останется тем же самым, а для у0 примет вид

![]() .

.

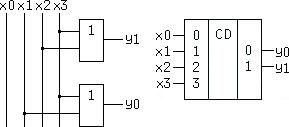

Реализация и условное обозначение неприоритетного Ш с прямой входной логикой приведены на рис.2.3. Переменная х0 оказалась "обделенной", но это произошло из-за того, что если нет сигнала ни на одном из первых трех входов, то он неизбежно должен присутствовать, по определению, на оставшемся, т.е. на третьем. Переменная х0 вместе с остальными может быть использована для формирования функции х0 + x1 + х2 + х3 равной 0, когда не активен ни один из входов, что может сигнализировать, например о неисправности источников сигналов.

Рис.2.3

Аналогичным

образом могут быть получены логические

выражения для шифраторов с инверсной

входной логикой, когда активным является

уровень лог.0 (эти выражения рекомендуется

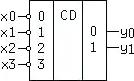

составить самостоятельно). УГО такого

Ш имеет вид:

Аналогичным

образом могут быть получены логические

выражения для шифраторов с инверсной

входной логикой, когда активным является

уровень лог.0 (эти выражения рекомендуется

составить самостоятельно). УГО такого

Ш имеет вид:

Шифраторы применяются в контроллерах прерываний работы микропроцессора внешними устройствами, в быстродействующем параллельном преобразователе напряжения в код (АЦП) и для кодирования номера клавиши.