- •Основы цифровой электроники

- •1.1. Логические функции

- •1.1.1Аксиомы и теоремы алгебры логики

- •1.1.2Операция сумма по модулю два

- •1.2. Логические элементы

- •Комбинационные схемы

- •1.3. Некоторые системы счисления

- •1.4. Дешифратор

- •1.5. Шифратор

- •1.6. Демультиплексор

- •1.7. Увеличение разрядности дешифраторов и демультиплексоров

- •1.8. Мультиплексор

- •1.9. Преобразователи кода

- •1.10. Сумматоры

- •Последовательностные схемы

- •1.11. Триггеры

- •1.11.1Асинхронный rs-триггер

- •1.11.2Синхронный rs-триггер

- •1.11.4Синхронный (динамический) d-триггер

- •1.11.5Универсальный jk-триггер

- •1.11.7Взаимные преобразования триггеров

- •1.12. Счетчики

- •1.13. Регистры

1.12. Счетчики

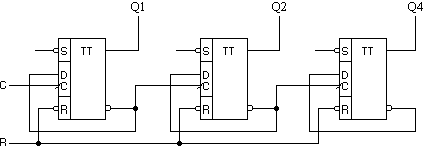

Соединив последовательно несколько триггерных схем-делителей частоты на два, получим простейший многоразрядный двоичный делитель. На рисунке показаны формирователи трех младших разрядов такого счетчика. По входу R осуществляется общий сброс триггеров (обнуление счетчика).

Более общее название для делителей частоты – счетчики. Коэффициент деления счетчика, состоящего из триггеров типа D или Т, составляет 2n; здесь n – число двоичных разрядов счетчика. В настоящее время используется много вариантов счетных схем: асинхронные и синхронные; двоичные и десятичные; однонаправленные, только с увеличением счета, и двунаправленные, счет в которых может увеличиваться или, уменьшаться (такие счетчики называют реверсивными). Коэффициент деления счетчика может быть либо постоянным, либо переключаемым.

Основой любой из этих схем служит линейка из нескольких триггеров. Перечисленные варианты счетчиков различаются схемой управления этими триггерами. Между триггерами добавляются логические связи, назначение которых – запретить прохождение в цикле счета лишним импульсам. К примеру, четырехтриггерный счетчик может делить исходную частоту на 16, так как 24= 16. Получим минимальный выходной код 0000, а максимальный 1111. Чтобы построить счетчик-делитель на 10, трех триггеров недостаточно (10>23), поэтому десятичный счетчик содержит в своей основе четыре триггера, но имеет обратные связи, останавливающие счет при коде 9= 1001.

Таким образом, удобно выпускать четырехтриггерные счетчики в двух вариантах: двоичном и десятичном. Примеры таких микросхем - пары: ИЕ6 и ИЕ7, ИE16 и ИЕ17. Расширять функции счетчиков можно, видоизменяя их цепи управления. Первоначально, счетчики были асинхронными. В асинхронном режиме тактовые импульсы для последующего триггера линейки вырабатывает предыдущий триггер.

В синхронном счетчике все триггеры получают тактовый импульс одновременно; поскольку тактовые входы их соединяются параллельно. Поэтому и триггеры переключатся практически одновременно. В асинхронном же счетчике каждый триггер вносит в процесс счета определенную задержку, поэтому разряды результирующего кода появляются на выходах триггеров неодновременно и несинхронно с соответствующим тактовым импульсом. Например, для четырехразрядного счетчика выходной параллельный код 1111 установится на выходах уже после того, как поступит шестнадцатый тактовый импульс.

Синхронная схема значительно сложнее асинхронной. На ее выходах данные от каждого разряда появляются одновременно и строго синхронно с последним входным импульсом. В синхронный счетчик разрешается синхронная (с тактовым импульсом): параллельная (в каждый триггер) загрузка начальных данных. Триггерная линейка синхронного счетчика снабжается специальным шифратором, который называется схемой ускоренного переноса (СУП).

Внутренние логические элементы управления, которыми часто снабжаются счетчики, позволяют сделать процесс счета реверсивным. Согласно команде, подаваемой на вход управления счетом «больше/меньше», можно либо увеличивать, либо уменьшать на единицу содержимое счетчика при каждом очередном тактовом импульсе. У некоторых счетчиков тактовые входы на увеличение и на уменьшение отдельные.

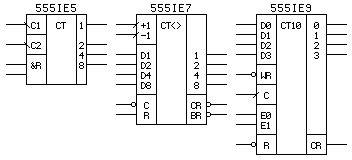

555ИЕ5

555ИЕ5

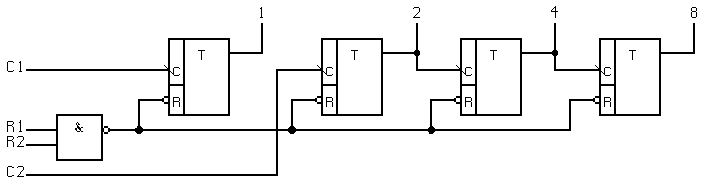

1. Среди систем охранной сигнализации и управления освещением достаточно широко используются датчики движения. Некоторые из них работают на принципе изменения частоты сигнала и весьма чувствительны. Для того чтобы не было ложных срабатываний соответствующих систем, используют так называемые схемы кратности: срабатывание происходит только в том случае, если число импульсов переменной тактовой частоты за заданный интервал времени превышает заданное число. Ниже приведен пример такой схемы, построенной на самом простом счетчике.

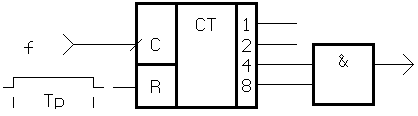

2. Измерение длительности импульсов

Данная схема сбрасывается независимым от измеряемого импульса сигналом.

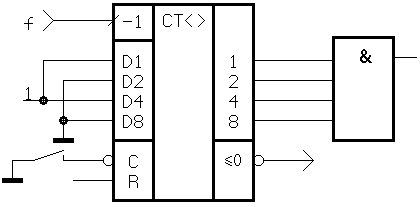

3. Формирователь задержки включения

Сигналом запуска последующей схемы будет уровень лог.0, возникающий по окончании счета на уменьшение. Дальнейшее поступление импульсов на счетный вход –1 запрещается либо этим сигналом, либо прекращением работы внешнего тактового генератора. Для примера показана загрузка по нажатию на кнопку числа 5 – столько тактовых сигналов должно поступить на вход счетчика, чтобы была разрешена работа всего устройства в целом.

Можно использовать нереверсивные счетчики и счетчики, не имеющие входы параллельной загрузки. В этом случае счет следует начинать от нуля, а заканчивать, когда на выходах образуется требуемая комбинация (для этого на приведенной схеме показана схема 4И).

4. Частотомеры. Эти устройства неизбежно строятся на счетчиках, причем чаще всего на двух линейках. Первая линейка работает от опорной высокостабильной высокой частоты (1…10 МГц), построена на десятичных счетчиках и делит опорную частоту в заданное число раз. Это формирователь рабочего интервала счета. Вторая линейка, построенная на синхронных двоичных или десятичных счетчиках, подсчитывает число импульсов измеряемой частоты, поступивших на ее вход за время существования рабочего интервала.