- •Отличительные черты вс четырех поколений.

- •2. Принципы многоуровневой организации вс.

- •3. Структурная организация вс. Принципы Фон-Неймана.

- •4. Архитектура эвм. Архитектура ia-32.

- •7. Структура процессора. Организация алу.

- •8. Структура процессора Intel p6.

- •11. Конвейерная обработка команд. Риски.

- •О ценка производительности идеального конвейера

- •13. Конвейерная обработка команд. Способы разрешения проблемы рисков по управлению.

- •14. Суперконвейерная и суперскалярная обработка машинных команд.

- •15. Параллельная обработка. Классификация по Флинну.

- •16. Параллельная обработка. Параллелизм на уровне команд.

- •17. Параллельная обработка. Параллелизм на уровне процессоров. Оценка эффективности.

- •Векторные компьютеры

- •Мультипроцессоры

- •Мультикомпьютеры

- •18. Параллельная обработка. Сравнение организации многопроцессорных вс (smp, numa, mpp, кластер).

- •19. Параллельные вс. Сети межсоединений.

- •Сети межсоединений

- •20. Сети межсоединений. Топология.

- •21. Сети межсоединений. Коммутация. Буферизация.

- •22. Сети межсоединений. Алгоритмы выбора маршрута. (см. 20 вопрос)

- •23. Устройство управления (уу). Управление работой процессора.

- •24. Уу. Управляющие сигналы.

- •29. Микропрограммное управление. Формат микрокоманды.

- •30. Микрокоманды. Форматы представления адресной информации.

- •33. Зу. Производительность. Физический тип. Иерархия памяти в вс.

- •Производительность зу

- •34. Зу. Методы доступа.

- •Методы доступа

- •35. Внутренняя память. Типы полупроводниковой памяти.

- •36. Структурная организация полупроводниковых зу.

- •37. Полупроводниковые зу. Способы повышения емкости.

- •38. Внутренняя память. Кэш-память.

- •39. Структурная организация оп и кэш-памяти.

- •Функциональные характеристики

- •2. Метод отображения (поиск соответствия между строками кэш и блоками оп)

- •Размер блока оп

- •Алгоритм чтения слова из кэш - памяти

36. Структурная организация полупроводниковых зу.

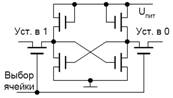

По способу реализации различают статические и динамические запоминающие элементы.

В статических ЗЭ информация

может храниться неограниченно долго

при наличии напряжения питания.

Статический ЗЭ реализуют в виде триггера

с двумя устойчивыми состояниями.

Запоминающий элемент обеспечивает хранение одного бита информации. Для построения

запоминающего устройства большей разрядности используют совокупность ЗЭ, адресные и управляющие входы которых (выборка и управление) объединены. Для получения требуемой емкости ЗУ необходимо использовать несколько банков памяти меньшей емкости. ОЗУ чаще всего строят по блочному принципу, т.е. с использованием нескольких банков. При использовании N банков памяти адрес Аслова ОП преобразуют в пару (n, a), где n – номер банка, а – адрес ячейки внутри банка. Существуют три основные схемы распределения адресных разрядов между n и a.

Схема расслоения памяти (циклическая)

Используется чередование адресов между банками памяти. Чередование обеспечивают за счет циклического разбиения адреса. n= Amod N, a= Adiv N

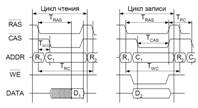

Временные диаграммы работы микросхем памяти DRAM

37. Полупроводниковые зу. Способы повышения емкости.

Полупроводниковые ЗУ в настоящее время представляют собой большой класс запоминающих устройств, различных по своим функциональным и техническим характеристикам, широко используемых в качестве внутренних ЗУ ЭВМ. Но этим их использование не ограничивается. Подавляющее большинство электронной и бытовой техники переходит на цифровые методы представления данных (не только текстовых, но и аудио, графических и видео) и управления (использование микроконтроллеров).Различные сферы применения накладывают свои особенности на реализацию полупроводниковых ЗУ, однако это чаще касается их конструктивных особенностей, а принципы построения одинаковы.Высокое быстродействие полупроводниковых ЗУ обусловливает то, что большинство из них имеет организацию с произвольным доступом. Хотя такие ЗУ, как флэш-память и ЗУ с переносом зарядов (используемые, например, в фото- и видеокамерах), организованы несколько иначе.Это же высокое быстродействие определяет и основные области применения полупроводниковых ЗУ в ЭВМ: кэш-память и оперативная память.

Причем надо отметить, что термин “ЗУ с произвольным доступом” (Random Access Memory – RAM) не соответствует в точности термину “оперативная память”, поскольку первый из них указывает на способ доступа, а второй – на функциональное назначение. И действительно, кэш-память и постоянные ЗУ также являются ЗУ с произвольным доступом. Однако, в соответствии с принятой в русскоязычной литературе терминологией, термин “оперативные ЗУ” ниже иногда используется как синоним ЗУ с произвольным доступом.

Основные виды полупроводниковых ЗУ: статическая и динамическая память с произвольным доступом, постоянная и флэш-память, а также другие виды памяти.

Параметры оценки быстродействия DRAM

tСAS – минимальное время от перепада сигнала СAS (1 ® 0) до момента появления считанных данных на выходе ИС памяти (tСAS » 15 нс);

tPС – минимальное время от начала доступа к одному столбцу микросхемы до момента доступа к следующему столбцу (tPС » 35 нс);

Способы повышения быстродействия ИС памяти

EDO (Extended Data Output – растянутый выход данных). В микросхеме EDO-памяти на выходе установлен буфер-защелка, фиксирующий данные после их извлечения из матрицы памяти при подъеме сигнала CAS и удерживающий их на выходе до

следующего его спада. Это позволило сократить длительность сигнала CAS и соответственно цикл памяти.

Способы повышения быстродействия ИС памяти DDR SDRAM, обеспечивающая двойную скорость передачи данных (DDR – Double или Dual Data Rate), в которой за один такт осуществляются две передачи данных – по

переднему и заднему фронтам каждого синхроимпульса.