- •Лабораторная работа технические средства автоматизации для цифровых систем.

- •Технические средства автоматизации для цифровых систем.. (сост. Доц. Сажин р.А. Пгту 2006 г.)

- •Технические средства автоматизации для цифровых систем.

- •3.1. Логические элементы цифровой автоматики.

- •3.2. Запоминающие элементы цифровой автоматики.

- •3.2.1. Статический «rs» триггер.

- •3.2.2. Динамический «d» триггер.

- •3.2.2. Регистры памяти.

- •3.2.2.1. Параллельный регистр.

- •3.2.2.2. Последовательный регистр.

- •3.2.3. Двоичные счетчики.

- •3.2.4. Шифраторы.

- •3.2.5. Дешифраторы.

- •3.2.6. Мультиплексоры.

- •3.2.8. Распределители..

- •3.9. Сумматоры

- •3.10. Аналого-цифровой преобразователь.

- •3.11. Цифро-аналоговый преобразователь

- •4. Элементы микропроцессорных систем.

- •4.1. Структура микропроцессорных систем.

- •4.1.1. Структура микропроцессора

- •4.1.1.1. Принцип работы микропроцессора при обработке команд.

- •4.1.1.2. Принцип работы микропроцессора при обработке цифровых сигналов.

- •4.1.2. Запоминающие устройства микропроцессорных систем.

- •4.1.2. 1. Оперативное запоминающие устройства.

- •4.1.2. 2. Постоянные запоминающие устройства.

- •Программируемый параллельный интерфейс, параллельные порты микропроцессорных систем.

- •Программируемый таймер.

- •Программируемый последовательный интерфейс, последовательные порты микропроцессорных систем.

4.1.1.2. Принцип работы микропроцессора при обработке цифровых сигналов.

Обработка цифровых сигналов производится в арифметическо-логическом устройстве (АЛУ) микропроцессора. Это устройство может обрабатывать одновременно последовательно два цифровых сигнала. Для этой цели по команде машинного цикла сначала из регистра «W», а потом из «Z» в буфер шины адреса направляются адреса хранения в ОЗУ (или формирования) этих сигналов. Одновременно на шине управления устройством управления и синхронизации микропроцессора выставляется команда «чтение», по которой в шину данных а, затем и в буфер шины данных пересылается сначала один, а затем и другой цифровой сигнал. Эти сигналы из буфера затем последовательно пересылаются для промежуточного хранения вначале в буфер АЛУ, а затем в его аккумулятор. В АЛУ методом арифметического сложения и логических сдвигов производится совместная обработка этих сигналов. Цифровой результат обработки этих сигналов направляется для хранения в аккумулятор. А в регистре признаков отражаются признаки (или флаги) этого результата. К числу этих признаков (флагов) можно отнести: положительность или отрицательность цифрового результата, его четность или нечетность, равенство или неравенство его нулю и т. д. Эти признаки или флаги используются командами ветвления для организации условия этого ветвления алгоритма. Для того чтобы полученный результат не был потерян при обработке последующих сигналов, перед началом этой обработки необходимо переслать результат предыдущей обработки из аккумулятора в один из регистров общего назначения или в ячейку ОЗУ или же в его стековую область.

4.1.2. Запоминающие устройства микропроцессорных систем.

Для хранения информации в микропроцессорных системах используют два вида памяти:

Оперативная в форме ОЗУ (оперативное запоминающие устройство);

Постоянная в форме ПЗУ ( постоянное запоминающие устройство).

4.1.2. 1. Оперативное запоминающие устройства.

Оперативные запоминающие устройства (ОЗУ) или RAM (random access memory -память с произвольным доступом) относятся к энергозависимым устройствам памяти микропроцессорных систем, в которые информация вносится и сохраняется только при условии включения их энергопитания. Основу ОЗУ составляет триггерный запоминающий элемент, схема которого показана на Рис.65.

Этот запоминающий элемент выполнен на основе n-МОП транзисторов, представляющих собой RS-триггер. При хранении битовой информации один из транзисторов Т1 или Т2 находится в открытом состоянии в то время, как другой закрыт. При обращении к этому запоминающему элементу на шине выборки ШВi появляется высокий потенциал. Этот потенциал открывает транзисторные ключи по всей этой шине, в том числе и транзисторы Т3 и Т4, в результате чего на шинах записи-считывания Di, и Di-инверсное появится потенциал (символ ) состояния триггера ЗУ. Таким образом, производится считывание информации через шины Di.

При записи информации в ЗУ шина выборки ШВi остается активной, при этом подача нулевого потенциала на Di-инверсную шину закрывает транзистор Т2

Рис 65. Структура запоминающего элемента оперативной памяти.

подачей на затвор этого транзистора через открытый транзистор Т3 низкого потенциала. При этом высоким потенциалом стока транзистора Т2 транзистор Т1 открывается. Таким образом, для записи символа «0» на инверсную шину Di

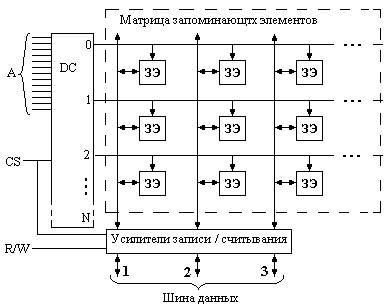

Рис 66. Структура матрицы запоминающих элементов оперативной памяти.

подается низкий потенциал, если же аналогично такой потенциал подать ша прямую шину Di, то в ЗУ запишется символ «1». Считывание состояния триггера ЗУ производится через шины столбцов «Di», которые подключаются к соответствующим усилителям.

Запоминающие элементы ЗУ оперативного запоминающего устройства (ОЗУ) поразрядно собираются в запоминающую матрицу, принципиальная структура которой показана на Рис. 66. В этой матрице шины выборки Швi запоминающих элементов построчно подключены к выходам дешифратора «DС». Обращение к каждой из этих шин производится через адресную шину А дешифратора. Информационные шины Di. запоминающих элементов матрицы группируются в строки, каждая из которых предназначена для конкретного разряда хранимой цифровой информации. Все строки запоминающей матрицы подключены поразрядно к усилителям записи/считывания. Управление процессом работы запоминающей матрицы осуществляется с помощью сигналов CS, R/W , активизация которых обеспечивает включение матрицы в соответствующем режиме работы. Так для записи в матрицу цифрового согнала на ее вход «CS» подается сигнал высокого уровня, и на адресном входе «А» ее дешифратора «DС» выставляется адрес ячейки (строки), в которую необходимо записать двоичное число. Поразрядная запись этого числа производится с шины данных через усилители записи в момент подачи сигнала «W». Аналогично подачей сигнала «R» (чтения) производится вывод на шину данных содержания ячейки матрицы с заданным адресом.

Если дешифратор «DС» плоской двумерной матрицы обозначить как «DСх» и подключить несколько таких матриц сигналами «CSi» к выходам дешифратора «DСу» то получим трехмерную запоминающую матрицу с расширенным ресурсом памяти и с обращением к конкретной ее ячейке через адресные координаты «Ах, Ау».