- •Лабораторная работа технические средства автоматизации для цифровых систем.

- •Технические средства автоматизации для цифровых систем.. (сост. Доц. Сажин р.А. Пгту 2006 г.)

- •Технические средства автоматизации для цифровых систем.

- •3.1. Логические элементы цифровой автоматики.

- •3.2. Запоминающие элементы цифровой автоматики.

- •3.2.1. Статический «rs» триггер.

- •3.2.2. Динамический «d» триггер.

- •3.2.2. Регистры памяти.

- •3.2.2.1. Параллельный регистр.

- •3.2.2.2. Последовательный регистр.

- •3.2.3. Двоичные счетчики.

- •3.2.4. Шифраторы.

- •3.2.5. Дешифраторы.

- •3.2.6. Мультиплексоры.

- •3.2.8. Распределители..

- •3.9. Сумматоры

- •3.10. Аналого-цифровой преобразователь.

- •3.11. Цифро-аналоговый преобразователь

- •4. Элементы микропроцессорных систем.

- •4.1. Структура микропроцессорных систем.

- •4.1.1. Структура микропроцессора

- •4.1.1.1. Принцип работы микропроцессора при обработке команд.

- •4.1.1.2. Принцип работы микропроцессора при обработке цифровых сигналов.

- •4.1.2. Запоминающие устройства микропроцессорных систем.

- •4.1.2. 1. Оперативное запоминающие устройства.

- •4.1.2. 2. Постоянные запоминающие устройства.

- •Программируемый параллельный интерфейс, параллельные порты микропроцессорных систем.

- •Программируемый таймер.

- •Программируемый последовательный интерфейс, последовательные порты микропроцессорных систем.

3.2. Запоминающие элементы цифровой автоматики.

Для запоминания однобитовых двоичных символов «0» или «1» применяют логические устройства, которые называются триггерами. Триггеры могут быть:

Статическими;

Динамическими.

3.2.1. Статический «rs» триггер.

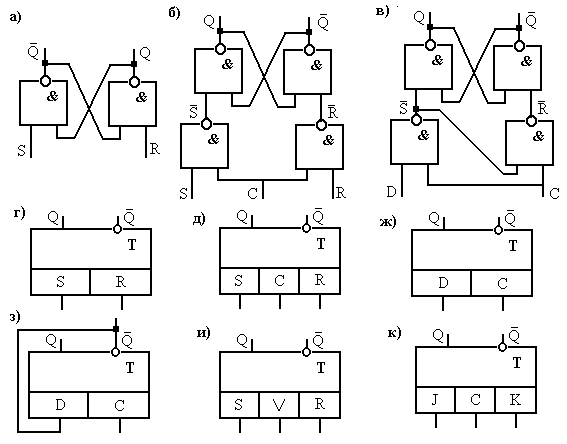

Статический «RS»

триггер может быть выполнен в двух

вариантах: синхронном и асинхронном и

на основе двух элементов И-НЕ, соединенных

по схеме, представленной на Рис 50а для

асинхронного варианта, или собран по

аналогичной схеме из двух элементов

ИЛИ-НЕ. Это логическое устройство имеет

два входа, один из них вход «S»

информационный, а другой «R»

вход обнуления триггера. У триггера два

выхода, один из них «Q»

прямой другой «Q’»

инверсный. В таблица 2 приведены параметры

логического состояния асинхронного

«RS» триггера, выполненного

на основе двух элементов И-НЕ.

Статический «RS»

триггер может быть выполнен в двух

вариантах: синхронном и асинхронном и

на основе двух элементов И-НЕ, соединенных

по схеме, представленной на Рис 50а для

асинхронного варианта, или собран по

аналогичной схеме из двух элементов

ИЛИ-НЕ. Это логическое устройство имеет

два входа, один из них вход «S»

информационный, а другой «R»

вход обнуления триггера. У триггера два

выхода, один из них «Q»

прямой другой «Q’»

инверсный. В таблица 2 приведены параметры

логического состояния асинхронного

«RS» триггера, выполненного

на основе двух элементов И-НЕ.

Таблица 2

S |

R |

Q |

Q’ |

Согласно этой таблице триггер работает как переключатель при подаче на соответствующий вход нуля или единицы. Одновременная подача на входы двух нулей или двух единиц приводит к |

1 |

0 |

1 |

0 |

|

0 |

1 |

0 |

1 |

|

0 |

0 |

1 |

1 |

|

1 |

1 |

запрет |

||

неопределенному (неоднозначному) состоянию этого триггера, поэтому такой режим работы этого триггера нежелателен.

Схема синхронного статического «RS» триггера показана на Рис 50 б, а в таблице 3 приведены параметры его логического состояния. Согласно параметрам этой таблицы синхронный «RS» триггер работает как

Рис 50. Логические схемы а) асинхронно-статического «RS» триггера, б) синхронного «RS» триггера, в) «D» триггера.

Таблица 3

С |

S |

R |

Q |

Q’ |

переключатель и по предыдущей схеме только тогда, когда подается единичный сигнал на его «С» вход. При нулевом состоянии этого входа триггер этого типа выключен из работы , т.е. всегда находится в нулевом состоянии. |

0 |

1 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

1 |

|

1 |

1 |

1 |

запрет |

||

3.2.2. Динамический «d» триггер.

Структура динамического «D» триггера показана на Рис. 50в. Триггер этого типа имеет вход тактового сигнала «С» и информационный вход «D». У этого триггера так же два выхода, один из них «Q» прямой другой «Q’» инверсный. Параметры логического состояния этого триггера приведены в таблице 4..

Таблица 4

С |

D |

Q |

Q’ |

Анализ параметров этой таблицы показывает, что пока на входе «С» сигнал за тактовый цикл не переходит с уровня «0» до уровня «1» информационный вход «D» не влияет на состояние триггера этого типа и он остается в нулевом состоянии. Это свойство данного триггера успешно используется в других цифровых устройствах |

0 |

0 |

0 |

1 |

|

0 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

|

1 |

0 |

1 |

0 |

|

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

1 |

|

1 |

0 |

0 |

1 |

Обычно на принципиальных схемах цифровых устройств триггеры изображают с помощью фигур, представленных на Рис. 50 (г-к). На рисунке 50г показана схема асинхронного «RS» триггера, на рисунке 50д синхронного «RS» триггера и на Рис 50ж «D» триггера. Если инверсный выход«Q’» «D» триггера соединить с его «D» входом то получим триггер с особыми свойствами Рис 50з. Такой триггер называют переключающим «Т» триггером, который за который за каждый тактовый цикл меняет свое состояние на противоположное. На принципиальных схемах цифровых систем этот триггер представлен в виде показанном на Рис.50и. На рис 50к. показана схема универсального «JK» триггера, свойства которого зависят соотношения входов «J» и «K».