- •Лабораторная работа технические средства автоматизации для цифровых систем.

- •Технические средства автоматизации для цифровых систем.. (сост. Доц. Сажин р.А. Пгту 2006 г.)

- •Технические средства автоматизации для цифровых систем.

- •3.1. Логические элементы цифровой автоматики.

- •3.2. Запоминающие элементы цифровой автоматики.

- •3.2.1. Статический «rs» триггер.

- •3.2.2. Динамический «d» триггер.

- •3.2.2. Регистры памяти.

- •3.2.2.1. Параллельный регистр.

- •3.2.2.2. Последовательный регистр.

- •3.2.3. Двоичные счетчики.

- •3.2.4. Шифраторы.

- •3.2.5. Дешифраторы.

- •3.2.6. Мультиплексоры.

- •3.2.8. Распределители..

- •3.9. Сумматоры

- •3.10. Аналого-цифровой преобразователь.

- •3.11. Цифро-аналоговый преобразователь

- •4. Элементы микропроцессорных систем.

- •4.1. Структура микропроцессорных систем.

- •4.1.1. Структура микропроцессора

- •4.1.1.1. Принцип работы микропроцессора при обработке команд.

- •4.1.1.2. Принцип работы микропроцессора при обработке цифровых сигналов.

- •4.1.2. Запоминающие устройства микропроцессорных систем.

- •4.1.2. 1. Оперативное запоминающие устройства.

- •4.1.2. 2. Постоянные запоминающие устройства.

- •Программируемый параллельный интерфейс, параллельные порты микропроцессорных систем.

- •Программируемый таймер.

- •Программируемый последовательный интерфейс, последовательные порты микропроцессорных систем.

Программируемый последовательный интерфейс, последовательные порты микропроцессорных систем.

Обмен информацией в параллельном коде через параллельные порты (интерфейсы) может быть успешно применен только внутри микропроцессорной системы. Обмен информацией между микропроцессорными системами по этому принципу требует большого количества проводов, т.к. каждый разряд числового сигнала должен по этому принципу передаваться по отдельному проводу. Кроме того требуют дополнительных проводов сигналы согласования скорости приема и передачи этих сигналов. Проблема обмена информации между двумя или несколькими микропроцессорными системами успешно решается с применением последовательного кода (способа) передачи цифровых сигналов заданной разрядности, по которому в однопроводной линии связи ЛС цифровые двоичные

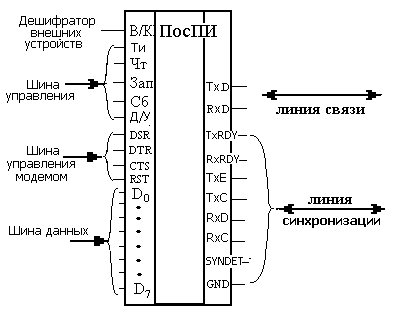

Рис.72. Структура связи ПосПИ с управляющим микропроцессором через систему шин и с другим микропроцессором через линию связи.

символы появляются в виде заданной последовательности, которые проявляются в виде наличия или отсутствия импульсов, заданной амплитуды и частоты. Для реализации такого способа передачи цифровой информации применяются устройства, которые называются последовательными интерфейсами (последовательными портами).

Последовательный программируемый интерфейс ПосПИ как структурный блок микропроцессорной системы работает независимо от самого микропроцессора по собственной программе, представленной в виде управляющего слова. Структура связей ПосПИ с управляющим микропроцессором и с другим микропроцессором по линии связи показана на Рис.72.

Последовательный интерфейс ПосПИ

связан с микропроцессором .только через

шину данных «ШД» и шину управления

«ШУ». Причем в шину управления введены

дополнительные связи для управления

работой модема. Вход «В/К» используется

аналогично для включения ЧИПа (микросхемы)

в работу через сигнал дешифратора

внешних устройств.

Последовательный интерфейс ПосПИ

связан с микропроцессором .только через

шину данных «ШД» и шину управления

«ШУ». Причем в шину управления введены

дополнительные связи для управления

работой модема. Вход «В/К» используется

аналогично для включения ЧИПа (микросхемы)

в работу через сигнал дешифратора

внешних устройств.

С противоположной микропроцессорной системой данная система соединяется по линии связи ЛС, в которой выделяются две линии – линия передачи данных и линия синхронизации этой передачи. Данная схема ПосПИ представляет синхронную систему последовательной передачи данных, в которой обе микропроцессорные системы взаимно согласуются по частоте взаимного обмена цифровой информацией. Принцип работы такой системы рассмотрим на примере структуры, представленной на Рис.73.

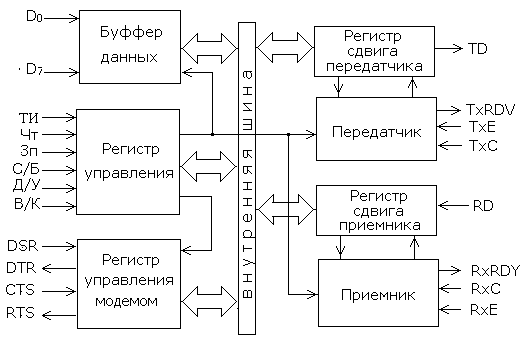

Все структурные элементы последовательного интерфейса связаны внутренней шиной, к которой с одной стороны примыкают буфер шины данных, регистр управления и регистр управления модемом, а с другой к этой шине примыкают регистры сдвига приемо-передатчика

Буфер шины данных предназначен для промежуточного хранения цифровых сигналов перед их передачей в шину данных или из нее во внутреннюю шину ПосПИ. По команде запись «Зп» этот интерфейс пересылаеив буфер данных сигналы из системной шины данных и посылает в эту шину сигналы по команде чтение «Чт».

Регистр управления связан с системной шиной управления по следующим входам:

ТИ – тактовая частота системы;

Чт - команда чтение;

Зп - команда запись;

С/Б – команда сброс;

Д/У - команда , указывающая на тип передаваемых данных (данные или

команда управления);

В/К – команда включения ЧИПа (микросхемы) в работу;

Регистр управления модемом последовательного интерфейса связан с системной шиной управления по следующим входам:

DSR – Сигнал готовности передатчика к передаче данных;

DTR – Сигнал запроса на прием информации;

RTS – Сигнал готовности к приему информации;;

CTS – Сигнал разрешения передачи информации

Передача информации в линию связи производится сигналом «TD», который появляется на выходе регистра сдвига передатчика. В свою очередь передатчик согласует свою работу с приемником противоположного последовательного порта через сигналы:

TxRDY – Сигнал готовности передатчика принять символ данных от процессора в

шину данных;

TxE – Сигнал «буфер шины данных пустой»;

TxC – Сигнал синхронизации передатчика с приемником.

Рис. 73. Внутренняя структура программируемого последовательного интерфейса .

Прием информации из линии связи в регистр сдвига приемника производится сигналом «RD». В свою очередь приемник согласует свою работу с передатчиком противоположного последовательного порта через сигналы:

RxRDY – Сигнал готовности приемника передать символ данных процессору через

шину данных;

RxE – Сигнал «буфер шины данных полный»;

RxC – Сигнал синхронизации приемника с передатчиком.

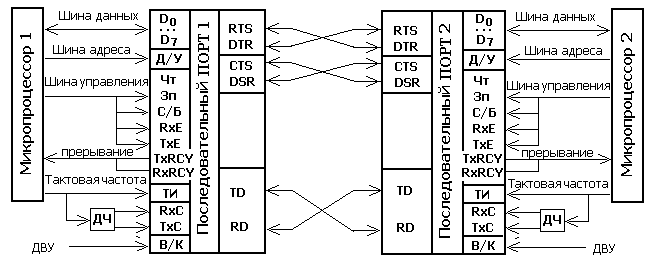

Выше изложенная структура последовательного интерфейса относится к интерфейсам синхронного действия, в которых обе микропроцессорные системы согласованы по тактовому сигналу. Структура синхронной взаимосвязи двух микропроцессорных систем показана на Рис.74.

Рис.74 Структура синхронной взаимосвязи двух микропроцессорных систем

Принцип взаимной передачи информации по этой схеме состоит в следующем. Ведущий микропроцессор по уровню сигналов TxRDY и TxE опрашивает состояние передатчика и буфера шины данных, после чего выставляет на шине данных цифровой сигнал, одновременно с этим подает на шину управления команду «запись». По этой команде сигнал данных запишется в буфер шины данных последовательного порта 1 (ведущего микропроцессора), после чего последовательный порт (интерфейс) работает независимо от микропроцессора по собственной программе (управляющему слову). При заполнении регистра сдвига передатчика сигналом данных формируется команда DSR, которая передается на вход CTS последовательного порта 2 (ведомого микропроцессора), Если регистр сдвига последовательного порта 2 (ведомого микропроцессора) пуст, то он формирует команду RTS, которая передается на вход DTR последовательного порта 1 (ведущего микропроцессора). В результате этого происходит передача данных по перекрестным каналам TD и RD становится возможным и приемник последовательного порта 2 (ведомого микропроцессора)включается в работу, поэтому его регистр сдвига последовательно заполняется битами данных цифрового сигнала (Рис.73) с тактовой частотой. TxС. При полном заполнении этого регистра формируется сигнал RxE, который переводит последовательный порта 2 в режим связи с ведомым микропроцессором. По этой команде содержимое регистра сдвига приемника пересылается в буфер шины данных последовательного порта 2, а затем по команде «чтение» оно переносится через шину данных в микропроцессор 2. В это время по команде RxRDY микропроцессор 2 приостанавливает выполнение операций не связанных с приемом сигнала данных.

Таким образом, передатчик

последовательного порта 1 ведущего

микропроцессора всегда согласован в

работе с приемником последовательного

порта 2 ведомого микропроцессора, также

как буферы системных шин обеих портов

согласованы в работе. При достижении

этой согласованности порты синхронно

с одинаковой тактовой частотой сигнала

TxС совершают обмен

информацией по перекрестным каналам

TD и RD. При этом

как показано на Рис. 75. структура кадра

передачи инфромации по этим каналам

выглядит следующим образом..

Таким образом, передатчик

последовательного порта 1 ведущего

микропроцессора всегда согласован в

работе с приемником последовательного

порта 2 ведомого микропроцессора, также

как буферы системных шин обеих портов

согласованы в работе. При достижении

этой согласованности порты синхронно

с одинаковой тактовой частотой сигнала

TxС совершают обмен

информацией по перекрестным каналам

TD и RD. При этом

как показано на Рис. 75. структура кадра

передачи инфромации по этим каналам

выглядит следующим образом..

Рис. 75. Структура кадра передачи инфромации по каналам последовательной

связи.

Информация в линии связи передается побиино следующим образом. В период паузы в лини связи всегда устанавливается уровень логической единицы, что снижает вероятность появления помех. Признаком начала передачи данных является переход сигнала с высокого уровня на низкий в течении периода одного такта. Такой информационный импульс называется стартовым битом, после которого следует последовательная совокупность битов данных (обычно по числу импульсов кратных восьми). В конце информационных битов следует бит проверки четности, за которым следуют стоп биты, фиксирующие конец кадра данных, а затем в линии связи вновь наступает период паузы.

Работа последовательного интерфейса (порта) в синхронном режиме связана с определенными недостатками, главным из которых является необходимость тактовой согласованности передающего (ведущего) и принимающего (ведомого) микропроцессоров, что не всегда возможно. Устранение этого недостатка возможно при использовании асинхронного принципа последовательной передачи данных, суть которого состоит в том, что в процессе передачи данных оба микропроцессорных устройства (ведущий и ведомый) осуществляют взаимопроверку состояния приемопередатчиков. В случае опережения в работе одного из этих микропроцессоров подается команда на прерывание (остановку) его работы или переключение его на другие программные операции до тех пор, пока смежный (медленный) микропроцессор не сравняется с ним по тактовым операциям передачи данных. В этом режиме оба микропроцессора могут работать на разной тактовой частоте, но обязательно с взаимопроверкой согласованности результата. Асинхронный программируемый последовательный интерфейс (порт) имеет структуру устройства типа UART (Универсальный Асинхронный Ридер-Транслятор).