- •Комп’ютерна схемотехніка

- •1. Реалізація операції додавання

- •1.1. Початкові дані

- •1.2. Елементна база — інтегральні схеми ттлш серій к1531,кр1533

- •1.3. Алгоритм додавання двійкових чисел

- •1.4. Функціональна схема алп для виконання операції додавання

- •1.5. Мікропрограма додавання

- •1.6. Принципіальна схема модуля операційного блока

- •1.7. Проектування модуля керуючого блока

- •1.8. Характеристики алп

- •2. Реалізація операції віднімання

- •2.1. Початкові дані

- •2.2. Алгоритми віднімання двійкових чисел

- •2.3. Функціональна схема алп для виконання операції віднімання

- •2.4. Мікропрограма віднімання

- •2.5. Принципіальна схема модуля операційного блока

- •2.6 Проектування модуля керуючого блока

- •Реалізація операцій додавання і віднімання

- •3.1. Початкові дані

- •3.2. Алгоритми додавання і віднімання двійкових чисел

- •Функціональна схема алп для виконання операцій

- •3.4. Мікропрограма додавання та віднімання двійкових чисел

- •3.5. Принципіальна схема модуля операційного блока

- •3.6. Проектування модуля керуючого блока

- •4. Реалізація операції множення

- •4.1. Початкові дані

- •4.2. Алгоритм множення двійкових чисел із зсувом суми часткових добутків вправо

- •4.3. Функціональна схема алп для операції множення

- •4.4. Мікропрограма множення цілих чисел

- •4.5. Модуль операційного блока для множення цілих чисел

- •4.6. Модуль керуючого блока

- •4.7. Принципільна схема модуля керуючого блока

- •5. Реалізація операції ділення

- •5.1. Початкові дані

- •5.2. Алгоритм ділення цілих чисел

- •5.3. Функціональна схема алп для мікропрограми ділення

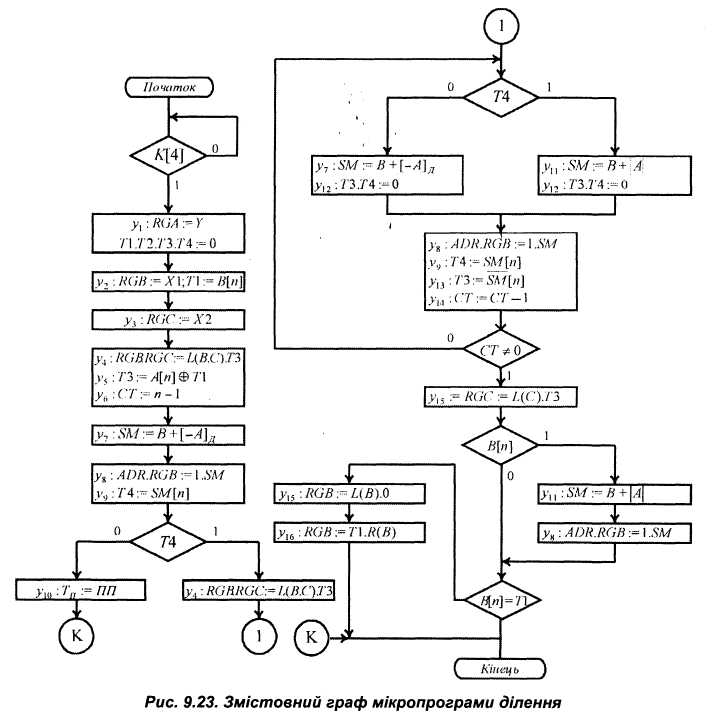

- •5.4. Мікропрограма ділення цілих чисел без відновлення залишку

- •5.5. Принципіальна схема модуля операційного блока для мікропрограми ділення

- •5.6. Схема другого рівня керування операційним блоком

- •7. Принципіальна схема автомата Мілі для операції ділення

- •Умовне графічне позначення вхідних комутаторів

- •Умовне графічне позначення дворозрядного

- •Умовне графічне позначення 4-розрядного

5.3. Функціональна схема алп для мікропрограми ділення

Функціональну схему АЛП для виконання мікропрограми ділення показано на рис.22.

Схема АЛП містить:

регістр RGA для приймання восьмирозрядного дільника Y;

регістри RGB і RGC для приймання 16-розрядного діленого X;

комбінаційний восьми розрядний суматор SM;

мультиплексор MUX, який забезпечує записування інформації в регістр RBG із вхідної шини Ш1 або з виходів суматора SM;

схему BIN для подання прямого або оберненого коду дільника на входи суматора SM;

лічильник кількості циклів CT;

Рисунок

22 – Функціональна схема АЛП для операції

ділення

схему вироблення ознак результату ОР;

тригери T1 – T4 для створення другого рівня керування модулем операційного блока МОБ5;

місцевий керуючий блок МКБ5 на основі автомата Мілі з пам’яттю на JK – тригерах.

5.4. Мікропрограма ділення цілих чисел без відновлення залишку

Початок. Якщо К[4], то М1, інакше – чекати

М1 у1: RGA := Y; T1.T2.T3.T4 := 0.0.0.0 < завантаження дільника обнуління тригерів >

у2: RGB := Х1; T1 := B[n] < завантаження старшої частини діленого; присвоєння тригеру Т1 знака діленого >

у3: RGC := Х2 < завантаження молодшої частини діленого>

у4: RGB.RGС := L(B.C).T3 < зсув вліво на один розряд змісту регістрів RGB і RGС. Передача значення старшого розряду регістра RGС в молодший розряд регістра RGB, а в молодший розряд RGС – змісту тригера Т3 >

у5: T3 := ЗНАК = А[n] Т1 < записування в тригер T3 знака результату ділення>

у6: СT := n -1 < завантаження в лічильник СТ кількості циклів>

у7 : SM := B + [-A]Д < віднімання дільника в доповняльному коді від значення даних в регістрі RGB >

у8 : ADR.RBG := 1.SM < завантаження результату віднімання в регістр RBG . Входу адресації ADR мультиплексора MUX надається значення одиниці>

у9: T4 := SM[n] < присвоєння знака залишку тригера T4 >

Якщо T4, то М2 , інакше

у10: TП := ПП < присвоєння ознаки переповнення тригеру TП в ЦПК >.

Перейти до М7 (кінець)

М2 у4: RGB.RGС := L(B.C).T3 .

М3 Якщо T4, то М4 , інакше

у7 : SM := B + [-A]Д

у12: T3.T4 = 0.0 < обнуління тригерів T3,T4 >

Перейти до М5

М4 у11: SM := B + [A] < додавання дільника до залишку >

у12: T3.T4 = 0.0

М5 у8 : ADR.RBG := 1.SM

у9: T4 := SM[n]

у13:

T3

:=

![]() < присвоєння тригеру T3

інверсного значення знака суматора –

формування цифри частки >

< присвоєння тригеру T3

інверсного значення знака суматора –

формування цифри частки >

у14: СT := СT -1 < декремент змісту лічильника>

Якщо СT ≠ 0, то М3, інакше М8

М8 у15 := RGС := L(С).Т3 < зсув вліво змісту регістра RGС і записування останньої молодшої цифри частки >

Якщо

![]() ,

то М6

, інакше

,

то М6

, інакше

у11: SM := B + [A]

у8 : ADR.RBG := 1.SM

М6 Якщо В[n] = T1, то М7, інакше

у15 := RGВ := L(В.0) < зсув вліво залишку >

у16 := RGВ := Т1. R (В) < зсув вправо частки і присвоєння їй знака діленого >

М7 Кінець.

Змістовний і закодований графи мікропрограми ділення показано на рис.23 і рис.24.

Рисунок

23 – Змістовний граф мікропрограми

ділення

Рисунок

24 – Закодований і розмічений граф

мікропрограми ділення