- •1. Введение

- •2. Базовые понятия

- •2.1 Что такое pld, fpga и asic

- •2.2 Принципиальная структура fpga

- •2.3 Что такое hdl. Распространенные hdl

- •2.4 Понятие уровней абстракции и иерархии в проектировании аппаратуры

- •2.4.1 Уровни абстракции

- •2.4.2 Понятие проекта. Составные части проекта. Иерархия проекта.

- •2.5 Маршрут проектирования цифровых схем для реализации на fpga

- •2.6 Функциональное тестирование

- •2.7 Процесс синтеза

- •2.8 Процесс имплементации и создания конфигурационного файла

- •2.9 Понятия «система на кристалле» и ip-ядро

- •3. Специфика проектирования цифровых устройств для fpga с использованием средств фирмы Xilinx

- •3.1 Обзор семейств fpga и средств проектирования фирмы Xilinx

- •3.1.1 Обзор семейств fpga фирмы Xilinx

- •3.2 Обзор семейства fpga Spartan 6

- •3.3 Структура логической ячейки fpga на примере семейства Spartan 6

- •3.4 Дополнительные ресурсы fpga фирмы Xilinx на примере семейства Spartan 6

- •3.4.1 Блочная память (Block ram)

- •3.4.2 Аппаратные блоки умножения

- •3.4.3 Контроллер памяти (Memory Controller Block)

- •3.4.4 Контроллер pci Express

- •3.4.5 Гигабитные приемопередатчики (Gigabit Transceiver)

- •3.4.6 Блоки ввода-вывода

- •3.5 Понятие глобальных временных ограничений

- •3.6 Генерация ip-блоков

- •3.7 Моделирование проектов. Обзор isim

- •3.8 Внутрисхемная отладка проектов. Обзор ChipScope

- •3.9 Обзор микроконтроллеров класса «soft-core»

- •4. Проектирование аппаратуры с использование языка Verilog hdl

- •4.1 Понятие модуля. Базовая структура модуля

- •4.1.1 Объявление портов ввода-вывода.

- •4.1.2. Объявление внутренних сигналов, параметров или переменных.

- •4.1.3. Тело модуля

- •4.2 Реализация комбинационных схем вентильного уровня

- •4.3 Реализация модульной структуры проекта

- •4.4 Конструкции для реализации комбинационных схем уровня rtl

- •4.4.1 Операторы

- •4.4.2 Блок always

- •4.5 Реализация комбинационных схем уровня rtl

- •4.5.1 Модифицированное описание 1-битного компаратора

- •4.5.2 Описание двоичного дешифратора

- •4.5.3 Описание блока алу

- •4.6 Конструкции для реализации последовательных схем уровня rtl

- •4.6.1 Триггер d-типа

- •4.6.2 Регистр

- •4.6.3 Регистровый файл

- •4.7 Реализация последовательных схем

- •4.7.1 Двоичный счетчик

- •4.7.2 Стек

- •4.8. Константы и параметры. Проектирование ip-блоков

- •4.8.1. Константы

- •4.8.2. Параметры

- •4.9 Конструкции для реализации конечных автоматов. Автоматы Мура и Мили

- •4.10. Реализация конечных автоматов

- •5. Функциональное тестирование аппаратуры средствами языка Verilog hdl

- •5.1 Базовая структура тестового окружения

- •5.2 Описание настроек моделирования

- •5.3 Тестовые последовательности и блок initial

- •5.4 Описание генератора тактового сигнала

- •5.5 Вспомогательные конструкции

- •5.5.2 Циклы

- •5.5.3 Ожидание событий и состояний

- •5.5.4 Системные функции

- •5.6 Реализация законченного тестового окружения

- •6. Лабораторные работы

- •6.1 Лабораторная работа №1 Создание проекта и выполнение всего маршрута проектирования в среде проектирования ise фирмы Xilinx

- •Введение

- •Описание задачи

- •Выполнение работы

- •Проекты для самостоятельной работы

- •Заключение

- •6.2 Лабораторная работа №2 Проектирование простых комбинационных схем. Моделирование проекта

- •Введение

- •Описание задачи

- •Выполнение работы

- •Проекты для самостоятельной работы

- •Заключение

- •6.3 Лабораторная работа №3 Проектирование простых последовательных схем. Реализация тактирования

- •Введение

- •Описание задачи

- •Выполнение работы

- •Проекты для самостоятельной работы

- •Заключение

- •6.4 Лабораторная работа №4 Проектирование конечных автоматов

- •Введение

- •Описание задачи

- •Выполнение работы

- •Проекты для самостоятельной работы

- •Заключение

- •6.5 Лабораторная работа №5 Проектирование устройств, содержащих ip-блоки

- •Введение

- •Описание задачи

- •Выполнение работы

- •Проекты для самостоятельной работы

- •Заключение

- •7. Приложение

- •7.1 Краткое описание лабораторного макета Atlys

- •8. Рекомендуемая литература

Проекты для самостоятельной работы

Добавить флаг нулевого результата для операций сложения и вычитания. При этом значение флага будет отображаться на одном из светодиодов, расположенном на тестовой плате Atlys;

Добавить операции логического сдвига влево и вправо на один разряд;

Реализовать операции сложения и вычитания на одном и том же сумматоре.

Заключение

По окончании данной лабораторной работы вы получили представление о конструкциях языка Verilog HDL, используемых для описания комбинационных схем. Также вы научились создавать базовые тестовые окружения для разрабатываемых блоков и осуществлять процесс моделирования. Кроме этого вы получили навыки работы с временными диаграммами для анализа корректности функционирования разрабатываемых модулей.

6.3 Лабораторная работа №3 Проектирование простых последовательных схем. Реализация тактирования

Цель работы: изучение принципов построения цифровых схем, содержащих элементы памяти, изучение возможностей языка Verilog HDL по описанию последовательных схем, реализация тактирования в FPGA и использование глобальных временных ограничений.

После выполнения работы вы:

научитесь пользоваться операторами и конструкциями языка Verilog HDL для создания последовательных схем;

научитесь проектировать цифровые устройства, содержащие память;

получите представление о глобальных временных ограничениях;

получите базовое представление об утилите Core Generator;

научитесь реализовывать тактирование в FPGA.

Введение

Целью данной лабораторной работы является получение базового представления о проектировании цифровых устройств, содержащих в своем составе элементы памяти. При этом в ходе работы над предлагаемым проектом будут использоваться конструкции языка и шаблоны, служащие для описания триггеров и регистров. Описание подобных элементов памяти базируется на блоках always, «срабатывающих» по некоторым событиям, основанным на переключении тактового сигнала (posedge, negedge). Реализация самого тактового сигнала в свою очередь предполагает использование специальных встроенных в FPGA блоков, таких как CMT (содержащих в своем составе блоки DCM и PLL). Доступ к подобным встроенным блокам осуществляется через специальную утилиту, называющуюся Core Generator.

Как и в предыдущих лабораторных работах, в ходе выполнения работы, будут получены как результаты моделирования, так и полностью функционирующее устройство, реализующее поставленную задачу.

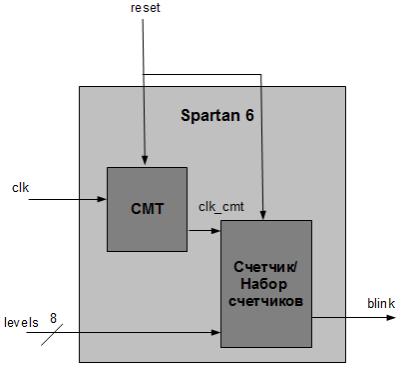

Описание задачи

Задачей данной лабораторной работы будет являться создание блока, изменяющего свои выходные сигналы с определенной частотой. В текущей реализации, такой блок будет иметь единственный выходной сигнал, разрядностью в 1 бит, который будет инвертировать свое значение раз в секунду. Кроме этого, данный блок будет поддерживать 8-ми разрядный входной сигнал, отвечающий за увеличение частоты изменения выходного сигнала. Т. е. чем больше значение будет подано на вход блока, тем чаще будет происходить изменение выходного сигнала.

Входное 8-ми разрядное значение будут задаваться с помощью 8-ми переключателей. При этом выходной 1-но разрядный сигнал будет соединен с любым из светодиодов, расположенных на плате Atlys. Также в проекте потребуется реализовать тактовый сигнал и сигнал асинхронного или синхронного сброса всех триггеров.

При этом главной задачей проекта будет являться наблюдение мигания светодиода с различной, зрительно различимой, частотой.

Ядром данного проекта будет служить обыкновенный счетчик. Также проект будет содержать аппаратный блок CMT для реализации тактирования. Структурная схема проекта этой лабораторной работы представлена на рисунке 6.3.1.

Рисунок

6.3.1 — Структурная схема проекта

лабораторной работы №3

Рисунок

6.3.1 — Структурная схема проекта

лабораторной работы №3