- •146 Цифровая схемотехника Конспект цифровая схемотехника

- •2. Формирователи прямоугольных импульсов

- •10. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы.

- •1.2 Прохождение импульсов через rc-цепи.

- •1.2.1 Напряжение и ток в rc-цепях под воздействием единичного скачка.

- •1.2.2 Дифференцирующая (укорачивающая) и разделительная rc-цепи.

- •1.2.3 Реальные rc-цепи при импульсном воздействии.

- •1.3 Фиксаторы уровня в дифференцирующих rc-цепях.

- •1.4 Интегрирующие rc-цепи.

- •Погрешности интегрирующей цепи:

- •2. Формирователи прямоугольных импульсов

- •2.1 Диодные ограничители последовательного и параллельного типа.

- •2.2 Линейные модели транзистора в режиме большого сигнала.

- •2.3 Расчет транзисторных ключей.

- •2.4 Транзисторный усилитель ограничитель.

- •2.5 Динамические характеристики транзисторных ключей.

- •3. Мультивибраторы

- •3.2 Транзисторный мультивибратор. Принцип действия, осциллограм-мы работы мультивибратора

- •3.3 Расчет периода колебаний мультивибратора

- •3.4 Регулировка частоты, термостабилизация и улучшение формы выходного напряжения мультивибратора.

- •3.5 Транзисторный одновибратор. Принцип действия, осциллограммы.

- •4. Потенциальные логичекие элементы

- •4.2 Диодная логика. Логика «и»

- •Логика «или»

- •Недостатки диодной логики: схемы критичны к внутреннему сопротивлению источников эдс (), обладают нестабильными уровнями логического «0» и «1».

- •4.3 Диодно-транзисторная логика (дтл)

- •4.4 Транзистор-транзисторная логика (ттл)

- •4.5 Логические элементы на моп и кмоп-структурах.

- •5.1 Мультивибраторы на потенциальных логических элементах.

- •5.2 Одновибраторы на потенциальных логических элементах.

- •5.2 Одновибраторы на потенциальных логических элементах.

- •Расчет длительности импульса одновибратора.

- •6.1 Кодирование временных интервалов.

- •6.2 Кодирование напряжение.

- •6.3 Аналогово-цифровые преобразователи (ацп). Основные характеристики и параметры.

- •6.3.1 Ацп на параллельных компараторах;

- •6.3.2 Ацп поразрядного кодирования.

- •6.4 Цифро-аналоговые преобразователи (цап). Структура, основные характеристики и параметры.

- •6.4.1 Взвешенная схема, управляющая напряжением.

- •6.5 Устройство выборки хранения.

- •7.1 Общая характеристика и принципы построения глин.

- •7.2 Автоколебательные глин на транзисторах.

- •7.3 Ждущие глин на транзисторах.

- •7.4 Глин на оупт.

- •8.2 Автоколебательный блокинг-генератор.

- •8.3 Ждущий блокинг-генератор.

- •8.4 Синхронизация блокинг-генератора.

- •9.1 Оперативные запоминающие устройства (озу) с произвольным доступом.

- •9.2 Статические и динамические зу.

- •9.3 Построение плат памяти.

- •9.4 Программируемые запоминающие устройства (пзу).

- •10. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы.

- •10.2 Программируемые логические матрицы (плм).

- •10.2.1 Схемотехника плм

- •10.2.2 Подготовка задачи к решению с помощью плм

- •10.2.3 Программирование плм

- •10.2.4 Упрощенное изображение схем плм

- •10.2.5 Воспроизведение скобочных форм переключательных функций

- •10.2.6 Наращивание (расширение) плм

9.2 Статические и динамические зу.

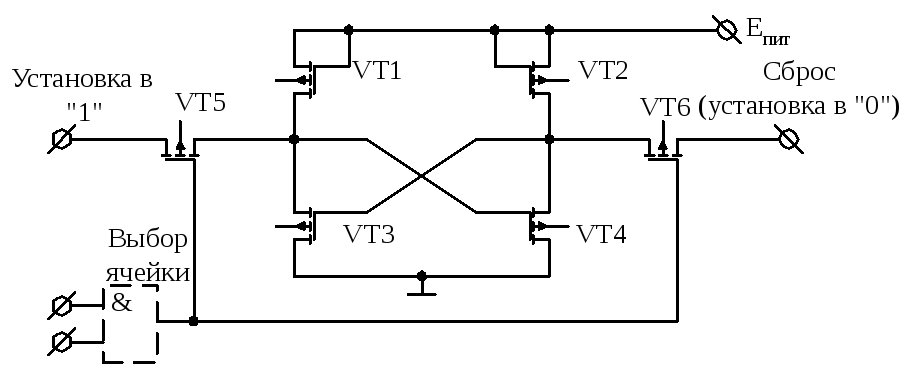

Упрощенная схема ячейки статической МОП памяти приведена на рис. 9.2.

Рис. 9.2. Упрощенная схема ячейки статической МОП памяти

Сигнал выборки ячейки формируется схемой «И», на входы которой поступают сигналы логической «1» с выходов дешифраторов строк и столбцов.

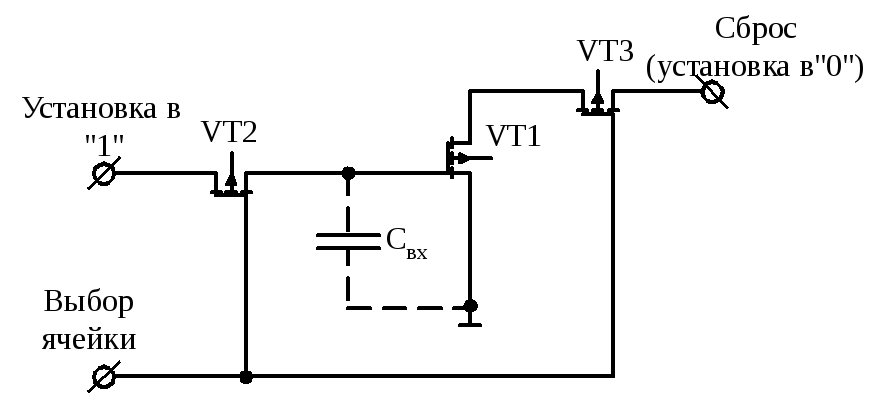

Схема динамической памяти приведена на рис. 9.3.

Рис. 9.3 Упрощенная схема ячейки динамической МОП памяти

Ячейка динамической памяти имеет вдвое меньше МОП-транзисторов и занимает вдвое меньшую площадку на кристалле. Запоминающий элемент — входная емкость транзистора VT1 Свх. Благодаря большому входному сопротивлению Rвх МОП-транзисторов (Rвх10Мом, Свх510пФ) получаем постоянную времени разряда 10mc, в связи с этим данные необходимо регенерировать (перезаписывать) через время порядка 25 mc. Для этой цели служит специальная дополнительная схема. Она автоматически обращается поочередно к столбцам, обеспечивая регенерацию данных во всех ячейках. Обращение к ячейки возможно при наличии отпирающего напряжения на транзисторах VT2, VT3 сигналом «выбор ячейки».

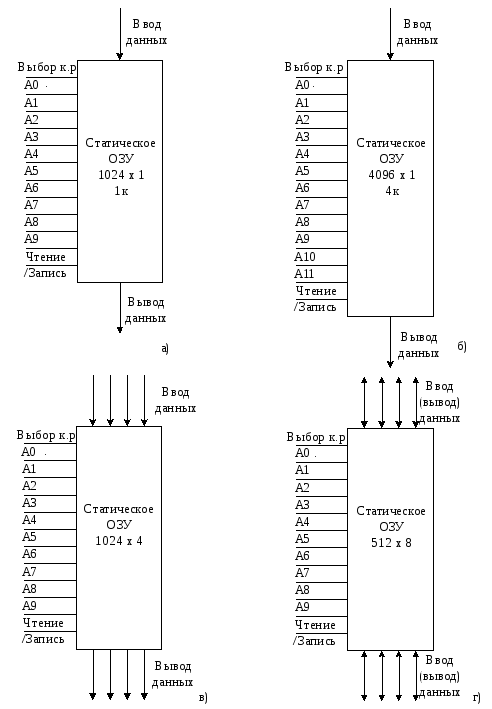

На рис. 9.4. представлены 4 варианта организации структуры интегральных схем статической памяти.

При 10 адресных линий А0-А9, имеем возможность адресовать 210=1024 ячейки. Сигнал «выбор кристалла» — используется для задания одного из двух рядов памяти составленных из таких ИМС. Для организации памяти объемом 1КБайт требуется 8 таких ИМС (8х1024). Используя входы «выбор кристалла» можно организовать 2 линейки памяти (2048х8 разрядных слов).

В ИМС имеются шины или линии ввода и вывода данных. Линия чтение/запись — при подаче логической «1» обеспечивает чтение данных, при подаче логического «0» — запись.

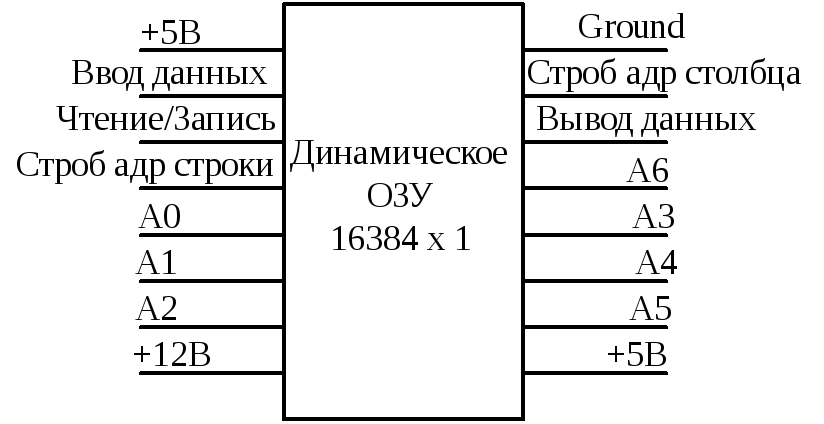

На рис. 9.5. представлено динамическое ОЗУ объемом 4к, 16к, 64к в корпусе DIP на 16 выводов.

Рис. 9.5. Динамическое ОЗУ объемом 4к, 16к, 64к.

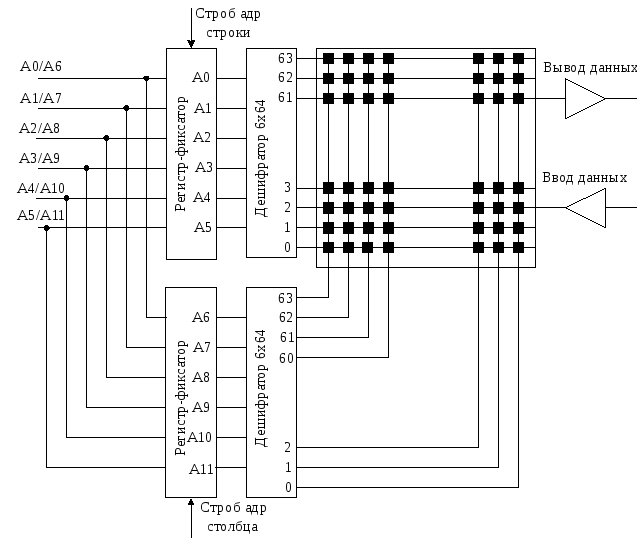

Для уменьшения числа внешних выводов используется применения сигналов строба адреса строки и строб адреса столбца. Такой прием называется адресацией с мультиплексированием.

На рис. 9.6. показана схема, поясняющая метод адресации с мультиплексированием. Для памяти 4к используют дешифраторы столбца и строки, каждый из которых должен иметь 6 входов и 64 выхода. На входе каждого дешифратора стоит 6 разрядный регистр-фиксатор. Для адресации ячейки в таком ЗУ необходимо затратить 2 временных цикла.

Рис. 9.4. Варианты организации структуры интегральных схем статической памяти

На 6 адресных входов поступают сигналы с 6 линий: младшая часть адреса (А0-А5), после чего поступает сигнал строб адреса строки, по которому эти 6 разрядов адреса записываются в регистр-фиксатор дешифратора адреса строки, затем 6 старших разрядов адреса (А6-А11) записываются в регистр-фиксатор дешифратора адреса столбца по сигналу строб адреса столбца. После этого цикла в регистрах-фиксаторах хранится 12 разрядный адрес, что дает возможность выбрать одну из 4096 ячеек памяти.

Рис. 9.6. Схема адресации с мультиплексированием

9.3 Построение плат памяти.

В разделе 9.2 были рассмотрены ИМС для построения статических и динамических ЗУ. Возникают вопросы, какие дополнительные ИМС должны быть на плате памяти? Как организуется ее работа?

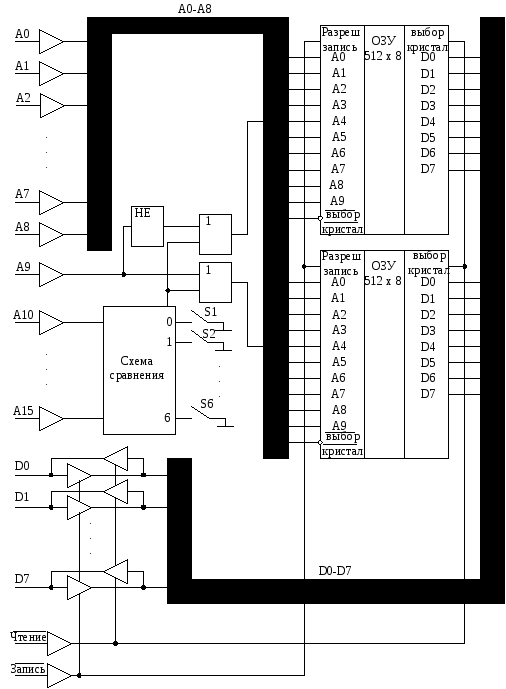

На рис. 9.7. представлена упрощенная структурная схема памяти небольшой МП системы. Для построения памяти 1кБ применены 2 ИМС по 512х8 разрядных слов каждая. В зависимости от структуры шины конкретной МП системы, примененных схем памяти для построения реальной системы (платы памяти) требуется дополнительные ИМС.

А0-А15 — адресные линии памяти.

А0-А9 — внутренняя шина (внутренняя линия адреса).

D0-D7 — двунаправленная линия, составляющая шину данных.

Чтение

(![]() )

— сигнал для вывода данных из памяти

на шину данных МП системы.

)

— сигнал для вывода данных из памяти

на шину данных МП системы.

Запись

(![]() )

— сигнал для записи данных из МП в

память.

)

— сигнал для записи данных из МП в

память.

Все

адресные сигналы подлежат буферированию,

что выполнено на ИМС ТТЛ типа малой

степени интеграции. Они служат для

развязки шин микро ЭВМ и внутренних

адресных входов внутри памяти. В небольших

схемах памяти буферы могут не

использоваться. А0-А8 — адресная шина с

буферами непосредственно на ИМС памяти.

А9 служит для выбора одной из двух ИМС

памяти. Следовательно, адресуемая ячейка

находится в одной из двух 512 битовых

областей памяти. А9 поступает через

схему «ИЛИ» на одну из ИМС памяти, а

![]() через вторую схему «ИЛИ» на вторую схему

памяти, следовательно, когда выбрана

одна из ИМС, доступ ко второй закрыт.

через вторую схему «ИЛИ» на вторую схему

памяти, следовательно, когда выбрана

одна из ИМС, доступ ко второй закрыт.

Адреса А10-А15 сравниваются с набором данных адресов, набранного посредством тумблеров S1-S6. Выходной сигнал схемы сравнения содержит информацию о том, имеет ли место обращение к данной памяти. Если адресные сигналы совпадают с адресом полученным набором тумблеров, то на выходе схемы сравнения формируется сигнал логического «0», который разрешает выбор кристалла на данной плате памяти. Если не совпадают сигналы А10-А15 с S1-S6 , то на выходе схемы сравнения формируется сигнал логической «1»,запрещающий обращение к данной плате памяти. Если на линиях S1-S6 все «0», то плата памяти будет реагировать на адреса от 0 до 1 кБ, если S1=1, S2-S6=0 — на адреса 1кБ-2кБ и т.д. Следовательно, наращивание памяти возможно до 64 кБ с помощью тумблеров S1-S6.

Рис. 9.7. Структурная схема памяти небольшой МП системы

Линии D0-D7 связаны с кристаллами с помощью шинного приемопередатчика (формирователя). Эти формирователи ТТЛ типа выполняют 2 функции: обеспечивают ввод (запись) данных и вывод (считывание). При соответствующих сигналах «чтение» и «запись».