- •146 Цифровая схемотехника Конспект цифровая схемотехника

- •2. Формирователи прямоугольных импульсов

- •10. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы.

- •1.2 Прохождение импульсов через rc-цепи.

- •1.2.1 Напряжение и ток в rc-цепях под воздействием единичного скачка.

- •1.2.2 Дифференцирующая (укорачивающая) и разделительная rc-цепи.

- •1.2.3 Реальные rc-цепи при импульсном воздействии.

- •1.3 Фиксаторы уровня в дифференцирующих rc-цепях.

- •1.4 Интегрирующие rc-цепи.

- •Погрешности интегрирующей цепи:

- •2. Формирователи прямоугольных импульсов

- •2.1 Диодные ограничители последовательного и параллельного типа.

- •2.2 Линейные модели транзистора в режиме большого сигнала.

- •2.3 Расчет транзисторных ключей.

- •2.4 Транзисторный усилитель ограничитель.

- •2.5 Динамические характеристики транзисторных ключей.

- •3. Мультивибраторы

- •3.2 Транзисторный мультивибратор. Принцип действия, осциллограм-мы работы мультивибратора

- •3.3 Расчет периода колебаний мультивибратора

- •3.4 Регулировка частоты, термостабилизация и улучшение формы выходного напряжения мультивибратора.

- •3.5 Транзисторный одновибратор. Принцип действия, осциллограммы.

- •4. Потенциальные логичекие элементы

- •4.2 Диодная логика. Логика «и»

- •Логика «или»

- •Недостатки диодной логики: схемы критичны к внутреннему сопротивлению источников эдс (), обладают нестабильными уровнями логического «0» и «1».

- •4.3 Диодно-транзисторная логика (дтл)

- •4.4 Транзистор-транзисторная логика (ттл)

- •4.5 Логические элементы на моп и кмоп-структурах.

- •5.1 Мультивибраторы на потенциальных логических элементах.

- •5.2 Одновибраторы на потенциальных логических элементах.

- •5.2 Одновибраторы на потенциальных логических элементах.

- •Расчет длительности импульса одновибратора.

- •6.1 Кодирование временных интервалов.

- •6.2 Кодирование напряжение.

- •6.3 Аналогово-цифровые преобразователи (ацп). Основные характеристики и параметры.

- •6.3.1 Ацп на параллельных компараторах;

- •6.3.2 Ацп поразрядного кодирования.

- •6.4 Цифро-аналоговые преобразователи (цап). Структура, основные характеристики и параметры.

- •6.4.1 Взвешенная схема, управляющая напряжением.

- •6.5 Устройство выборки хранения.

- •7.1 Общая характеристика и принципы построения глин.

- •7.2 Автоколебательные глин на транзисторах.

- •7.3 Ждущие глин на транзисторах.

- •7.4 Глин на оупт.

- •8.2 Автоколебательный блокинг-генератор.

- •8.3 Ждущий блокинг-генератор.

- •8.4 Синхронизация блокинг-генератора.

- •9.1 Оперативные запоминающие устройства (озу) с произвольным доступом.

- •9.2 Статические и динамические зу.

- •9.3 Построение плат памяти.

- •9.4 Программируемые запоминающие устройства (пзу).

- •10. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы.

- •10.2 Программируемые логические матрицы (плм).

- •10.2.1 Схемотехника плм

- •10.2.2 Подготовка задачи к решению с помощью плм

- •10.2.3 Программирование плм

- •10.2.4 Упрощенное изображение схем плм

- •10.2.5 Воспроизведение скобочных форм переключательных функций

- •10.2.6 Наращивание (расширение) плм

4.2 Диодная логика. Логика «и»

П ринципиальная

схема простейшего логического элемента

«И» и таблица истинности представлены

на рис. 4.15. Если хотя бы на одном входе

схемы имеется низкий уровень положительного

напряжения, принимаемый за условный

нуль, то диод, связанный через катод с

этим входом, открыт и напряжение на его

аноде, а, следовательно, и на выходе

устройства равно нулю. Если же на всех

входах схемы присутствует высокий

(единичный) уровень напряжения, то

выходной сигнал равен единице.

ринципиальная

схема простейшего логического элемента

«И» и таблица истинности представлены

на рис. 4.15. Если хотя бы на одном входе

схемы имеется низкий уровень положительного

напряжения, принимаемый за условный

нуль, то диод, связанный через катод с

этим входом, открыт и напряжение на его

аноде, а, следовательно, и на выходе

устройства равно нулю. Если же на всех

входах схемы присутствует высокий

(единичный) уровень напряжения, то

выходной сигнал равен единице.

|

вх1 |

вх2 |

вых |

|

1 |

1 |

1 |

|

1 |

0 |

0 |

|

0 |

1 |

0 |

|

0 |

0 |

0 |

Рис.4.15 ДТ типа «И» с таблицей истинности

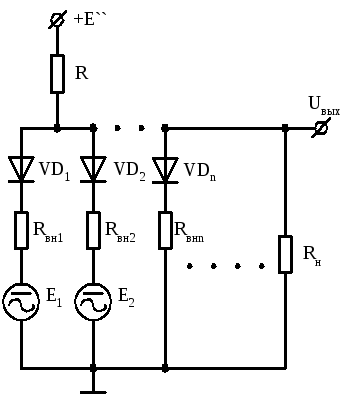

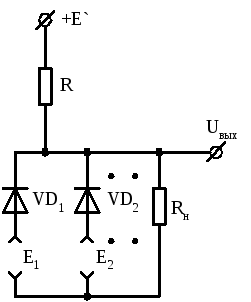

Логика «или»

Простейшее логическое устройство с таблицей истинности, выполняющее операцию дизъюнкции над логическими переменными x1 и x2 , выраженными в форме электрических напряжений, представлены на рис. 4.16. Под единичным уровнем понимают высокий положительный потенциал. Если единичный уровень присутствует хотя бы на одном входе, то через открытый диод VD1 (VD2) это напряжение передаётся на выход, создавая единичный уровень напряжения.

Недостатки диодной логики: схемы критичны к внутреннему сопротивлению источников эдс (), обладают нестабильными уровнями логического «0» и «1».

Время

задержки

![]() ;

;

|

вх1 |

вх2 |

вых |

|

1 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

1 |

|

0 |

0 |

0 |

Таблица 4.2

Рис.4.16 ДЛ типа «ИЛИ» с таблицей истинности

Для ликвидации указанных недостатков были разработаны схемы ДТЛ (диодно-транзисторная логика).

4.3 Диодно-транзисторная логика (дтл)

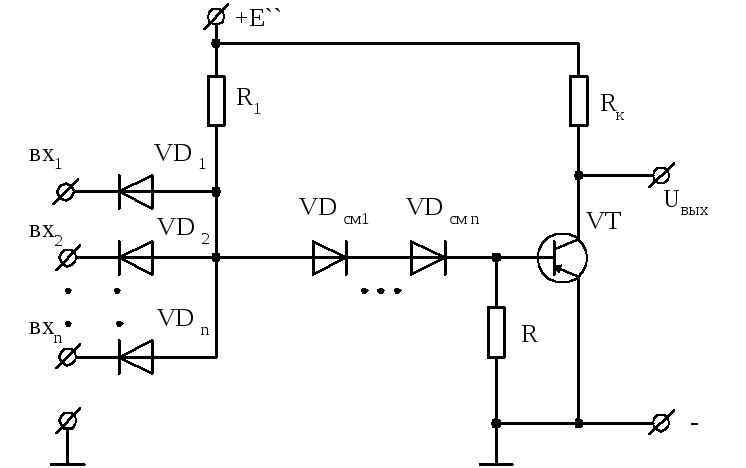

Принципиальная схема такого устройства показана на рис.4.17. В данном устройстве диоды VD1 и VD2 (совместно с резистором R1) выполняют логическую операцию «И», транзистор VT1 работает в схеме инвертора и выполняет операцию «НЕ», диоды VDсм1 и VDсмn служат увеличения порога открывания ключа, собранного на транзисторе VT1.

Достоинства схемы:

схема характеризуется высокой стабильностью логического «0» и логической «1»;

схема не критична к внутреннему сопротивлению источника

;

;выходное сопротивление данного элемента «И-НЕ» при логическом «0» на выходе определяется сопротивлением насыщенного транзистора VT

,

т.е. мало, а при логической «1» на выходе

равно сопротивлению

,

т.е. мало, а при логической «1» на выходе

равно сопротивлению .

.

Рассмотренные элементы «И-НЕ» могут быть выполнены и в интегральном исполнении. Их достоинством является малое значение втекающих входных токов.

Рис.4.17 Принципиальная схема элемента ДТЛ

![]() ;

;

![]() ;

;![]() ;

;![]() .

.

4.4 Транзистор-транзисторная логика (ттл)

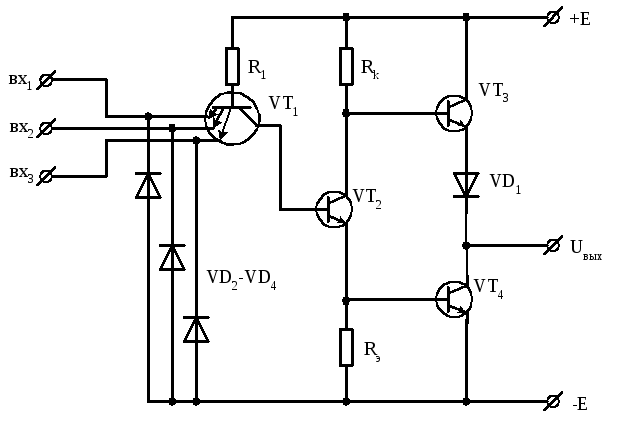

Принципиальная схема ТТЛ-элемента, являющегося основой ряда полупроводниковых интегральных микросхем для цифровых устройств, приведена на рис. 4.18. В данной схеме применен многоэмиттерный транзистор VT1. Если хотя бы один эмиттерно-базовый переход его включён в прямом направлении, то коллекторный переход многоэмиттерного транзистора VT1 смещен в обратном направлении. При отсутствии входных переходов включённых в прямом направлении базо-коллекторный переход включён в прямом направлении. Пусть на всех входах вх1, вх2 и вх3 схемы (см. рис.4.18) действуют сигналы, уровень которых соответствует уровню логической «1» (напряжение около 3,5 В). При данном уровне входных сигналов базо-коллекторный переход смещён в прямом направлении и через резистор R1 и коллекторный переход транзистора VT1 течет ток по следующей цепи: от источник питания +Е через резистор R1, базо-коллекторный переход транзистора VT1, базо-эмиттерный переход VT2 и базо-эмиттерный переход VT4. Все входящие в данную цепь переходы включены в прямом направлении. Эмиттерно-базовые переходы транзистора VT1 смещены в обратном направлении. Режим транзистора VT1 оказывается инверсным. Транзисторы VT2 и VT4 насыщены. Потенциал VT2 ниже, что обеспечивает запирание VT3. Следовательно VT3 заперт (режим отсечки), VT4 открыт и насыщен, что обеспечивает на выходе схемы низкий потенциал (уровень «0»).

Рис.4.18

Рис.4.18

При

другом сочетании входных сигналов,

когда хотя бы один из них имеет низкий

уровень напряжения – уровень логического

«0» (примерно 0,3 В), тогда эмиттерно-базовый

переход, соответствующего входа, смещен

в прямом направлении. Прямой ток этого

перехода протекает по цепи, включающей

источник питания +Е, резистор R1,

эмиттерно-базовый переход и источник

входного сигнала. Считая напряжение на

эмиттерно-базовом переходе, смещенном

в прямом направлении, близким к 0,6 В,

получим, что напряжение на базе транзистора

VT1

относительно корпуса равно 0,9 В (![]() ).

).

Напряжение

на коллекторе многоэмиттерного

транзистора будет меньше

![]() на значение падения напряжения на

включенном коллекторном переходе

на значение падения напряжения на

включенном коллекторном переходе![]() ,

т.е. примерно 0,4 В, и составляет всего

0,5 В. Это напряжение меньше, чем сумма

напряжений отсечки

,

т.е. примерно 0,4 В, и составляет всего

0,5 В. Это напряжение меньше, чем сумма

напряжений отсечки![]() и

и![]() .

Входное сопротивление выключенного

транзистораVT2,

составляющее коллекторную нагрузку

многоэмиттеного транзистора VT1,

очень велико. Входным током запертого

транзистора VT2

служит малый ток

.

Входное сопротивление выключенного

транзистораVT2,

составляющее коллекторную нагрузку

многоэмиттеного транзистора VT1,

очень велико. Входным током запертого

транзистора VT2

служит малый ток

![]() .

Этот ток и является коллекторным током

транзистора VT1.

Таким образом, транзистор VT1

имеет значительный ток базы, протекающий

через открытый базо-эмиттерный переход,

и очень малый коллекторный ток, равный

.

Этот ток и является коллекторным током

транзистора VT1.

Таким образом, транзистор VT1

имеет значительный ток базы, протекающий

через открытый базо-эмиттерный переход,

и очень малый коллекторный ток, равный

![]() .

.

При

таком соотношении базового и коллекторного

токов транзистор VT1

насыщен; его коллекторный переход смещен

в обратном направлении. Эмиттерно-базовый

ток, протекающий через открытый входной

переход, складывается из тока базы

![]() и

тока коллектора

и

тока коллектора![]() .

Значение эмиттерного тока соответствует

входному току элемента при наличии

напряжения уровня логического «0» на

входе. Остальные эмиттерыVT1

по-прежнему работают в инверсном режиме

и ток их мал.

.

Значение эмиттерного тока соответствует

входному току элемента при наличии

напряжения уровня логического «0» на

входе. Остальные эмиттерыVT1

по-прежнему работают в инверсном режиме

и ток их мал.

Таким образом, при напряжении соответствующем уровню логического «0» хотя бы на одном из входов транзистор VT2 заперт. Потенциал коллектора VT2 близок к +Е, что открываети насыщает VT3. При этом VT4 заперт, т.к. потенциал его базы близок к нулю. На выходе схемы при этом имеет место высокое напряжение порядка 3,5В (уровень логической «1»), т.к. +Е поступает на выход схемы через насыщенный транзистор VT3 и диод VD1 включённый в прямом направлении. Диоды VD2-VD4 выполняют защитные функции микросхемы от отрицательных входных импульсов. Указанное преобразование сигнала соответствует логической операции «И-НЕ», которую выполняет каскад на многоэмиттерном транзисторе VT1 операция «И» инвертор, собранный на транзисторах VT2, VT3 и VT4 (операция «НЕ»).

Параметры

схемы «И-НЕ» серии К155:

![]() ;

;![]() ;

;![]() ;

;![]() ;

;![]() ;

;![]() .

.