- •146 Цифровая схемотехника Конспект цифровая схемотехника

- •2. Формирователи прямоугольных импульсов

- •10. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы.

- •1.2 Прохождение импульсов через rc-цепи.

- •1.2.1 Напряжение и ток в rc-цепях под воздействием единичного скачка.

- •1.2.2 Дифференцирующая (укорачивающая) и разделительная rc-цепи.

- •1.2.3 Реальные rc-цепи при импульсном воздействии.

- •1.3 Фиксаторы уровня в дифференцирующих rc-цепях.

- •1.4 Интегрирующие rc-цепи.

- •Погрешности интегрирующей цепи:

- •2. Формирователи прямоугольных импульсов

- •2.1 Диодные ограничители последовательного и параллельного типа.

- •2.2 Линейные модели транзистора в режиме большого сигнала.

- •2.3 Расчет транзисторных ключей.

- •2.4 Транзисторный усилитель ограничитель.

- •2.5 Динамические характеристики транзисторных ключей.

- •3. Мультивибраторы

- •3.2 Транзисторный мультивибратор. Принцип действия, осциллограм-мы работы мультивибратора

- •3.3 Расчет периода колебаний мультивибратора

- •3.4 Регулировка частоты, термостабилизация и улучшение формы выходного напряжения мультивибратора.

- •3.5 Транзисторный одновибратор. Принцип действия, осциллограммы.

- •4. Потенциальные логичекие элементы

- •4.2 Диодная логика. Логика «и»

- •Логика «или»

- •Недостатки диодной логики: схемы критичны к внутреннему сопротивлению источников эдс (), обладают нестабильными уровнями логического «0» и «1».

- •4.3 Диодно-транзисторная логика (дтл)

- •4.4 Транзистор-транзисторная логика (ттл)

- •4.5 Логические элементы на моп и кмоп-структурах.

- •5.1 Мультивибраторы на потенциальных логических элементах.

- •5.2 Одновибраторы на потенциальных логических элементах.

- •5.2 Одновибраторы на потенциальных логических элементах.

- •Расчет длительности импульса одновибратора.

- •6.1 Кодирование временных интервалов.

- •6.2 Кодирование напряжение.

- •6.3 Аналогово-цифровые преобразователи (ацп). Основные характеристики и параметры.

- •6.3.1 Ацп на параллельных компараторах;

- •6.3.2 Ацп поразрядного кодирования.

- •6.4 Цифро-аналоговые преобразователи (цап). Структура, основные характеристики и параметры.

- •6.4.1 Взвешенная схема, управляющая напряжением.

- •6.5 Устройство выборки хранения.

- •7.1 Общая характеристика и принципы построения глин.

- •7.2 Автоколебательные глин на транзисторах.

- •7.3 Ждущие глин на транзисторах.

- •7.4 Глин на оупт.

- •8.2 Автоколебательный блокинг-генератор.

- •8.3 Ждущий блокинг-генератор.

- •8.4 Синхронизация блокинг-генератора.

- •9.1 Оперативные запоминающие устройства (озу) с произвольным доступом.

- •9.2 Статические и динамические зу.

- •9.3 Построение плат памяти.

- •9.4 Программируемые запоминающие устройства (пзу).

- •10. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы.

- •10.2 Программируемые логические матрицы (плм).

- •10.2.1 Схемотехника плм

- •10.2.2 Подготовка задачи к решению с помощью плм

- •10.2.3 Программирование плм

- •10.2.4 Упрощенное изображение схем плм

- •10.2.5 Воспроизведение скобочных форм переключательных функций

- •10.2.6 Наращивание (расширение) плм

4.5 Логические элементы на моп и кмоп-структурах.

Появление и широкое использование полевых транзисторов с изолированным затвором положило начало ряду очень перспективных семейств логических элементов.

В основе МДП-логики, или, что то же самое, МОП-логики (МОПТЛ), ключевые схемы на МОП-транзисторах. В них за уровень логического нуля принимается напряжение на открытом транзисторе, которое у полевых транзисторов столь же мало, как у насыщенного биполярного транзистора, т.е. 0,05-0,15 В. За уровень логической единицы принимают напряжение сток-исток закрытого транзистора, которое близко к напряжению питания схемы. Таким образом, логический перепад напряжения близок к напряжению питания.

Большая разница между уровнями нуля и единицы значительно повышают помехоустойчивость схемы по сравнению с логикой на биполярных элементах, такой как ДТЛ, ТТЛ и особенно ЭСТЛ, НСТЛ и И2Л.

Еще одно преимущество МОП-логики заключается в том, что ее входные (затворные) цепи практически не потребляют тока. Влияние входной цепи последующего (нагрузочного) элемента сводится лишь к увеличению входной емкости данной ячейки.

Однако как раз это преимущество — высокое сопротивление входных цепей — приводит к затягиванию заряда и разряда паразитных емкостей, что является главной причиной невысокого быстродействия МОП-логики по сравнению с ЭСТЛ, ТТЛ.

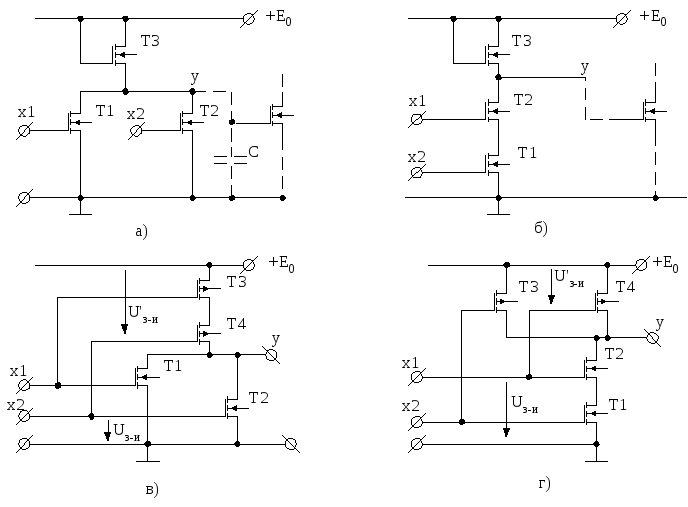

На рис. 4.19. а, б приведены ячейки типа ИЛИ-НЕ и И-НЕ, реализованные на МОП-транзисторах с индуцированным n-каналом. Здесь Транзистор Т3 служит динамической нагрузкой. В схеме на рис. 4.19, а логические транзисторы Т1 и Т2 включены параллельно, поэтому отпирание каждого из низ логической единицей на входе приводит к снижению выходного уровня до логического нуля, т.е. схема выполняет операцию ИЛИ-НЕ.

В логической схеме на рис. 4.19, б ток в цепи, а значит, и низкий уровень выходного напряжения возможен только при отпирании всех (в данном случае обоих) транзисторов. Это имеет место при подаче напряжения высокого уровня, соответствующего логической единице, одновременно на все входы. Отсюда ясно, что эта схема выполняет функцию И-НЕ.

Рисунок

4.19.

Рисунок

4.19.

МОП-логика на ключах с динамической нагрузкой не получила существенного распространения из-за заметного потребления энергии ключом в открытом состоянии.

МОП-транзисторная логика на комплиментарных транзисторах (КМОПТЛ) имеет основное достоинство в том, что в ней изменение выходного напряжения не связано с изменением тока: он остается близким к нулю. Два типовых варианта таких логических элементов показаны на рис. 4.19, в, г, из которых видна закономерность структуры КМОПТЛ: параллельное соединение транзисторов одного типа сопровождается последовательным соединением транзисторов другого типа. Выполняемая логическая функция определяется включением транзисторов «нижнего этажа» Т1 и Т2. В рассматриваемой схеме это n-канальные транзисторы. Если изменить полярность питающего напряжения, то в «нижнем этаже» окажутся транзисторы с p-каналом.

Пусть в схеме на рис. 4.19, в на оба логических входа поданы уровни x1=x2=Uз-и=0. Тогда в n-канальных транзисторах Т1 и Т2 канала не образуется, т.е. они заперты. В p-канальных транзисторах Т3 и Т4, наоборот, образуется каналы, так как разность потенциалов U’з-и Е0 заведомо превышает (по модулю) пороговое напряжение. Однако поскольку через каналы протекают ничтожно малые токи запертых транзисторов Т1 и Т2, падение напряжения на каналах тоже получается ничтожным. Поэтому можно считать, что выходное напряжение равно напряжению питания. Это и есть уровень единицы (y=1).

Если поданы на входы x1 или x2 уровень Uз-и=Е0, то в транзисторе Т1 (Т2) образуется кал, а в транзисторе Т3(Т4) исчезает, т.е. этот транзистор запирается. Ничтожно малый остаточный ток транзистора Т3 (Т4), протекая через канал Т1 (Т2), дает на нем практически нулевое падение напряжения (y=0).

Помимо высокой экономичности, преимуществом КМОПТЛ по сравнению с МОПТЛ являются малые рабочие напряжения и более высокое быстродействие. Схема на рис 4.19, г характеризуется аналогичными свойствами, какими пользовались выше.

5. РЕЛАКСАЦИОННЫЕ ГЕНЕРАТОРЫ НА ПОТЕНЦИАЛЬНЫХ ЛОГИЧЕСКИХ ЭЛЕМЕНТАХ.