- •146 Цифровая схемотехника Конспект цифровая схемотехника

- •2. Формирователи прямоугольных импульсов

- •10. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы.

- •1.2 Прохождение импульсов через rc-цепи.

- •1.2.1 Напряжение и ток в rc-цепях под воздействием единичного скачка.

- •1.2.2 Дифференцирующая (укорачивающая) и разделительная rc-цепи.

- •1.2.3 Реальные rc-цепи при импульсном воздействии.

- •1.3 Фиксаторы уровня в дифференцирующих rc-цепях.

- •1.4 Интегрирующие rc-цепи.

- •Погрешности интегрирующей цепи:

- •2. Формирователи прямоугольных импульсов

- •2.1 Диодные ограничители последовательного и параллельного типа.

- •2.2 Линейные модели транзистора в режиме большого сигнала.

- •2.3 Расчет транзисторных ключей.

- •2.4 Транзисторный усилитель ограничитель.

- •2.5 Динамические характеристики транзисторных ключей.

- •3. Мультивибраторы

- •3.2 Транзисторный мультивибратор. Принцип действия, осциллограм-мы работы мультивибратора

- •3.3 Расчет периода колебаний мультивибратора

- •3.4 Регулировка частоты, термостабилизация и улучшение формы выходного напряжения мультивибратора.

- •3.5 Транзисторный одновибратор. Принцип действия, осциллограммы.

- •4. Потенциальные логичекие элементы

- •4.2 Диодная логика. Логика «и»

- •Логика «или»

- •Недостатки диодной логики: схемы критичны к внутреннему сопротивлению источников эдс (), обладают нестабильными уровнями логического «0» и «1».

- •4.3 Диодно-транзисторная логика (дтл)

- •4.4 Транзистор-транзисторная логика (ттл)

- •4.5 Логические элементы на моп и кмоп-структурах.

- •5.1 Мультивибраторы на потенциальных логических элементах.

- •5.2 Одновибраторы на потенциальных логических элементах.

- •5.2 Одновибраторы на потенциальных логических элементах.

- •Расчет длительности импульса одновибратора.

- •6.1 Кодирование временных интервалов.

- •6.2 Кодирование напряжение.

- •6.3 Аналогово-цифровые преобразователи (ацп). Основные характеристики и параметры.

- •6.3.1 Ацп на параллельных компараторах;

- •6.3.2 Ацп поразрядного кодирования.

- •6.4 Цифро-аналоговые преобразователи (цап). Структура, основные характеристики и параметры.

- •6.4.1 Взвешенная схема, управляющая напряжением.

- •6.5 Устройство выборки хранения.

- •7.1 Общая характеристика и принципы построения глин.

- •7.2 Автоколебательные глин на транзисторах.

- •7.3 Ждущие глин на транзисторах.

- •7.4 Глин на оупт.

- •8.2 Автоколебательный блокинг-генератор.

- •8.3 Ждущий блокинг-генератор.

- •8.4 Синхронизация блокинг-генератора.

- •9.1 Оперативные запоминающие устройства (озу) с произвольным доступом.

- •9.2 Статические и динамические зу.

- •9.3 Построение плат памяти.

- •9.4 Программируемые запоминающие устройства (пзу).

- •10. Программируемые логические матрицы, программируемая матричная логика, базовые матричные кристаллы.

- •10.2 Программируемые логические матрицы (плм).

- •10.2.1 Схемотехника плм

- •10.2.2 Подготовка задачи к решению с помощью плм

- •10.2.3 Программирование плм

- •10.2.4 Упрощенное изображение схем плм

- •10.2.5 Воспроизведение скобочных форм переключательных функций

- •10.2.6 Наращивание (расширение) плм

6.1 Кодирование временных интервалов.

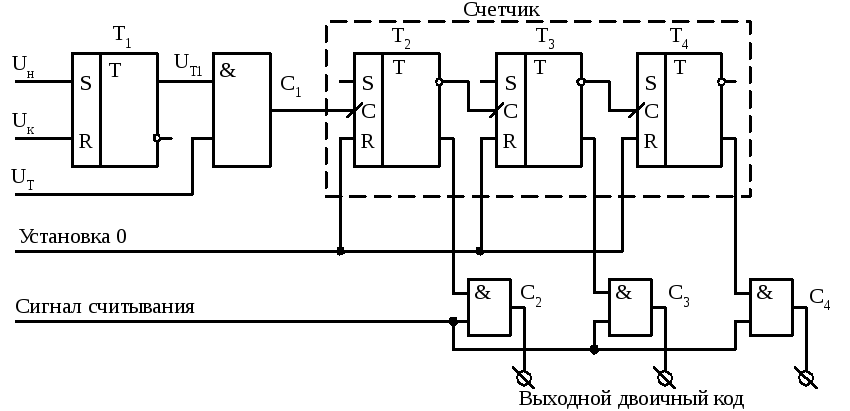

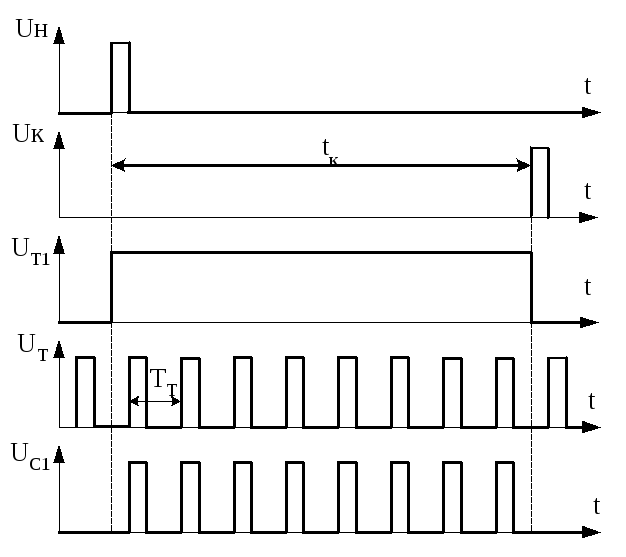

Пусть рассматриваемая функция отражает какой-либо временной интервал. В качестве примера можно определить интервал времени между посланным и отраженным от цели сигналом радиолокатора с целью определения расстояния до цели. Устройство, с помощью которого можно измерить временной интервал, представлено на рис. 6.2, а временные диаграммы его работы приведены на рис. 6.3.

Рис. 6.2. Устройство преобразование временного интервала в цифровой код

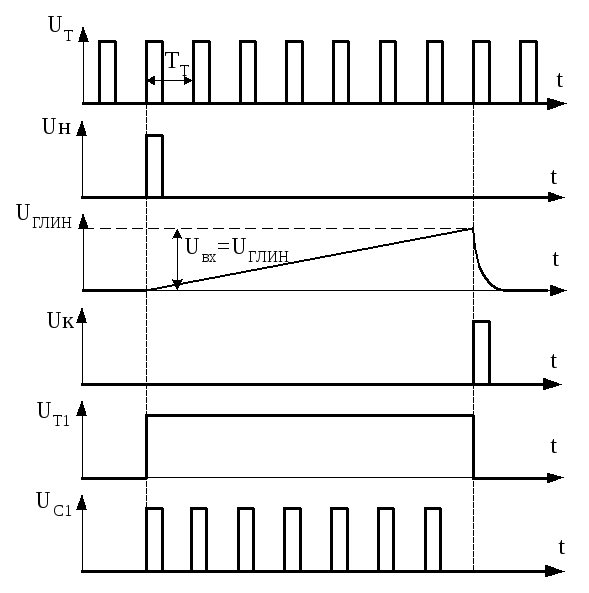

Импульс начала Uн(посылка импульсом радиолокатором) поступает на входSтриггера Т1и устанавливает его в состояние «1», а импульс концаUк(приход отраженного сигнала) поступает на входRтриггера Т1, устанавливая его в состояние «0». На первый вход схемы совпадения С1поступает сигналUТ1состояния триггера Т1, а на второй вход — тактовые импульсыUТ. На выходе схемы совпадения С1имеют место только те импульсы, которые попадают в интервал времени между поступлениями импульсовUниUк—tк. Чем выше тактовая частота сигналаUТ, тем точнее измеряется интервалtк. (см. рис. 6.3).

Рис. 6.3. Временные диаграммы работы устройства кодирования временного интервала.

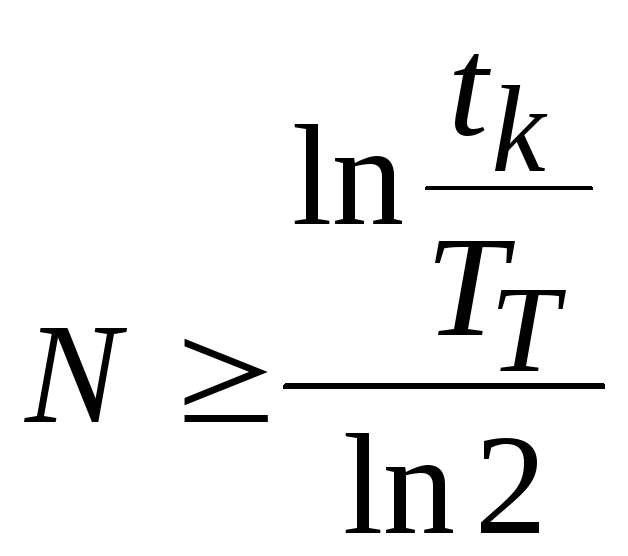

Количество импульсов отсчитывается счетчиком, собранного на триггерах Т2, Т3, Т4, и по сигналу считывания через схемы совпадения С2, С3, С4этот код выставляется на выходе схемы. Число разрядов счетчика выбирается из условия:

![]()

![]()

![]() ,

,

откуда следует, что число разрядов счетчика N:

![]()

.

.

![]() При

вещественном значении числаNнеобходимо применить большее целое

число.

При

вещественном значении числаNнеобходимо применить большее целое

число.

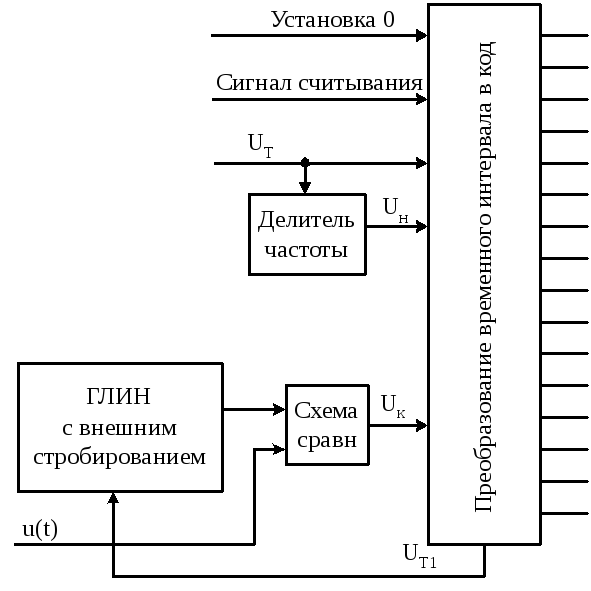

6.2 Кодирование напряжение.

![]() Схема

преобразования аналогового напряженияu(t) в цифровой

код представлена на рис. 6.4.

Схема

преобразования аналогового напряженияu(t) в цифровой

код представлена на рис. 6.4.

![]() Она состоит из 2-х частей:

Она состоит из 2-х частей:

схемы преобразования напряжения u(t) в пропорциональный ему временной интервалtк;

схемы преобразования временного интервала в цифровой код.

Работа 2-ой схемы рассмотрена в разделе 6.1.

![]()

Рис. 6.4. Схема кодирования напряжения

Тактовый сигнал UТпоступает на делитель частоты, который

формирует сигнал начала преобразованияUн, поступающий на

схему преобразования временного

интервала в цифровой код. Под действием

этого сигнала триггер Т1(см. рис.

6.2) устанавливается в «1» и сигналUТ1

поступает дополнительно на генератор

линейно-изменяющегося напряжения (ГЛИН)

в качестве строба (см. рис. 6.4). По этому

сигналу ГЛИН начинает формировать

пилообразное линейно-возрастающее

напряжение, поступающее на вход схемы

сравнения (компаратор). На второй вход

компаратора поступает входной сигналu(t). Когда

входное напряжение ГЛИН достигает

значенияUвх

(![]() )срабатывает компаратор и формирует

импульс концаUк,

переключающий триггер Т1в состояние

«0». При линейной зависимостиUГЛИН(t)

времяtмежду импульсамиUниUкпропорциональноUвх.

Следовательно, цифровой код схемы

преобразования временного интервала

в код будет пропорционален (или равен

в соответствующем масштабе) измеряемому

входному сигналу. Сигнал «0» на выходеUТ1формирует обратный

ход ГЛИН, система возвращается в исходное

состояние и ждет очередного импульса

(Uн) обусловленного

тактовыми импульсами.

)срабатывает компаратор и формирует

импульс концаUк,

переключающий триггер Т1в состояние

«0». При линейной зависимостиUГЛИН(t)

времяtмежду импульсамиUниUкпропорциональноUвх.

Следовательно, цифровой код схемы

преобразования временного интервала

в код будет пропорционален (или равен

в соответствующем масштабе) измеряемому

входному сигналу. Сигнал «0» на выходеUТ1формирует обратный

ход ГЛИН, система возвращается в исходное

состояние и ждет очередного импульса

(Uн) обусловленного

тактовыми импульсами.

Временные диаграммы работы схемы кодирования напряжения приведены на рис. 6.5.

Рис. 6.5. Временные диаграммы работы схемы кодирования напряжения