- •Конспект лекцій з дисципліни

- •Конспект лекцій з дисципліни

- •Частина 1. Проектування цифрових пристроїв

- •На базі пеом

- •Лекція 1. Етапи і методи розробки цифрових

- •Пристроїв на базі пеом

- •1.1. Навіщо необхідний персональний комп'ютер радіоінженеру?

- •1.2. Переваги та недоліки цифрових пристроїв у порівнянні з аналоговими пристроями

- •1.3. Типова функціональна схема радіотехнічної системи

- •1.4. Етапи проектування цифрових пристроїв

- •1.5. Приклад проектування рекурсивного та трансверсального цифрового фільтра

- •Лекція 2. Елементи електронної пам'яті у цифрових пристроях

- •2.1. Класифікація елементів пам'яті

- •2.2. Постійні запам'ятовувальні пристрої

- •Лекція 3. Застосування постійних запам'ятовувальних пристроїв

- •3.1. Зберігання даних на прикладі блоку rom-bios pc/xt

- •3.2. Функціональне перетворення

- •Шифратори та дешифратори

- •3.3. Формування цифрових і аналогових сигналів Формування сигналів із програмованою часовою діаграмою

- •Формування аналогових сигналів заданої форми

- •3.4. Програмування пзп

- •Лекція 4. Застосування статичних та динамічних озп

- •4.1. Статичні озп

- •4.2. Динамічні озп (dram)

- •4.3. Побудова лінії затримки на елементах пам'яті

- •4.4. Блоки пам'яті на динамічних озп

- •Лекція 5. Модулі динамічної пам'яті

- •5.1. Характеристики модулів динамічної пам'яті

- •5.2. Методи підвищення пропускної здатності динамічної пам'яті

- •5.3. Типи модулів пам'яті fpm dram (Fast Page Mode dram) - швидка сторінкова пам'ять

- •Bedo (Burst edo) - пакетна edo ram

- •Sdram (Synchronous dram) - синхронна dram

- •Частина 2. Базова архітектура пэвм стандарту ibm pc/xt Лекція 6. Історія появи стандарту pc. Фірми ibm, Microsoft, Intel, amd

- •6.1. Внесок фірми ibm у створення та розвиток пк

- •6.2. Внесок фірми Microsoft у створення й розвиток пк

- •6.3. Внесок фірми Intel у створення й розвиток пк

- •6.4. Внесок фірми amd у створення й розвиток пк

- •Лекція 7. Архітектура пэвм ibm pc/xt і способи підключення зовнішніх пристроїв

- •7.1. Функціональна схема пэвм ibm pc/xt

- •Шинна організація персональних комп'ютерів

- •Організація системних шин pc/xt

- •7.2. Способи підключення зовнішнього пристрою до комп'ютера

- •Включення через послідовний порт

- •Включення через паралельний порт

- •Включення в системну шину

- •Підключення через сучасні інтерфейси

- •7.3. Центральний процесор 8088 Адресний простір пам'яті та введення/виводу

- •Структура мікропроцесора 8088

- •Лекція 8. Порти введення/виводу, реальний режим та базова система введення/виводу

- •8.1. Карта портів введення/виводу

- •8.2. Карта пам'яті в реальному режимі

- •8.3. Призначення та структура rom-bios в pc

- •Лекція 9. Система переривань

- •9.1. Призначення та розподіл переривань

- •9.2. Організація системи переривань

- •9.3. Контролер переривань 8259

- •Лекція 10. Компоненти системної плати - співпроцесор, порти та таймер

- •10.1. Математичний співпроцесор 8087

- •10.2. Паралельний периферійний інтерфейс

- •10.3. Периферійний інтегральний таймер

- •Лекція 11. Система прямого доступу до пам’яті

- •11.1. Організація прямого доступу до пам’яті

- •11.2. Контролер dma 8237

- •Регістри та команди контролера пдп

- •Режими роботи контролера пдп

- •Частина 3. Розвиток архітектури стандарту pc Лекція 12. Структура та режими роботи сучасного процесора

- •12.1. Вимоги до сучасних процесорів

- •12.2. Структура сучасного процесора

- •Технології енергозбереження

- •Технології шифрування та захисту

- •12.3. Режими роботи центрального процесора

- •Лекція 13. Системні технології кешування та Plug & Play

- •13.1. Кешування інструкцій та даних

- •13.2. Системні ресурси та карта пам'яті в ос Windows

- •13.3. Технологія Plug & Play

- •Лекція 14. Інтерфейси

- •14.1. Класифікація інтерфейсів

- •14.2. Послідовний інтерфейс (com)

- •14.2. Паралельний інтерфейс (lpt)

- •Стандарти lpt

- •Стандарт ieee 1284

- •Формування циклів запису та читання в стандарті epp Діаграми сигналів у режимі epp

- •Лекція 15. Сучасні інтерфейси

- •15.1. Інтерфейс usb

- •Пристрої usb - функції та хаби

- •Типи передачі даних

- •15.2. Інтерфейс FireWire (ieee 1394)

- •Порівняння FireWire і usb

- •15.3. Радиоинтерфейс BlueTooth

- •15.4. Радіоінтерфейс Wi-Fi

- •15.5. Інтерфейс Wireless usb

- •Лекція 16. Внутрішні шини стандарту pc

- •16.1. Шина isa

- •16.2. Шина pci

- •16.3. Інтерфейс agp

- •16.4. Інтерфейс pci-Express 16x

- •Лекція 17. Пристрої зберігання даних

- •17.1. Основні характеристики зовнішніх накопичувачів

- •17.2. Структура дисків

- •Дефрагментация

- •Файлова система fat і ntfs

- •17.3. Типи накопичувачів

- •Гнучкі диски (Floppy)

- •Жорсткі диски (hd)

- •Твердотільні накопичувачі ssd (solid state drive)

- •Флэш-Накопичувачі (Flash-card)

- •Гибридные жёсткие диски(h-hdd)

- •Оптичні диски (cd)

- •Лекція 18. Сучасні технології зберігання даних

- •18.1. Raid-Системи

- •Основні поняття та визначення

- •18.3. Складні raid-Масиви

- •Частина 4. Комп'ютерні системи Лекція 19. Еволюція комп'ютерних архітектур 2-4 поколінь

- •19.1. Пеом на базі i286

- •19.2. Пеом на базі i386

- •19.3. Пеом на базі процесора i486

- •Лекція 20. Центральний процесор Pentium

- •20.1. Процесори Pentium першого покоління Процесор 80586 (Pentium)

- •Процесор 80686 (Pentium Pro)

- •20.2. Процесори Pentium другого та третього покоління

- •Лекція 21. Сучасні процесори Pentium

- •21.1. Процесор Pentium IV Перше покоління Pentium IV

- •Друге покоління Pentium IV

- •21.2. Багатоядерна архітектура Pentium d - Conroe

- •Процесори для мобільних систем

- •Лекція 22. Процесори фірми amd

- •22.1. Клони Intel

- •22.2. П'яте та шосте покоління (k5, k6)

- •Сімейство k5

- •Сімейство k6

- •22.3. Athlon - сьоме покоління процесорів

- •Лекція 23. Сучасні процесори фірми amd

- •23.1. Athlon64 - восьме покоління процесорів

- •23.2. Athlon64 x2 - дев'яте покоління процесорів

- •23.3. Phenom – деcяте покоління процесорів (Stars Core)

- •Лекція 24. Мультимедіа - Відеосистема

- •24.1. Технологія та стандарти відеосистеми Двовимірне зображення

- •Синтез тривимірного зображення

- •24.2. Відео карта

- •Лекція 25. Мультимедиа - Монітори

- •25.1. Монітори на основі епт (crt)

- •25.2. Рідкокристалічні монітори та проектори (lcd)

- •25.3. Плазмені дисплеї (Plasma Display Panel)

- •25.4. Електролюмінесцентні монітори (oeld)

- •25.5. Органічні світлодіодні монітори (oled)

- •Лекція 26. Мультимедіа - звуковідтворення

- •26.1. Технології та стандарти

- •Режим аудиоплейера

- •Режим редактора

- •Синтезатор звуків

- •Голосове керування рс

- •Стиск аудіоданих із втратами

- •Системи кодування аудіоданих

- •26.2. Апаратна реалізація аудиоканала

- •26.3. Акустична система

- •Лекція 27. Оптимальні конфігурації пэвм

- •27.1. Класифікація комп'ютерних систем

- •27.2. Критерій оптимальної конфігурації пэвм

- •27.3. Приклади оптимальних конфігурацій пеом

Лекція 5. Модулі динамічної пам'яті

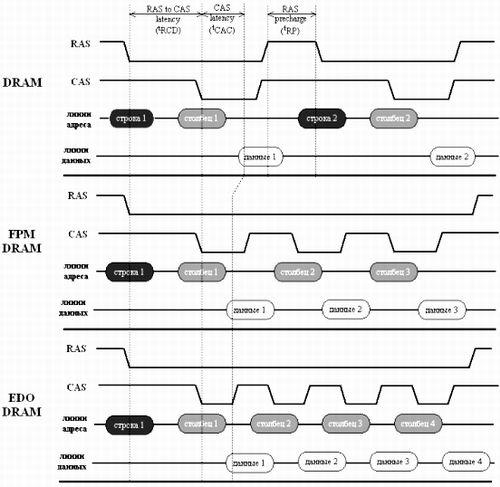

У мікросхемах пам'яті, що випускались аж до середини дев'яностих, всі три затримки (RAS to CAS Delay, CAS Delay і RAS precharge) у сумі становили близько 200нс, що відповідало двом тактам в 10МГц системі та, відповідно, дванадцяти - в 60МГц. З появою Intel Pentium 60 (1993 рік) та Intel 486 DX4-100 (1994 рік) виникла потреба в удосконалюванні динамічної пам'яті. Були запропоновані модулі пам'яті - закінчені блоки, що містять також елементи управління.

5.1. Характеристики модулів динамічної пам'яті

1. Розрядність.

2. Тактова частота.

3. Діаграми сигналів.

4. Формула пам'яті (тайминги).

Для запису або читання комірки пам’яті спочатку циклу подається сигнал RAS#, щоб прочитати адресу рядка. Потім через інтервал tRCD (затримка RAS-to-CAS) подається сигнал CAS#. Перед сигналом CAS# відсилається команда запису або читання W#/R. Після подачі сигналу CAS# через інтервал CAS Latency видаються або записуються дані. Для пам'яті DDR цей інтервал становить 2, 2.5 або 3 такти. Після одержання даних контролер повинен деактивувати рядок за час tRP (RAS precharge time). Дві наступні один за одним активації сигналу RAS# не можуть бути ближче, ніж tRAS (active-to-precharge delay). Звичайно tRAS становить 5-8 тактів. Є також параметр Command Rate (1T, 2T) - це кількість тактів активізації модуля пам'яті (CS#). Схематично все сказане вище записується як (2T) 6-3-3-3 і називається формулою пам'яті (за табл.5.1 читається зверху донизу)

Таблиця 5.1.

|

Тип пам'яті |

SDRAM |

DDR SDRAM | |

|

Частота |

133МГц |

166МГц | |

|

2T – Command Rate |

Затримка команди чип-пам'ять |

2 clocks |

2 clocks |

|

Cycle Time Tras# |

Тривалість RAS# |

6 clocks |

6 clocks |

|

RAS Precharge Time |

Пауза RAS-RAS |

2 clocks |

3 clocks |

|

RAS to CAS Delay |

Затримка RAS-CAS |

2 clocks |

3 clocks |

|

CAS Latency |

Затримка CAS-Data |

3 clocks |

2.5 clocks |

Існує також поняття максимального часу доступу до довільної комірки пам'яті – латентність, що виміряється в кількості тактів центрального процесора (або просто в нс) і характеризує швидкість роботи системи в цілому. Так, латентність системи на Pentium IV становить близько 150нс, а системи на Athlon64 - менше 50нс.

Пропускна здатність (ПЗ) – максимальна кількість байт інформації, що може пропустити пристрій за одиницю часу. Залежить від здатності читання-запису за один такт (кратність), тактової частоти та ширини шини. У позначенні модулів використовується ПЗ на біт: DDR400 або ПЗ на весь модуль: PC3200 (400*8).

5.2. Методи підвищення пропускної здатності динамічної пам'яті

1. Тіньова регенерація.

2. Збільшення розрядності шини.

3. Пакетна передача (Burst).

4. Багатоканальність.

5.3. Типи модулів пам'яті fpm dram (Fast Page Mode dram) - швидка сторінкова пам'ять

FPM-DRAM - Fast-Page Mode DRAM - пам'ять зі швидким чередуванням сторінок, розроблена в 1995 році. Основною відмінністю від пам'яті попереднього покоління стала підтримка скорочених адрес. Якщо чергова запитувана комірка перебуває в тому самому рядку, що й попередня, її адреса однозначно визначається одним лише номером стовпця та передача номера рядка вже не потрібна. Формула: один RAS - багато CAS. При цьому стовпець та дані йдуть по черзі. Регенерація здійснюється в закритій сторінці.

EDO-DRAM (Extended Data Out) - пам'ять із удосконаленим виходом

Даний тип пам'яті з'явився в 1996 році. Містить спеціальний тригер-клямку, що втримує лінії даних після зникнення сигналу CAS. Тому стало можливим зняти сигнал CAS до закінчення читання даних, підготовляючи в цей час мікросхему до прийому номера наступного стовпця.

Тут за рахунок буфера на виході адреса стовпця та дані існують одночасно.

Рис. 5.1. Часові діаграми роботи деяких типів пам'яті