- •Конспект лекцій з дисципліни

- •Конспект лекцій з дисципліни

- •Частина 1. Проектування цифрових пристроїв

- •На базі пеом

- •Лекція 1. Етапи і методи розробки цифрових

- •Пристроїв на базі пеом

- •1.1. Навіщо необхідний персональний комп'ютер радіоінженеру?

- •1.2. Переваги та недоліки цифрових пристроїв у порівнянні з аналоговими пристроями

- •1.3. Типова функціональна схема радіотехнічної системи

- •1.4. Етапи проектування цифрових пристроїв

- •1.5. Приклад проектування рекурсивного та трансверсального цифрового фільтра

- •Лекція 2. Елементи електронної пам'яті у цифрових пристроях

- •2.1. Класифікація елементів пам'яті

- •2.2. Постійні запам'ятовувальні пристрої

- •Лекція 3. Застосування постійних запам'ятовувальних пристроїв

- •3.1. Зберігання даних на прикладі блоку rom-bios pc/xt

- •3.2. Функціональне перетворення

- •Шифратори та дешифратори

- •3.3. Формування цифрових і аналогових сигналів Формування сигналів із програмованою часовою діаграмою

- •Формування аналогових сигналів заданої форми

- •3.4. Програмування пзп

- •Лекція 4. Застосування статичних та динамічних озп

- •4.1. Статичні озп

- •4.2. Динамічні озп (dram)

- •4.3. Побудова лінії затримки на елементах пам'яті

- •4.4. Блоки пам'яті на динамічних озп

- •Лекція 5. Модулі динамічної пам'яті

- •5.1. Характеристики модулів динамічної пам'яті

- •5.2. Методи підвищення пропускної здатності динамічної пам'яті

- •5.3. Типи модулів пам'яті fpm dram (Fast Page Mode dram) - швидка сторінкова пам'ять

- •Bedo (Burst edo) - пакетна edo ram

- •Sdram (Synchronous dram) - синхронна dram

- •Частина 2. Базова архітектура пэвм стандарту ibm pc/xt Лекція 6. Історія появи стандарту pc. Фірми ibm, Microsoft, Intel, amd

- •6.1. Внесок фірми ibm у створення та розвиток пк

- •6.2. Внесок фірми Microsoft у створення й розвиток пк

- •6.3. Внесок фірми Intel у створення й розвиток пк

- •6.4. Внесок фірми amd у створення й розвиток пк

- •Лекція 7. Архітектура пэвм ibm pc/xt і способи підключення зовнішніх пристроїв

- •7.1. Функціональна схема пэвм ibm pc/xt

- •Шинна організація персональних комп'ютерів

- •Організація системних шин pc/xt

- •7.2. Способи підключення зовнішнього пристрою до комп'ютера

- •Включення через послідовний порт

- •Включення через паралельний порт

- •Включення в системну шину

- •Підключення через сучасні інтерфейси

- •7.3. Центральний процесор 8088 Адресний простір пам'яті та введення/виводу

- •Структура мікропроцесора 8088

- •Лекція 8. Порти введення/виводу, реальний режим та базова система введення/виводу

- •8.1. Карта портів введення/виводу

- •8.2. Карта пам'яті в реальному режимі

- •8.3. Призначення та структура rom-bios в pc

- •Лекція 9. Система переривань

- •9.1. Призначення та розподіл переривань

- •9.2. Організація системи переривань

- •9.3. Контролер переривань 8259

- •Лекція 10. Компоненти системної плати - співпроцесор, порти та таймер

- •10.1. Математичний співпроцесор 8087

- •10.2. Паралельний периферійний інтерфейс

- •10.3. Периферійний інтегральний таймер

- •Лекція 11. Система прямого доступу до пам’яті

- •11.1. Організація прямого доступу до пам’яті

- •11.2. Контролер dma 8237

- •Регістри та команди контролера пдп

- •Режими роботи контролера пдп

- •Частина 3. Розвиток архітектури стандарту pc Лекція 12. Структура та режими роботи сучасного процесора

- •12.1. Вимоги до сучасних процесорів

- •12.2. Структура сучасного процесора

- •Технології енергозбереження

- •Технології шифрування та захисту

- •12.3. Режими роботи центрального процесора

- •Лекція 13. Системні технології кешування та Plug & Play

- •13.1. Кешування інструкцій та даних

- •13.2. Системні ресурси та карта пам'яті в ос Windows

- •13.3. Технологія Plug & Play

- •Лекція 14. Інтерфейси

- •14.1. Класифікація інтерфейсів

- •14.2. Послідовний інтерфейс (com)

- •14.2. Паралельний інтерфейс (lpt)

- •Стандарти lpt

- •Стандарт ieee 1284

- •Формування циклів запису та читання в стандарті epp Діаграми сигналів у режимі epp

- •Лекція 15. Сучасні інтерфейси

- •15.1. Інтерфейс usb

- •Пристрої usb - функції та хаби

- •Типи передачі даних

- •15.2. Інтерфейс FireWire (ieee 1394)

- •Порівняння FireWire і usb

- •15.3. Радиоинтерфейс BlueTooth

- •15.4. Радіоінтерфейс Wi-Fi

- •15.5. Інтерфейс Wireless usb

- •Лекція 16. Внутрішні шини стандарту pc

- •16.1. Шина isa

- •16.2. Шина pci

- •16.3. Інтерфейс agp

- •16.4. Інтерфейс pci-Express 16x

- •Лекція 17. Пристрої зберігання даних

- •17.1. Основні характеристики зовнішніх накопичувачів

- •17.2. Структура дисків

- •Дефрагментация

- •Файлова система fat і ntfs

- •17.3. Типи накопичувачів

- •Гнучкі диски (Floppy)

- •Жорсткі диски (hd)

- •Твердотільні накопичувачі ssd (solid state drive)

- •Флэш-Накопичувачі (Flash-card)

- •Гибридные жёсткие диски(h-hdd)

- •Оптичні диски (cd)

- •Лекція 18. Сучасні технології зберігання даних

- •18.1. Raid-Системи

- •Основні поняття та визначення

- •18.3. Складні raid-Масиви

- •Частина 4. Комп'ютерні системи Лекція 19. Еволюція комп'ютерних архітектур 2-4 поколінь

- •19.1. Пеом на базі i286

- •19.2. Пеом на базі i386

- •19.3. Пеом на базі процесора i486

- •Лекція 20. Центральний процесор Pentium

- •20.1. Процесори Pentium першого покоління Процесор 80586 (Pentium)

- •Процесор 80686 (Pentium Pro)

- •20.2. Процесори Pentium другого та третього покоління

- •Лекція 21. Сучасні процесори Pentium

- •21.1. Процесор Pentium IV Перше покоління Pentium IV

- •Друге покоління Pentium IV

- •21.2. Багатоядерна архітектура Pentium d - Conroe

- •Процесори для мобільних систем

- •Лекція 22. Процесори фірми amd

- •22.1. Клони Intel

- •22.2. П'яте та шосте покоління (k5, k6)

- •Сімейство k5

- •Сімейство k6

- •22.3. Athlon - сьоме покоління процесорів

- •Лекція 23. Сучасні процесори фірми amd

- •23.1. Athlon64 - восьме покоління процесорів

- •23.2. Athlon64 x2 - дев'яте покоління процесорів

- •23.3. Phenom – деcяте покоління процесорів (Stars Core)

- •Лекція 24. Мультимедіа - Відеосистема

- •24.1. Технологія та стандарти відеосистеми Двовимірне зображення

- •Синтез тривимірного зображення

- •24.2. Відео карта

- •Лекція 25. Мультимедиа - Монітори

- •25.1. Монітори на основі епт (crt)

- •25.2. Рідкокристалічні монітори та проектори (lcd)

- •25.3. Плазмені дисплеї (Plasma Display Panel)

- •25.4. Електролюмінесцентні монітори (oeld)

- •25.5. Органічні світлодіодні монітори (oled)

- •Лекція 26. Мультимедіа - звуковідтворення

- •26.1. Технології та стандарти

- •Режим аудиоплейера

- •Режим редактора

- •Синтезатор звуків

- •Голосове керування рс

- •Стиск аудіоданих із втратами

- •Системи кодування аудіоданих

- •26.2. Апаратна реалізація аудиоканала

- •26.3. Акустична система

- •Лекція 27. Оптимальні конфігурації пэвм

- •27.1. Класифікація комп'ютерних систем

- •27.2. Критерій оптимальної конфігурації пэвм

- •27.3. Приклади оптимальних конфігурацій пеом

9.2. Організація системи переривань

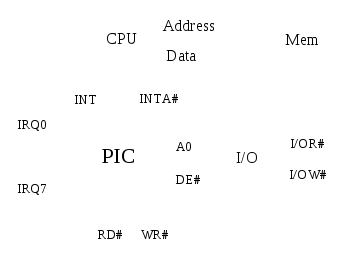

Функціональна схема системи переривань наведена на рис.9.2.

Система заснована на взаємодії CPU 8088 з контролером переривань PIC 8259А.

Рис. 9.2. Організація переривань

Початок переривання складається з подачі сигналу запиту на переривання IRQ зовнішнім пристроєм, що вимагає обслуговування, на один з восьми входів PIC. Останній робить запит на CPU сигналом INT. Крім цього, переривання може бути ініційовано відповідною командою. Центральний процесор видає два сигнали підтвердження INTA. У відповідь на сигнал підтвердження -INTА1 8259А не видає даних і залишається в Z-Стані. У цей час CPU завершує виконання поточної команди, копіює регістри F, CS, IP у стек, скидає прапор IF і готується до прийому байта з 8259. По сигналу -INTА2 8259 посилає в CPU номер переривання. Для визначення адреси початку програми CPU використовує таблицю вказівників векторів переривань, що завжди розміщається на початку пам'яті за адресою 0..3FF (1кБ).

Таблиця містить 256 елементів по 4 байти в кожному. У молодших двох байтах утримується зміщення адреси, а в старших двох байтах - базова адреса сегмента. CPU обчислює адреса зміщення як номер переривання помножений на 4 та зчитує його в регістр IP. Наступні два байти зчитуються в регістр CS та починається виконання програми за адресою CS:IP

Наприкінці програми переривання міститься команда посилки байта з CPU в 8259, що інформує про завершення переривання. CPU відновлює стан регістрів, який був до початку переривання, а 8259 готовий до обслуговування наступних запитів IRQ від зовнішніх пристроїв. У системі AT та вище використовуються два контролери переривань, включені каскадно.

9.3. Контролер переривань 8259

Структурна схема контролера представлена на мал. 9.3.

У регістрах запитів (РЗПР) і обслужених запитів (РОЗПР) порозрядно зберігаються запити від периферійних пристроїв, що очікують, та від обслужених периферійний пристроїв. Після зняття запиту та закінчення переривання у відповідний розряд записується 0.

Програмування 8259 зводиться до запису в нього слів (байт) командної ініціалізації (СКІ) і слів команд операцій (СКО). СКІ вводяться на початку роботи контролера (в BIOS) та задають режим його роботи.

│INTA#

│ INT

v

^

┌────────┐

┌───┴──────────┴────┐

D7..D0

│ Буфер │ ║ │ Схема управління │

════════╡ шини

╞═══╣ └─┬───┬──────┬──────┘

│ даних

│ ┌───────┘ v ^

└────────┘ │

╠═════╦═══│══════│══╦═══

┌────────┐ │ ║ ┌─╨───┴──┐

┌─┴──╨───┐

RD#────>┤

Логіч. ├─┤ ║ │ Регістр│ │

Регістр├<──IRQ0

WR#────>┤

схема │ │ ║ │ обслу- │ │ запитів├<──IRQ1

А0────>┤

читан./│ │ ║ │ жених │ │ перери-├<──

...

CS#────>┤

запису │ │ ║ │ запитів│ │ вань

├<──IRQ7

└────────┘ │ ║ └───┬────┘

└───┬────┘

┌────────┐ │ ║ ^

^

CАS0<──>┤

Буферн.├─┘ ║ ┌───┴──────────┴────┐

CАS1<──>┤

схема │ ╠═══╡ Схема маскування │

CАS2<──>┤

каска- │ ║ │ запитів та аналіза│

DE#

──>┤ дування│ │ їх по пріоритету

│

└────────┘

└───────────────────┘

Рис. 9.3. Структура контролера 8259

У процесі роботи можлива зміна алгоритму обслуговування запитів за допомогою команд СКО1...СКО3. СКО1 заноситься в порт 21h та забезпечує порозрядне маскування входів IRQ0...IRQ7. Одиниця в i-му розряді забороняє переривання по входу IRQi. Байти СКО2 та СКО3 записуються в порт 20h. СКО2 (А0=0, D4=0, D3=0) указує вид установки дна та дно пріоритетного кільця, а також вид кінця переривання. Наприклад, наприкінці програми переривання, як правило, заноситься число 20h у порт 20h:

MOV AL, 20h

OUT 20h, AL

Це означає нормальний кінець переривання для 8259 та перехід на обслуговування інших входів IRQ.

Контрольні питання

1. Чи можливо функціонування ПЕОМ без переривань?

2. Дайте класифікацію типів переривань.

3. Як організована система переривань?

4. Приведіть опис контролера переривань.

5. Навіщо в програмі переривання в порт 20h заноситься число 20h?