- •Конспект лекцій з дисципліни

- •Конспект лекцій з дисципліни

- •Частина 1. Проектування цифрових пристроїв

- •На базі пеом

- •Лекція 1. Етапи і методи розробки цифрових

- •Пристроїв на базі пеом

- •1.1. Навіщо необхідний персональний комп'ютер радіоінженеру?

- •1.2. Переваги та недоліки цифрових пристроїв у порівнянні з аналоговими пристроями

- •1.3. Типова функціональна схема радіотехнічної системи

- •1.4. Етапи проектування цифрових пристроїв

- •1.5. Приклад проектування рекурсивного та трансверсального цифрового фільтра

- •Лекція 2. Елементи електронної пам'яті у цифрових пристроях

- •2.1. Класифікація елементів пам'яті

- •2.2. Постійні запам'ятовувальні пристрої

- •Лекція 3. Застосування постійних запам'ятовувальних пристроїв

- •3.1. Зберігання даних на прикладі блоку rom-bios pc/xt

- •3.2. Функціональне перетворення

- •Шифратори та дешифратори

- •3.3. Формування цифрових і аналогових сигналів Формування сигналів із програмованою часовою діаграмою

- •Формування аналогових сигналів заданої форми

- •3.4. Програмування пзп

- •Лекція 4. Застосування статичних та динамічних озп

- •4.1. Статичні озп

- •4.2. Динамічні озп (dram)

- •4.3. Побудова лінії затримки на елементах пам'яті

- •4.4. Блоки пам'яті на динамічних озп

- •Лекція 5. Модулі динамічної пам'яті

- •5.1. Характеристики модулів динамічної пам'яті

- •5.2. Методи підвищення пропускної здатності динамічної пам'яті

- •5.3. Типи модулів пам'яті fpm dram (Fast Page Mode dram) - швидка сторінкова пам'ять

- •Bedo (Burst edo) - пакетна edo ram

- •Sdram (Synchronous dram) - синхронна dram

- •Частина 2. Базова архітектура пэвм стандарту ibm pc/xt Лекція 6. Історія появи стандарту pc. Фірми ibm, Microsoft, Intel, amd

- •6.1. Внесок фірми ibm у створення та розвиток пк

- •6.2. Внесок фірми Microsoft у створення й розвиток пк

- •6.3. Внесок фірми Intel у створення й розвиток пк

- •6.4. Внесок фірми amd у створення й розвиток пк

- •Лекція 7. Архітектура пэвм ibm pc/xt і способи підключення зовнішніх пристроїв

- •7.1. Функціональна схема пэвм ibm pc/xt

- •Шинна організація персональних комп'ютерів

- •Організація системних шин pc/xt

- •7.2. Способи підключення зовнішнього пристрою до комп'ютера

- •Включення через послідовний порт

- •Включення через паралельний порт

- •Включення в системну шину

- •Підключення через сучасні інтерфейси

- •7.3. Центральний процесор 8088 Адресний простір пам'яті та введення/виводу

- •Структура мікропроцесора 8088

- •Лекція 8. Порти введення/виводу, реальний режим та базова система введення/виводу

- •8.1. Карта портів введення/виводу

- •8.2. Карта пам'яті в реальному режимі

- •8.3. Призначення та структура rom-bios в pc

- •Лекція 9. Система переривань

- •9.1. Призначення та розподіл переривань

- •9.2. Організація системи переривань

- •9.3. Контролер переривань 8259

- •Лекція 10. Компоненти системної плати - співпроцесор, порти та таймер

- •10.1. Математичний співпроцесор 8087

- •10.2. Паралельний периферійний інтерфейс

- •10.3. Периферійний інтегральний таймер

- •Лекція 11. Система прямого доступу до пам’яті

- •11.1. Організація прямого доступу до пам’яті

- •11.2. Контролер dma 8237

- •Регістри та команди контролера пдп

- •Режими роботи контролера пдп

- •Частина 3. Розвиток архітектури стандарту pc Лекція 12. Структура та режими роботи сучасного процесора

- •12.1. Вимоги до сучасних процесорів

- •12.2. Структура сучасного процесора

- •Технології енергозбереження

- •Технології шифрування та захисту

- •12.3. Режими роботи центрального процесора

- •Лекція 13. Системні технології кешування та Plug & Play

- •13.1. Кешування інструкцій та даних

- •13.2. Системні ресурси та карта пам'яті в ос Windows

- •13.3. Технологія Plug & Play

- •Лекція 14. Інтерфейси

- •14.1. Класифікація інтерфейсів

- •14.2. Послідовний інтерфейс (com)

- •14.2. Паралельний інтерфейс (lpt)

- •Стандарти lpt

- •Стандарт ieee 1284

- •Формування циклів запису та читання в стандарті epp Діаграми сигналів у режимі epp

- •Лекція 15. Сучасні інтерфейси

- •15.1. Інтерфейс usb

- •Пристрої usb - функції та хаби

- •Типи передачі даних

- •15.2. Інтерфейс FireWire (ieee 1394)

- •Порівняння FireWire і usb

- •15.3. Радиоинтерфейс BlueTooth

- •15.4. Радіоінтерфейс Wi-Fi

- •15.5. Інтерфейс Wireless usb

- •Лекція 16. Внутрішні шини стандарту pc

- •16.1. Шина isa

- •16.2. Шина pci

- •16.3. Інтерфейс agp

- •16.4. Інтерфейс pci-Express 16x

- •Лекція 17. Пристрої зберігання даних

- •17.1. Основні характеристики зовнішніх накопичувачів

- •17.2. Структура дисків

- •Дефрагментация

- •Файлова система fat і ntfs

- •17.3. Типи накопичувачів

- •Гнучкі диски (Floppy)

- •Жорсткі диски (hd)

- •Твердотільні накопичувачі ssd (solid state drive)

- •Флэш-Накопичувачі (Flash-card)

- •Гибридные жёсткие диски(h-hdd)

- •Оптичні диски (cd)

- •Лекція 18. Сучасні технології зберігання даних

- •18.1. Raid-Системи

- •Основні поняття та визначення

- •18.3. Складні raid-Масиви

- •Частина 4. Комп'ютерні системи Лекція 19. Еволюція комп'ютерних архітектур 2-4 поколінь

- •19.1. Пеом на базі i286

- •19.2. Пеом на базі i386

- •19.3. Пеом на базі процесора i486

- •Лекція 20. Центральний процесор Pentium

- •20.1. Процесори Pentium першого покоління Процесор 80586 (Pentium)

- •Процесор 80686 (Pentium Pro)

- •20.2. Процесори Pentium другого та третього покоління

- •Лекція 21. Сучасні процесори Pentium

- •21.1. Процесор Pentium IV Перше покоління Pentium IV

- •Друге покоління Pentium IV

- •21.2. Багатоядерна архітектура Pentium d - Conroe

- •Процесори для мобільних систем

- •Лекція 22. Процесори фірми amd

- •22.1. Клони Intel

- •22.2. П'яте та шосте покоління (k5, k6)

- •Сімейство k5

- •Сімейство k6

- •22.3. Athlon - сьоме покоління процесорів

- •Лекція 23. Сучасні процесори фірми amd

- •23.1. Athlon64 - восьме покоління процесорів

- •23.2. Athlon64 x2 - дев'яте покоління процесорів

- •23.3. Phenom – деcяте покоління процесорів (Stars Core)

- •Лекція 24. Мультимедіа - Відеосистема

- •24.1. Технологія та стандарти відеосистеми Двовимірне зображення

- •Синтез тривимірного зображення

- •24.2. Відео карта

- •Лекція 25. Мультимедиа - Монітори

- •25.1. Монітори на основі епт (crt)

- •25.2. Рідкокристалічні монітори та проектори (lcd)

- •25.3. Плазмені дисплеї (Plasma Display Panel)

- •25.4. Електролюмінесцентні монітори (oeld)

- •25.5. Органічні світлодіодні монітори (oled)

- •Лекція 26. Мультимедіа - звуковідтворення

- •26.1. Технології та стандарти

- •Режим аудиоплейера

- •Режим редактора

- •Синтезатор звуків

- •Голосове керування рс

- •Стиск аудіоданих із втратами

- •Системи кодування аудіоданих

- •26.2. Апаратна реалізація аудиоканала

- •26.3. Акустична система

- •Лекція 27. Оптимальні конфігурації пэвм

- •27.1. Класифікація комп'ютерних систем

- •27.2. Критерій оптимальної конфігурації пэвм

- •27.3. Приклади оптимальних конфігурацій пеом

Частина 4. Комп'ютерні системи Лекція 19. Еволюція комп'ютерних архітектур 2-4 поколінь

19.1. Пеом на базі i286

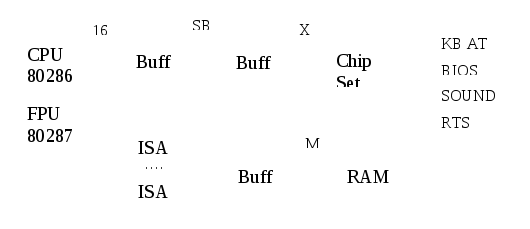

Система з’явилась у 1984р. та мала наступні особливості:

контролер клавіатури 8042 - новий стандарт AT;

застосований набір системної логіки – Chipset;

батарейна пам'ять CMOS;

годинники реального часу з календарем до кінця 1999р.;

16-розрядні шини даних;

використаний центральний процесор 80286 та співпроцесор 80287:

- технічний процес - 1500нм, 134 тис. транзисторів n-МОН;

- 16-розрядні ядро та інтерфейс;

- 24-розрядна адресація пам'яті (16МБ);

- тактова частота від 6МГц до 20МГц;

- 6-байтна черга команд;

- захищений режим;

- приблизно в 10 разів швидше PC/XT.

Функціональна схема представлена на рис.19.1.

Рис. 19.1. Структура системи i286

Саме із систем на базі i80286 почалося масове програмування та використання ПЭВМ стандарту PC.

19.2. Пеом на базі i386

Перша 32-розрядна система з'явилася в 1985р.

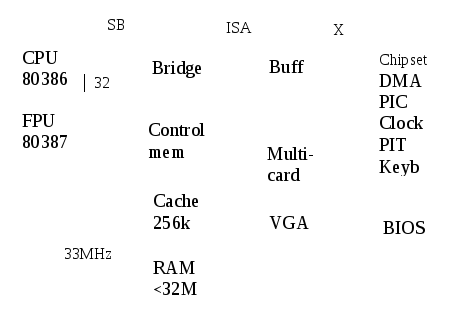

Функціональна схема представлена на рис.19.2. Ключові особливості системи на базі 80386:

частота системної шини підвищена до 33-40МГц із пропускною здатністю до 60МБ/с;

на системній платі розміщена кеш-пам'ять до 256кБ із контролером;

ОЗП у вигляді SIP-Модулів із часом доступу 60-100нс та з 2-3 тактами очікування працює на системній шині;

використаний 32-розрядний процесор 80386 та співпроцесор 80387:

- технічний процес - 1500нм, 275 тис. транзисторів, працює на частоті системної шини SB 16-40МГц;

- забезпечує адресацію до 4ГБ фізичної та до 64ТБ віртуальної пам'яті;

- поліпшений захищений режим;

- віртуальний режим;

- приблизно в 30 разів швидше PC/XT.

Рис. 19.2. Структура системи i386

19.3. Пеом на базі процесора i486

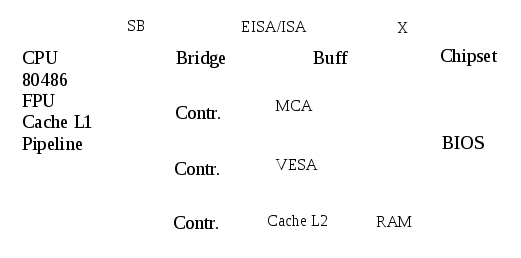

Система представлена в 1989р. Функціональна схема системи представлена на рис.19.3.

Головні особливості системи на базі процесора 80486:

запропонована шина EISA для серверів;

запропонована альтернатива EISA: шина MCA в якості розширення ISA;

відео-шина VESA 40МГц (1992р.);

нові модулі пам'яті FPM DRAM;

використане нове покоління процесорів 80486:

- технічний процес 1000-600нм, 1.2-1.6 млн. транзисторів, частота ядра до 150МГц;

- уведений коефіцієнт множення х2 та х3 ядра;

- уведена в ядро кеш-пам'ять першого рівня L1 8кБ Гарвардської архітектури (кеш L2 розміщався на системній платі);

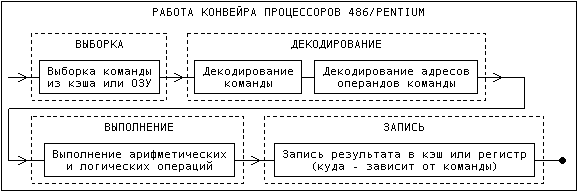

- застосований 5-стадійний конвеєр (рис.19.4);

- співпроцесор розміщений на кристалі;

- уведені пакетні цикли (burst) шини даних, що дозволяють передавати чергове слово в кожному такті шини (а не через такт);

- уведені додаткові буфери та регістри;

- збільшена черга команд до 16 байт;

- уведений розширений набір команд для мультимедійних додатків;

- приблизно в 100 разів швидше CPU 8088.

Рис. 19.3. Структура системи i486

Рис. 19.4. Робота конвеєра і486

Контрольні питання

1. Яка структура комп'ютерної системи на базі i286?

2. Чому процесор i386 називають революційним?

3. Яка структура ПЕОМ на базі i386?

4. Як функціонує конвеєр в CPU i486?

5. Назвіть особливості системи на основі CPU i486.