- •Конспект лекцій з дисципліни

- •Конспект лекцій з дисципліни

- •Частина 1. Проектування цифрових пристроїв

- •На базі пеом

- •Лекція 1. Етапи і методи розробки цифрових

- •Пристроїв на базі пеом

- •1.1. Навіщо необхідний персональний комп'ютер радіоінженеру?

- •1.2. Переваги та недоліки цифрових пристроїв у порівнянні з аналоговими пристроями

- •1.3. Типова функціональна схема радіотехнічної системи

- •1.4. Етапи проектування цифрових пристроїв

- •1.5. Приклад проектування рекурсивного та трансверсального цифрового фільтра

- •Лекція 2. Елементи електронної пам'яті у цифрових пристроях

- •2.1. Класифікація елементів пам'яті

- •2.2. Постійні запам'ятовувальні пристрої

- •Лекція 3. Застосування постійних запам'ятовувальних пристроїв

- •3.1. Зберігання даних на прикладі блоку rom-bios pc/xt

- •3.2. Функціональне перетворення

- •Шифратори та дешифратори

- •3.3. Формування цифрових і аналогових сигналів Формування сигналів із програмованою часовою діаграмою

- •Формування аналогових сигналів заданої форми

- •3.4. Програмування пзп

- •Лекція 4. Застосування статичних та динамічних озп

- •4.1. Статичні озп

- •4.2. Динамічні озп (dram)

- •4.3. Побудова лінії затримки на елементах пам'яті

- •4.4. Блоки пам'яті на динамічних озп

- •Лекція 5. Модулі динамічної пам'яті

- •5.1. Характеристики модулів динамічної пам'яті

- •5.2. Методи підвищення пропускної здатності динамічної пам'яті

- •5.3. Типи модулів пам'яті fpm dram (Fast Page Mode dram) - швидка сторінкова пам'ять

- •Bedo (Burst edo) - пакетна edo ram

- •Sdram (Synchronous dram) - синхронна dram

- •Частина 2. Базова архітектура пэвм стандарту ibm pc/xt Лекція 6. Історія появи стандарту pc. Фірми ibm, Microsoft, Intel, amd

- •6.1. Внесок фірми ibm у створення та розвиток пк

- •6.2. Внесок фірми Microsoft у створення й розвиток пк

- •6.3. Внесок фірми Intel у створення й розвиток пк

- •6.4. Внесок фірми amd у створення й розвиток пк

- •Лекція 7. Архітектура пэвм ibm pc/xt і способи підключення зовнішніх пристроїв

- •7.1. Функціональна схема пэвм ibm pc/xt

- •Шинна організація персональних комп'ютерів

- •Організація системних шин pc/xt

- •7.2. Способи підключення зовнішнього пристрою до комп'ютера

- •Включення через послідовний порт

- •Включення через паралельний порт

- •Включення в системну шину

- •Підключення через сучасні інтерфейси

- •7.3. Центральний процесор 8088 Адресний простір пам'яті та введення/виводу

- •Структура мікропроцесора 8088

- •Лекція 8. Порти введення/виводу, реальний режим та базова система введення/виводу

- •8.1. Карта портів введення/виводу

- •8.2. Карта пам'яті в реальному режимі

- •8.3. Призначення та структура rom-bios в pc

- •Лекція 9. Система переривань

- •9.1. Призначення та розподіл переривань

- •9.2. Організація системи переривань

- •9.3. Контролер переривань 8259

- •Лекція 10. Компоненти системної плати - співпроцесор, порти та таймер

- •10.1. Математичний співпроцесор 8087

- •10.2. Паралельний периферійний інтерфейс

- •10.3. Периферійний інтегральний таймер

- •Лекція 11. Система прямого доступу до пам’яті

- •11.1. Організація прямого доступу до пам’яті

- •11.2. Контролер dma 8237

- •Регістри та команди контролера пдп

- •Режими роботи контролера пдп

- •Частина 3. Розвиток архітектури стандарту pc Лекція 12. Структура та режими роботи сучасного процесора

- •12.1. Вимоги до сучасних процесорів

- •12.2. Структура сучасного процесора

- •Технології енергозбереження

- •Технології шифрування та захисту

- •12.3. Режими роботи центрального процесора

- •Лекція 13. Системні технології кешування та Plug & Play

- •13.1. Кешування інструкцій та даних

- •13.2. Системні ресурси та карта пам'яті в ос Windows

- •13.3. Технологія Plug & Play

- •Лекція 14. Інтерфейси

- •14.1. Класифікація інтерфейсів

- •14.2. Послідовний інтерфейс (com)

- •14.2. Паралельний інтерфейс (lpt)

- •Стандарти lpt

- •Стандарт ieee 1284

- •Формування циклів запису та читання в стандарті epp Діаграми сигналів у режимі epp

- •Лекція 15. Сучасні інтерфейси

- •15.1. Інтерфейс usb

- •Пристрої usb - функції та хаби

- •Типи передачі даних

- •15.2. Інтерфейс FireWire (ieee 1394)

- •Порівняння FireWire і usb

- •15.3. Радиоинтерфейс BlueTooth

- •15.4. Радіоінтерфейс Wi-Fi

- •15.5. Інтерфейс Wireless usb

- •Лекція 16. Внутрішні шини стандарту pc

- •16.1. Шина isa

- •16.2. Шина pci

- •16.3. Інтерфейс agp

- •16.4. Інтерфейс pci-Express 16x

- •Лекція 17. Пристрої зберігання даних

- •17.1. Основні характеристики зовнішніх накопичувачів

- •17.2. Структура дисків

- •Дефрагментация

- •Файлова система fat і ntfs

- •17.3. Типи накопичувачів

- •Гнучкі диски (Floppy)

- •Жорсткі диски (hd)

- •Твердотільні накопичувачі ssd (solid state drive)

- •Флэш-Накопичувачі (Flash-card)

- •Гибридные жёсткие диски(h-hdd)

- •Оптичні диски (cd)

- •Лекція 18. Сучасні технології зберігання даних

- •18.1. Raid-Системи

- •Основні поняття та визначення

- •18.3. Складні raid-Масиви

- •Частина 4. Комп'ютерні системи Лекція 19. Еволюція комп'ютерних архітектур 2-4 поколінь

- •19.1. Пеом на базі i286

- •19.2. Пеом на базі i386

- •19.3. Пеом на базі процесора i486

- •Лекція 20. Центральний процесор Pentium

- •20.1. Процесори Pentium першого покоління Процесор 80586 (Pentium)

- •Процесор 80686 (Pentium Pro)

- •20.2. Процесори Pentium другого та третього покоління

- •Лекція 21. Сучасні процесори Pentium

- •21.1. Процесор Pentium IV Перше покоління Pentium IV

- •Друге покоління Pentium IV

- •21.2. Багатоядерна архітектура Pentium d - Conroe

- •Процесори для мобільних систем

- •Лекція 22. Процесори фірми amd

- •22.1. Клони Intel

- •22.2. П'яте та шосте покоління (k5, k6)

- •Сімейство k5

- •Сімейство k6

- •22.3. Athlon - сьоме покоління процесорів

- •Лекція 23. Сучасні процесори фірми amd

- •23.1. Athlon64 - восьме покоління процесорів

- •23.2. Athlon64 x2 - дев'яте покоління процесорів

- •23.3. Phenom – деcяте покоління процесорів (Stars Core)

- •Лекція 24. Мультимедіа - Відеосистема

- •24.1. Технологія та стандарти відеосистеми Двовимірне зображення

- •Синтез тривимірного зображення

- •24.2. Відео карта

- •Лекція 25. Мультимедиа - Монітори

- •25.1. Монітори на основі епт (crt)

- •25.2. Рідкокристалічні монітори та проектори (lcd)

- •25.3. Плазмені дисплеї (Plasma Display Panel)

- •25.4. Електролюмінесцентні монітори (oeld)

- •25.5. Органічні світлодіодні монітори (oled)

- •Лекція 26. Мультимедіа - звуковідтворення

- •26.1. Технології та стандарти

- •Режим аудиоплейера

- •Режим редактора

- •Синтезатор звуків

- •Голосове керування рс

- •Стиск аудіоданих із втратами

- •Системи кодування аудіоданих

- •26.2. Апаратна реалізація аудиоканала

- •26.3. Акустична система

- •Лекція 27. Оптимальні конфігурації пэвм

- •27.1. Класифікація комп'ютерних систем

- •27.2. Критерій оптимальної конфігурації пэвм

- •27.3. Приклади оптимальних конфігурацій пеом

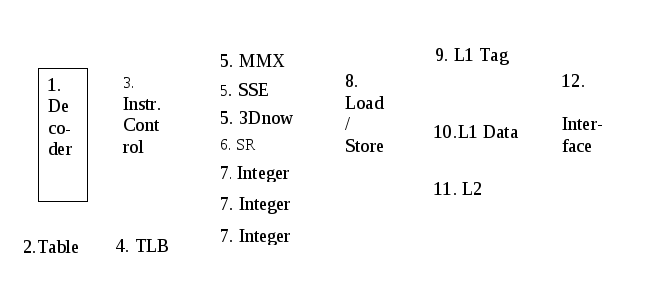

12.2. Структура сучасного процесора

На рис.12.2 дана структура сучасного процесора. Процесор містить наступні блоки:

1) Декодер команд CISC - RISC -Instrution Decoder.

2) Блок пророкування переходів та таблиця переходів - Prediction Table.

3) Блок розподілу інструкцій - Instrution Control (72-entry).

4) Регістри зберігання декодованих команд TLB (Translation Lookaside Buffer, буфер швидкого перетворення адреси).

5) Конвеєри із плаваючою крапкою FPU (MMX, SSE, 3Dnow!)

6) Регістри та блок їхнього швидкого перейменування - Stack Rename.

7) Конвеєр цілочисельних обчислень - Integer.

8) Блок вивантаження-завантаження даних - Load/Store.

9) L1 Tag - кеш 1-го рівня для зберігання інструкцій.

10) L1 Data - кеш 1-го рівня для зберігання даних.

11) L2 - кеш 2-го рівня.

12) Інтерфейс 64 біта - Interface.

Рис. 12.2. Структура сучасного процесора

У процесорі використовуються наступні технології:

1) Risk-Ядро. Для збільшення швидкодії в CPU CISC-Команди декодуються в RISC-подібні команди.

2) Конвеєр. Команда ділиться на стадії. Кожна стадія виконується окремим блоком. Блоки з'єднані в ланцюжок - конвеєр. Закономірність така: чим більше стадій конвеєра, тим простіше блоки та вище тактова частота. Однак велика кількість команд виконується одночасно і виникає проблема правильних переходів. Проблема вирішується пророкуванням переходів та вирішенням паралельного завдання під час перезавантаження конвеєра (Hyper Threading).

3) Суперскалярність – здатність виконувати багато команд одночасно.

4) Система пророкування переходів: статичне (визначене), динамічне (на основі отриманої раніше статистики переходів) та пророкування по припущенню – виконуються відразу кілька розгалужень.

5) Віртуальні регістри. Замість переміщення даних у регістрах міняються їхні імена.

6) Кеш-пам'ять. Зберігає проміжні обчислення та поточні команди.

7) MMX (Multi Media Extention – мультимедійне розширення).

8) Hyper Threading (многопотоковість). Застосовується в процесорах Pentium IV для кращого завантаження ядра при перезавантаженні конвеєра після помилки пророкування переходу.

9) SIMD – одна інструкція – багато даних. Технологія 3Dnow! використовується в процесорах AMD K6 та вище. SSE (Streaming SIMD Extensions), SSE2, SSE3 - прискорена обробка багатомірних масивів - використовується в процесорах Pentium та Athlon.

Процесор пов'язаний із зовнішнім світом через шинний інтерфейс із тактовою частотою FSB= 100-800МГц та розрядністю 64 біт. Ядро працює на частоті K*FSB, де K - коефіцієнт множення.

Існує оптимальне значення Kopt (Kopt=10...12 для процесорів Athlon XP) залежно від типу розв'язуваного завдання (потокові обчислення, наукові розрахунки), при якому система має максимальну швидкодію. Швидкодія також зростає при збільшенні обсягу кеш-пам'яті, та, мабуть, при зростанні FSB та розрядності.

Технології енергозбереження

DBS - технологія в Pentium 4 відключення компонентів на вимогу ( Enhanced Intel SpeedStep - Demand-Based Switching).

Cool'n Quiet - в Athlon64 зниження тактової частоти при зниженні навантаження на процесор.

C1E - поліпшений режим стану простою C1E (Enhanced Halt Mode).

ODCM - модуляція тактової частоти.

TM - Thermal Monitor.

TM1 - режим автоматичного захисту від перегріву.

TM2 - Thermal Monitor 2. Є заміною TM1 та у випадку сильного перегріву процесора знижує напруга живлення ядра та знижує множник частоти.