- •Новосибирский государственный

- •Оглавление

- •Введение

- •1. Система автоматического контроля

- •1.1. Функциональная схема сак

- •1.2. Классификация контрольно-измерительных приборов

- •1.3. Характеристики измерительных приборов

- •1.4. Основные элементы сак

- •1.4.1. Измерительные преобразователи (датчики)

- •1.4.2. Датчики перемещений

- •1.4.3. Датчики температуры

- •1.4.4. Датчики давления

- •1.4.5. Датчики расхода

- •1.4.6. Индукционные расходомеры

- •1.4.7. Датчики уровня

- •1.5. Методы измерений и измерительные схемы

- •1.5.1. Понятие о методах измерения

- •1.5.2. Мостовые измерительные схемы

- •1.5.3. Компенсационные измерительные схемы

- •1.5.4. Дифференциальная измерительная схема

- •2. Система автоматического управления

- •2.1. Функциональная схема сау электроприводом

- •2.2. Аппараты автоматического управления и защиты электроприводов

- •2.2.1. Командоаппараты

- •Кнопки управления

- •Путевые и конечные выключатели

- •Ртутные контакты

- •2.2.2. Реле Общие сведения и классификация реле

- •Электрические реле

- •2.2.3. Контакторы и магнитные пускатели

- •2.2.4. Аппараты защиты электроприводов

- •Реле максимального тока

- •2.3. Электрические схемы управления

- •2.3.1. Электрические схемы и их начертание

- •2.3.2. Электрическая схема управления задвижкой

- •2.3.3. Электрическая схема управления

- •2.3.4. Электрическая схема управления подпиточными насосами

- •2.3.5. Электрическая схема управления электродвигателем дымососа

- •2.3.6. Электрическая схема управления дутьевым вентилятором

- •2.3.7. Электрическая схема управления электродвигателем насоса сетевой воды

- •2.4. Электронные устройства и приборы в системах тГиВ

- •2.4.1. Общие сведения

- •2.4.2. Полупроводниковые приборы

- •2.4.3. Выпрямители

- •2.4.4. Усилители

- •2.4.5. Логические элементы

- •2.5. Микропроцессорные системы

- •2.6. Микропроцессорное управление электроприводами

- •3. Система автоматического регулирования

- •3.1. Понятие об автоматическом регулировании.

- •3.2. Основные свойства объектов регулирования

- •3.3. Динамические звенья сар

- •3.4. Типовые звенья сар и их характеристики

- •3.5. Структурная схема сар

- •3.6. Устойчивость линейных сар

- •3.7. Оценка качества регулирования линейных систем

- •3.8. Автоматические регуляторы

- •3.8.1. Классификация и законы регулирования

- •3.8.2. Выбор типа регулятора

- •Заключение

- •Библиографический список

2.4.5. Логические элементы

Это цифровые полупроводниковые устройства, выполненные на базе интегральных микросхем. Они выполняют определенные логические преобразования дискретных сигналов. Каждой комбинации входных сигналов соответствует на выходе сигнал, определяемый заданным правилам. При этом сигналы на входах и выходах могут иметь только два состояния, которым в соответствии с алгеброй логики присваиваются два символа – «1» (логическая единица) и «0» (логический нуль).

В технических и многих других практических приложениях логическая 1 – это знак того, что совершилось какое-то событие или ряд событий: замкнулись контакты и по цепи проходит ток, заработала аппаратура, принято решение, система выдержала испытания и т.д. В противоположность этому логический 0 означает, что контакты разомкнуты, аппаратура не работает, в цепи не проходит ток, проект отвергнут, система не выдержала испытания и т.д. [14].

Логические преобразования таких двоичных сигналов осуществляются на основе трех элементарных операций: ИЛИ – логическое сложение, дизъюнкция; И – логическое умножение, конъюнкция; НЕ – логическое отрицание, инверсия.

Основные логические функции, их элементы и схемы представлены в табл. 2.1 [12].

Число входов по ИЛИ и по И лежит в пределах от 2 до 16. Если имеющегося числа входов недостаточно, то для их увеличения используются интегральные схемы расширителей по ИЛИ, обозначаемые ЛД.

Таблица 2.1

Коэффициент разветвления по выходу характеризует нагрузочную способность логического элемента и определяется количеством входов однотипных элементов, которые можно подключить к выходу. В некоторых случаях в ТУ указывается максимальный выходной ток логического элемента.

Сигнал на выходе логического элемента задерживается относительно входного сигнала. Эта задержка определяет не только быстродействие цифровых схем, но и их работоспособность. Время задержки принято определять по уровню 0,5 U и 0,5 Uвых. При этом задержка переднего фронта и в результате длительность импульса на входе оказывается отличной от длительности импульса на выходе.

Мощность, потребляемая логической ИМС, обычно зависит от сигналов, поданных на входы. Для сравнения потребляемой ИМС мощности пользуются понятием средней мощности Pср, потребляемой базовым логическим элементом во включенном и выключенном состояниях. Это позволяет сравнить по потребляемой мощности логические ИМС различных серий.

Л огический

элемент может иметь один или несколько

входов и один выход. Количество возможных

комбинаций входных сигналов зависит

от количества входов логического

элемента и определяется по формуле:

огический

элемент может иметь один или несколько

входов и один выход. Количество возможных

комбинаций входных сигналов зависит

от количества входов логического

элемента и определяется по формуле:

N 2n,

где N — количество возможных комбинаций входных сигналов; 2 — количество состояний каждого из входов (0 или 1); n — количество входов логического элемента.

В табл. 2.2 показаны операции логических элементов ИЛИ, И, НЕ, а также символические записи соответствующих операций и алгоритмы работы в виде таблиц.

Таблица 2.2

|

Операция ИЛИ у = х1 + х2 |

Операция И у = х1 · х2 |

Операция НЕ

у

=

|

|

Вход 1:Вход 2: Выход |

Вход 1:Вход 2: Выход |

Вход: Выход |

|

0

0

1

1

|

0

0

1

1

|

0 = 1 1 = 0 – – |

На практике чаще применяют комбинированные логические элементы, реализующие последовательно выполненные две и более логических операции (см. табл. 2.1).

В настоящее время наибольшее распространение получили логические элементы, выполненные в виде интегральных микросхем (ИМС) на основе биполярных или МОП-транзисторов.

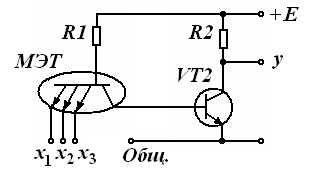

На рис. 2.48 приведен пример схемного решения элемента 3И–НЕ на основе многоэмиттерного транзистора (МЭТ).

Схема работает следующим образом. Если на все входы х1, х2, и х3 элемента поданы напряжения, соответствующие уровню 1, то ток эмиттерных переходов МЭТ будет стремиться к нулю. При этом ток через резистор R1 и прямо смещенный переход МЭТ в базу транзистора VT2 достаточно велик и транзистор VT2 полностью открыт. Сопротивление транзистора VT2 (перехода коллектор – эмиттер) в открытом состоянии значительно меньше сопро-

Рис. 2.48. Схема логического элемента 3И–НЕ

тивления последовательно включенного с ним резистора R2. Поэтому почти все напряжение Е, приложенное к последовательной цепи резистор R2 – транзистор VT2, окажется приложенным к резистору R2. На коллекторе VT2, то есть на выходе элемента у, напряжение будет стремиться к нулю. Таким образом, сигнал 0 может быть на выходе такой схемы только при наличии на всех входах сигнала 1.