podyak

.pdf2. Описание исследуемых схем

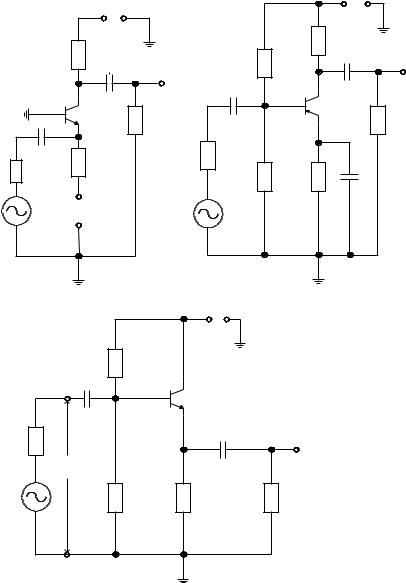

Схема каскада с ОБ показана на рис. 1. Входной сигнал на усилитель подается через емкость С1 в цепь эмиттера транзистора. В цепь эмиттера задается ток покоя транзистора с помощью отдельного источника Еэ и резистора Rэ. Выходное напряжение снимается с резистора Rк в коллекторной цепи и поступает через конденсатор С2 на нагрузку Rн. Усилитель по схеме с ОЭ показан на рис. 2. Здесь необходимое смещение базы задается с помощью делителя на резисторах R1 и R2. Резистор Rэ включен для стабилизации рабочей точки транзистора, положение которой зависит от температурных изменений характеристик транзистора (IК0, β, UБЭ). Для устранения возникающей при этом отрицательной обратной связи по току в полосе пропускания резистор Rэ шунтируется емкостью Сэ. Назначение элементов коллекторной цепи каскада такое же, как и в схеме с ОБ.

Включение транзистора в схеме с ОК показано на рис. 3. Здесь входной сигнал подается в цепь базы, а выходной сигнал снимается с эмиттера и через конденсатор С2 передается в нагрузку. В схеме с ОЭ возникает стопроцентная обратная связь по напряжению. Это приводит к увеличению входного сопротивления и уменьшению выходного. Коэффициент усиления по напряжению оказывается меньше единицы и зависит от коэффициентов согласования во входной и выходной цепях. Элементы цепи смещения такие же, как в схеме с ОЭ, способствуют стабилизации рабочей точки транзистора.

4. Расчетное задание

Для каждой из трех схем выполнить расчет:

•по постоянному току в режиме покоя (определить положение рабочей точки);

•основных характеристик усилителя (коэффициента усиления K0, граничных частот, диапазонов входных и выходных напряжений).

Таблица исходных данных для расчета

Схема |

Rг |

R1 |

R2 |

Rк |

Rэ |

Rн |

С1 |

С2 |

Сэ |

Ек(Еэ) |

включения |

|

|

кОм |

|

|

|

мкФ |

|

В |

|

|

|

|

|

|

|

|

|

|

|

|

ОБ |

0.5 |

|

|

6.8 |

15 |

12 |

10.0 |

0.25 |

|

15 |

|

|

|

|

|

|

|

|

|

|

|

ОЭ |

0.5 |

120 |

51 |

6.8 |

0.22 |

12 |

1.0 |

0.25 |

10.0 |

15 |

|

|

|

|

|

|

|

|

|

|

|

ОК |

0.5 |

51 |

51 |

|

2.2 |

5.1 |

0.25 |

1.0 |

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

130 |

|

|

|

|

|

|

+ Ек- |

|

+ |

Ек - |

|

|

|

|

|

|

|

|

Rк |

|

Rк |

C2 |

R1 |

C2 |

Uвых |

Uвых |

|

|

||

|

|

|

||

|

|

|

|

|

|

|

С1 |

VT |

|

VT |

|

|

|

|

|

|

|

|

|

|

|

Rн |

|

Rн |

С1 |

Rэ |

Rг |

|

Сэ |

R2 |

|

|||

Rг |

|

Rэ |

|

|

|

|

|

||

|

|

|

|

|

|

- |

|

|

|

Ег |

Еэ |

Ег |

|

|

+ |

|

|

||

|

|

|

|

|

Рис. 1 |

|

+ |

_ |

Рис. 2 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

Ек |

|

|

|

R1 |

|

|

|

|

|

C1 |

VT |

|

|

|

|

|

|

|

|

|

Rг |

|

|

|

С2 |

Uвых |

|

|

|

|

|

|

|

Uвх |

|

|

|

|

Ег |

R2 |

Rэ |

|

Rн |

|

|

|

|

|

|

Рис. 3

131

5.Программа эксперимента

1.Собрать схему, показанную на рис. 1, согласно данным, приведенным в таблице.

2.Измерить режим работы транзистора по постоянному току.

3.Оценив область средних частот, снять амплитудную характеристику усилителя и определить максимальные входной и выходной сигналы.

4.Снять частотную характеристику усилителя в режиме малого сигнала. Определить коэффициент усиления по напряжению и по току

вобласти средних частот.

5.Собрать схему, показанную на рис. 2, согласно данным таблицы. Повторить эксперименты, описанные в пп. 2–4.

6.Собрать схему, показанную на рис. 3, согласно данным, приведенным в таблице. Повторить эксперименты, описанные пп. 2–4.

5.Контрольные вопросы

1.Как находятся элементы Т-образной схемы замещения транзи-

стора?

2.Как составляются эквивалентные схемы усилительных каска-

дов?

3.Как по эквивалентной схеме каскада усиления рассчитать основные характеристики усилителя?

4.Как рассчитать граничные частоты усилителя с емкостной связью?

5.Как определить постоянные времени τα и τβ транзистора по данным, приводимым в справочниках?

6.Как зависят частотные свойства транзистора от режима по постоянному току?

7.Как выглядят наиболее важные зависимости параметров транзистора от температуры?

8.Как зависят динамические параметры транзистора от режима по постоянному току?

9.Какие есть приемы температурной стабилизации усилителя?

10.Почему в схеме с ОК динамический диапазон входных сигна-

лов больше, чем в схемах с ОБ и ОЭ?

11. В чем причина появления нелинейных искажений в усилителях?

132

12.Какие существуют ограничения при выборе рабочего режима транзистора?

13.Почему в справочниках характеристики транзистора приводятся в системе h-параметров?

Ли т е р а т у р а

1.Степаненко И.П. Основы теории транзисторов и транзисторных схем. –

М.: Энергия, 1973. (разд. 6.1–6.3, 7.1–7.4, 9.2, 10.1–10.2).

2.Микросхемотехника: учеб. пособие. Ч. 2 / Е.А. Подъяков, В.В. Орлик, С.В. Брованов. – Новосибирск: Изд-во НГТУ, 2003.

ЛАБОРАТОРНАЯ РАБОТА № 3

ИССЛЕДОВАНИЕ ОДНОКАСКАДНЫХ УСИЛИТЕЛЕЙ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ

1. Цель работы

Изучение свойств усилителей с емкостной связью, собранных на полевых транзисторах с управляющим p–n-переходом: однокаскадного усилителя по схеме с общим истоком (ОИ) и однокаскадного усилителя по схеме с общим стоком (ОС). Знакомство с особенностями статических характеристик полевого транзистора, выбором рабочего режима и расчетом цепей смещения. Расчет и измерение амплитудных и частотных характеристик.

2. Описание исследуемых схем

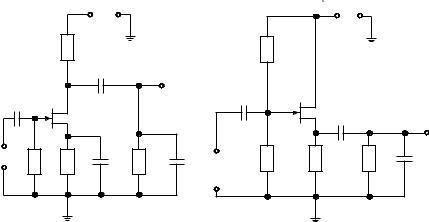

Схема однокаскадного усилителя с ОИ показана на рис. 1. Входной сигнал поступает на затвор транзистора через конденсатор С1. Исходный потенциал затвора фиксируется на уровне нуля с помощью сопротивления утечки RЗ. Напряжение смещения затвор–исток в этой схеме называют автоматическим, так как оно появляется на резисторе RИ от протекания тока истока. Возникающая при этом отрицательная обратная связь по току приводит к уменьшению коэффициента усиления каскада. Поэтому в полосе пропускания обратную связь устраняют путем шунтирования сопротивления RИ емкостью СИ. Выходное напря-

133

жение схемы формируется в цепи стока на резисторе RС и передается на нагрузку через разделительный конденсатор С2.

На рис. 2 приведена схема каскада с ОС. Нагрузка здесь включена в цепь истока через разделительный конденсатор С2. Смещение также автоматическое с помощью резистора RИ. Для выравнивания диапазонов положительных и отрицательных входных сигналов на затвор задается дополнительное положительное смещение с помощью делителя на резисторах R1 и R2. В схеме возникает стопроцентная отрицательная обратная связь по напряжению, что обеспечивает самое высокое входное и наиболее низкое выходное сопротивления по отношению к другим каскадам усиления.

3. Расчетное задание

Для каждой из двух схем выполнить расчет:

–по постоянному току в режиме покоя (определить положение рабочей точки);

–по переменному току найти K0, граничные частоты, диапазоны входных и выходных напряжений.

Таблица исходных данных для расчета

Схема |

|

|

|

|

Обозначение элемента |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

RЗ |

R1 |

R2 |

|

RИ |

RC |

Rн |

С1 |

С2 |

СИ |

ЕС |

|

включения |

|

||||||||||

|

|

|

кОм |

|

|

|

мкФ |

|

В |

||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

ОИ |

51 |

|

|

|

0.75 |

1.3 |

5.1 |

0.01 |

0.25 |

10.0 |

15 |

|

|

|

|

|

|

|

|

|

|

|

|

ОС |

|

120 |

51 |

|

6.8 |

|

12 |

0.01 |

0.25 |

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

4.Программа эксперимента

1.Собрать схему, приведенную на рис. 1, согласно данным таблицы.

2.Измерить режим работы транзистора по постоянному току.

3.Оценив область средних частот, снять амплитудную характеристику усилителя и определить максимальные входные и выходные сигналы.

4.В режиме малого сигнала снять частотную характеристику усилителя. Определить коэффициенты усиления по напряжению и току в области средних частот.

5.Собрать схему, приведенную на рис. 2, согласно данным таблицы. Повторить эксперименты, описанные в пп. 2–4.

134

|

|

Ек |

|

|

|

Ек |

|

|

|

|

|

|

|

|

|

|

|

+ |

|

|

|

+ |

|

|

|

|

|

|

|

|

|

|

Rк |

|

|

|

R1 |

|

|

|

|

С2 |

|

|

|

|

|

|

|

|

|

Uвых |

|

|

|

|

|

|

|

|

С1 |

VT |

|

С1 |

VT |

|

|

|

|

|

|

|

|

|

|

|

C2 |

|

|

|

|

|

|

|

|

Uвых |

|

|

|

|

|

|

|

|

|

Uвх Rз |

Rи |

Си |

Rн |

Сн |

R2 |

Rи |

|

|

|

||||||

|

|

|

|

|

Сн |

||

|

|

|

|

|

Uвх |

Rн |

|

|

|

|

|

|

|

|

Рис. 1 |

Рис. 2 |

6.Контрольные вопросы

1.Как работает полевой транзистор с управляющим p–n-переходом?

2.Как представляется эквивалентная схема полевого транзистора?

3.Как составить эквивалентную схему усилителя на полевом транзисторе?

4.Как выбирается режим работы полевого транзистора?

5.Как найти параметры схемы замещения полевого транзистора?

6.Как рассчитать полосу пропускания усилителя?

7.Как рассчитать входную емкость усилителя на полевом транзи-

сторе?

8.Как рассчитать выходное сопротивление каскада в схеме с ОИ?

9.В чем состоят наиболее сильные отличия схем с ОИ и ОС?

10. Какие виды обратных связей есть в исследованных схемах? Как они влияют на работу усилителей?

Ли т е р а т у р а

1.Степаненко И.П. Основы теории транзисторов и транзисторных схем. – М.: Энергия, 1973.

2.Микросхемотехника: учеб. пособие. Ч. 2 / Е.А. Подъяков, В.В. Орлик, С.В. Брованов. – Новосибирск: Изд-во НГТУ, 2003.

135

ЛАБОРАТОРНАЯ РАБОТА № 4

ИССЛЕДОВАНИЕ КАСКАДОВ УСИЛИТЕЛЕЙ ПОСТОЯННОГО ТОКА

1. Цель работы

Изучение особенностей построения и свойств, характерных для схемотехники усилителей постоянного тока (УПТ) элементарных ячеек: дифференциального усилителя (ДУ), схемы сдвига уровня и выходного каскада.

Экспериментальное определение основных усилительных параметров ДУ для двух способов стабилизации суммарного эмиттерного тока, исследование частотных и амплитудных характеристик схем. Результаты экспериментов сопоставляются с полученными из расчета данными.

2. Описание исследуемых схем

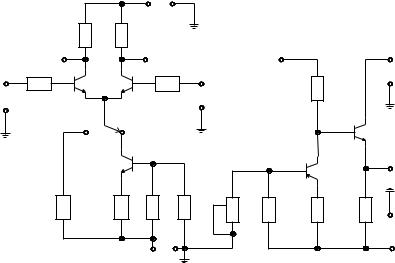

Схема ДУ постоянного тока показана на рис. 1. Усилитель собран по мостовой (балансной) схеме на транзисторах VT1, VT2 с источником тока в цепи эмиттеров, роль которого может выполнять или резистор Rэ1, или транзистор VT3, включенный источником тока. Переключение варианта условно показано с помощью переключателя П. С помощью источника тока задается смещение транзисторов VT1 и VT2 со стороны эмиттеров, как в схеме с общей базой. Базы транзисторов при этом подключены через резисторы RГ1 и RГ2, являющиеся внутренними сопротивлениями источников входных напряжений, к общей (нулевой) шине.

Выходное напряжение может сниматься как между коллекторами VT1 и VT2 (балансный или симметричный выход), так и с одного из коллекторов относительно общей шины (несимметричный выход).

На рис. 2 показан вариант схемы сдвига уровня и выходной каскад УПТ. Схема сдвига уровня собрана на транзисторе VT4 и резисторе R3. Ее назначение в том, чтобы сместить исходный (ненулевой) уровень напряжения с выхода УПТ (коллектор VT2) на уровень базового напряжения транзистора VT5 так, чтобы исходное напряжение на выходе усилителя мощности на транзисторе VT5 было равно нулю. Это означает, что выходное напряжение схемы сдвига уровня должно быть равно напряжению на базоэмиттерном переходе транзистора VT5, т. е.

136

примерно +0,65 В. Вследствие высокого сопротивления коллекторной цепи VT4 для переменного тока по отношению к резистору R3 полезный (усиленный) сигнал будет передаваться без ослабления. Для согласования относительно низкоомной нагрузки с высокоомным выходным сопротивлением схемы сдвига уровня применен выходной каскад на транзисторе VT5 по схеме с ОК.

Для исследования схемы сдвига уровня ее следует подключить к выходу ДУ, например, к коллектору транзистора VT2. В эмиттерной цепи транзисторов VT1 и VT2 при этом следует включить резистор Rэ1.

3. Расчетное задание

Для схем, приведенных на рис. 1 и 2, выполнить расчет:

•по постоянному току в режиме покоя;

•дифференциального и синфазного коэффициентов передачи;

•верхней граничной частоты полосы пропускания. Исходные данные для расчета взять из таблицы.

Таблица исходных данных для расчета

Rк1,2 |

RГ1,2 |

Rэ1 |

Rэ2 |

R1 |

R2 |

R3 |

R4 |

R5 |

R6 |

P |

Eк, Eэ |

|

|

|

|

|

кОм |

|

|

|

|

|

В |

|

|

|

|

|

|

|

|

|

|

|

|

6.8 |

1 |

5.6 |

0.22 |

1 |

10 |

33 |

10 |

3.3 |

6.8 |

20 |

+ /–12 |

|

|

|

|

|

|

|

|

|

|

|

|

4.Программа работ

4.1.Дифференциальный усилитель

1.Собрать схему, показанную на рис. 1, при включенном транзисторе VT3 по данным, приведенным в таблице.

2.Измерить режим работы транзисторов по постоянному току, заземлив входные зажимы Вх1 и Вх2. Все измерения выполнять относительно общей шины. При относительно большой разнице коллекторных напряжений дифференциальной пары балансировать схему, изменяя величину резистора RГ2.

3.Исследовать дифференциальный каскад в режиме дифференциального сигнала. Для этого подать на вход 1 напряжение генератора относительно общей шины, а вход 2 подключить к общей шине. На

137

частоте 1 кГц снять амплитудную характеристику. Определить дифференциальный коэффициент усиления и динамический диапазон входных и выходных сигналов.

4.Установить режим малого сигнала и снять частотную характеристику.

5.Исследовать каскад в режиме синфазного сигнала. Для этого объединить входы 1 и 2 и подключить к ним генератор сигналов относительно общей шины. На частоте 1 кГц снять амплитудную характеристику. Определить коэффициент передачи синфазного сигнала, установив на входах максимальный синфазный сигнал, но не выходящий за пределы линейного режима.

6.Отключить генератор тока на VT3 в цепи эмиттеров VT1 и VT2 и подключить резистор Rэ1. Измерить режим по постоянному току и, убедившись, что он не отличается существенно от предыдущего, выполнить исследования по пп. 3–5.

4.2.Схема сдвига уровня и выходной каскад

1.Собрать схему по рис. 2 по данным таблицы.

|

|

Ек |

|

|

|

|

|

+ |

- |

|

|

|

|

Rк |

Rк |

|

|

|

|

|

Uвых1 |

Uвых2 |

|

|

|

+ |

|

|

|

|

|

|||

|

|

|

Uвх |

|

|

|

|

|

|

Rг2 |

|

|

|

Rг1 VT1 |

VT2 |

|

|

|

Ек |

|

|

|

|

|

|||

Uвх1 |

|

|

|

R3 |

|

|

|

|

|

Uвх2 |

|

|

|

|

|

|

|

|

|

|

|

П |

|

|

|

VT5 |

|

|

|

|

|

|

|

|

|

|

|

|

VT4 |

|

|

|

|

|

|

|

|

Uвых |

|

|

|

|

P |

|

|

|

R1 |

R2 |

R4 |

|

|

|

|

|

|

|

|

||

Rэ1 |

Rэ2 |

|

|

|

|

|

|

|

|

R5 |

R6 |

+ |

|

|

|

|

|

|||

|

|

|

|

|

|

Еэ |

|

- |

|

+ |

|

|

- |

|

|

|

|

|

||

|

|

Еэ |

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 1 |

|

|

Рис. 2 |

|

|

138

2.Подключить схему к выходу дифференциального каскада (коллектор VT2 на рис. 1). С помощью потенциометра P установить на выходе схемы сдвига уровня нулевой потенциал. Измерить режим по постоянному току.

3.На частоте 1 кГц снять амплитудную характеристику и осциллограммы напряжений на эмиттере и базе транзистора VT5 и коллекторе транзистора VT2.

5.Контрольные вопросы

1.Могут ли на входах дифференциального каскада присутствовать одновременно дифференциальный и синфазный сигналы?

2.Какие преимущества дает использование генератора стабильного тока в эмиттерах дифференциального каскада?

3.Что такое смещение нулевого уровня и каковы причины его возникновения?

4.От чего зависит полоса пропускания дифференциального кас-

када?

5.Почему желательно иметь большой дифференциальный коэффициент усиления и небольшой синфазный коэффициент?

6.Какие виды обратных связей есть в исследованных схемах?

Ли т е р а т у р а

1.Степаненко И.П. Основы теории транзисторов и транзисторных схем. – М.: Энергия, 1973.

2.Подъяков Е.А., Орлик В.В., Брованов С.В. Электронные цепи и микро-

схемотехника : учеб. пособие. Ч. 2. – Новосибирск: Изд-во НГТУ, 2003.

139