- •Вступление

- •Основные задачи технической диагностики

- •Системы диагноза технического состояния

- •Диагностические системы управления

- •Объекты диагноза

- •Математические модели объектов диагноза

- •Функциональные схемы систем тестового и функционального диагноза

- •Методы и технические средства диагностирования элементов и устройств вычислительной техники и систем управления Общие сведения

- •Тестовое тестирование узлов, блоков и устройств.

- •Структуры автоматизированных систем.

- •Программное обеспечение процессов диагностирования.

- •Логические анализаторы.

- •Микропроцессорные анализаторы (ма).

- •Способы запуска.

- •Подключающие устройства.

- •Ввод начальных данных.

- •Проверка отдельных триггеров.

- •Проверка содержимого постоянных запоминающих устройств (пзу).

- •Проверка оперативных запоминающих устройств (озу).

- •Проверка работы линии коллективного пользования (лкп).

- •Проверка аналого-цифровых преобразователей (ацп).

- •Проверка печатных плат.

- •Проверка микропроцессорной системы.

- •Сигнатурные анализаторы

- •Процесс формирования сигнатур.

- •Аппаратурная реализация сигнатурного анализатора.

- •Тестовое диагностирование устройств в составе эвм.

- •Диагностирование оборудования процессоров.

- •Способы диагностирования периферийных устройств.

- •Диагностирование упу/пу с помощью процессора.

- •Проверки упу/пу с помощью диагностических приказов.

- •Диагностирование упу/пу с помощью тестеров.

- •Способы тестирования зу.

- •Принципы построения стандартных проверяющих тестов полупроводниковых зу.

- •Аппаратурные средства функционального диагностирования узлов и блоков. Основные принципы построения.

- •Кодовые методы контроля.

- •Контроль передач информации.

- •Контроль по запрещенным комбинациям.

- •Самопроверяемые схемы контроля.

- •Контроль по модулю

- •Организация аппаратурного контроля озу.

- •Организация аппаратурного контроля внешних зу.

- •Средства функционального диагностирования в составе эвм.

- •Контроль методом двойного или многократного счета

- •Экстраполяционная проверка

- •Контроль по методу усеченного алгоритма (алгоритмический контроль).

- •Способ подстановки.

- •Проверка предельных значений или метод "вилок".

- •Проверка с помощью дополнительных связей.

- •Метод избыточных переменных

- •Контроль методом обратного счета.

- •Метод избыточных цифр.

- •Метод контрольного суммирования.

- •Контроль методом счета записи.

- •Контроль по меткам

- •Метод обратной связи

- •Метод проверки наличия формальных признаков (синтаксический метод, метод шаблонов).

- •Метод проверки запрещенных комбинаций.

- •Метод an-кодов

- •Методы на основе циклических кодов и кодов Хэмминга и др.

- •Структурные методы обеспечения контролепригодности дискретных устройств.

- •Введение контрольных точек.

- •Размножение контактов.

- •Использование блокирующей логики.

- •Применение параллельных зависимых проверок

- •Замена одним элементом состояний группы элементов памяти.

- •Методы улучшения тестируемой бис. Сокращение числа тестовых входов.

- •Двухуровневое сканирование.

- •Микропроцессорные встроенные средства самотестирования.

- •Контроль и диагностирование эвм Характеристики систем диагностирования

- •Системы контроля в современных эвм

- •Применение аналоговых сигнатурных анализаторов

- •Работа локализатора неисправностей pfl780 в режиме "Pin by Pin"

- •Работа в режиме Pin by Pin

- •Работа с торцевыми разъемами

- •Среда тестирования

- •Индивидуальное тестирование или режим Pin by Pin?

- •Тестирование специальных устройств

- •Устранение ложных отказов путем использования эталонных сигнатур компонентов от разных производителей

- •Тестирование цифровых компонентов методом asa

- •Вариации сигнатур.

- •Входные цепи защиты

- •Набор альтернативных сигнатур

- •Тестирование подключенных к общей шине компонентов путем их изоляции специальными блокирующими напряжениями.

- •Системы с шинной архитектурой

- •Устройства с тремя логическими состояниями

- •Разрешение работы и блокирование компонентов

- •Применение "блокирующих" напряжений

- •Отключение тактовых импульсов.

- •Отключение шинных буферов.

- •Опция Loop until Pass

- •Локализация дефектных компонентов в системах с шинной архитектурой без их удаления из испытываемой цепи

- •Поиск неисправностей методами asa и ict в системах с шинной архитектурой

- •Сравнение шинных сигнатур

- •Шинные сигнатуры

- •Изоляция устройств.

- •Локализация коротких замыканий шины и неисправностей нагрузки прибором toneohm 950 в режиме расширенного обнаружения неисправностей шины

- •Типы шинных неисправностей

- •Короткие замыкания с низким сопротивлением

- •Измерение протекающего через дорожку тока.

- •Измерение напряжения на дорожке печатной платы

- •Обнаружение кз и чрезмерных токов нагрузки в труднодоступных для тестирования местах

- •Короткие замыкания на платах

- •Обнаружение сложных неисправностей тестируемой платы путем сравнения импедансных характеристик в режиме asa

- •Импедансные сигнатуры

- •Локализация неисправностей методом Аналогового сигнатурного анализа

- •Методы сравнения

- •Основы jtag Boundary Scan архитектуры

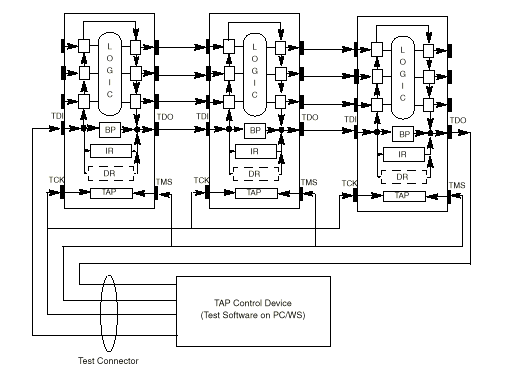

- •АрхитектураBoundaryScan

- •Обязательные инструкции

- •Как происходитBoundaryScanтест

- •Простой тест на уровне платы

- •Граф состояний тар – контроллера

- •Мониторинг сети Управление сетью

- •Предупреждение проблем с помощью планирования

- •Утилиты мониторинга сети

- •Специальные средства диагностики сети

- •Источники информации по поддержке сети

- •Искусство диагностики локальных сетей

- •Организация процесса диагностики сети

- •Методика упреждающей диагностики сети

- •Диагностика локальных сетей и Интернет Диагностика локальных сетей

- •Ifconfig le0

- •Сетевая диагностика с применением протокола snmp

- •Диагностика на базеIcmp

- •Применение 6-го режима сетевого адаптера для целей диагностики

- •Причины циклов пакетов и осцилляции маршрутов

- •Конфигурирование сетевых систем

- •Методы тестирования оптических кабелей для локальных сетей.

- •Многомодовый в сравнении с одномодовым

- •Нахождение разрывов

- •Измерение потери мощности

- •Использование тестовOtdRдля одномодовых приложений

- •Источники

- •Словарь терминов а

Простой тест на уровне платы

Одним из первых тестов, проводимых для печатной платы, должен являться так называемый тест инфраструктуры. Этот тест используется для того, чтобы установить, все ли компоненты смонтированы правильно. При этом тесте два последних бита регистра инструкций (IR) всегда равны «01». «Выдвигая» содержимое IR каждого устройства в цепочке, можно различить, правильно ли установлена микросхема. Это достигается последовательным чтением

Рис. 3 Одиночная Boundary Scan цепочка на плате.

IR регистра посредством ТАР – контроллера.

После успешного завершения предыдущего теста, начинается тес проверки соединений компонентов. Ищутся обрывы или замыкания. Тестовые последовательности предустанавливаются на выводы, работающие на выход. Используется команда EXTEST. Эти последовательности попадают на входы следующих элементов и сдвигаются в последовательном коде на TDO для последующего анализа.

Тестовые образцы генерируются и анализируются программным образом. Пример программ подобного типа - Automatic Test Pattern Generation (ATPG) или Boundary scan Test Pattern Generation (BTPG).

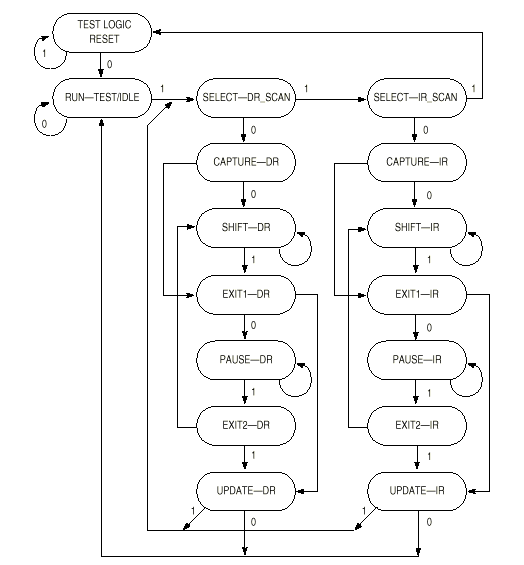

Граф состояний тар – контроллера

ТАР

– контроллер отвечает за интерпретацию

логических значений сигнала TMS.

Он является синхронным цифровым

автоматом, контролирующим JTAG

– логику. Значения, указанные на графе

рядом с состояниями (помечены овалами),

отражают значение сигнала TMS,

стробируемое положительным фронтом

сигнала ТСК (см. рис. 4).

Рис. 4. Граф состояний ТАР – контроллера

Как видно из графа, TAP-контроллер перейдет в исходное состояние RESET из любого другого не более чем за 5 импульсов TCK при TMS=1. При этом произойдет сброс всей схемы BST, а в регистр инструкций запишется значение по умолчанию (как правило, инструкция IDCODE, но может и другая, например, SAMPLE. Во избежание этого сброса следует проводить контроллер TAP через безопасное состояние IDLE, в котором все рабочие установки сохраняются.

Схема ВST содержит целый набор сдвиговых регистров. При проходе по правой ветви графа доступен регистр инструкций длиной от 3 бит. Загруженная инструкция определяет один из регистров данных, доступных при проходе по левой ветви и действия с ними в определенных состояниях TAP-контроллера. Из этих регистров, как минимум, в наличии обычно имеются регистр доступа к внешним выводам чипа и однобитный регистр обхода.

Поскольку в цепочке JTAG-устройств все сдвиговые регистры складываются в один длинный, то регистр обхода позволяет уменьшить эту длину, представляя обойденные устройства всего одним битом. Для этого служит инструкция BYPASS. Поскольку ввод инструкции BYPASS отменяет действие ранее загруженной инструкции, к сожалению, невозможно сохранить состояние блоков ввода-вывода, устанавливаемое инструкциями типа EXTEST и INTEST. Исключением является инструкция CLAMP, после которой можно использовать регистр обхода. Но эта инструкция практически не встречается.

В регистре доступа для каждого блока ввода-вывода ПЛИС, как правило, отведены три последовательных бита: вход (I), выход (O) и запрет выхода (T). Порядок вывода бит на TDO различен для ПЛИС разных фирм. Например, для Xilinx - (T,O,I), а для Altera - (I,T,O).

В состоянии CAPTURE в выбранный сдвиговый регистр записывается текущее состояние. Кстати, для регистра инструкций обычно это код инструкции SAMPLE, а для регистра обхода - логическая единица. В состоянии UPDATE данные из сдвигового регистра переписываются в соответствующий регистр хранения.

Таким образом инструкция SAMPLE не только считывает текущее состояние внешних выводов, но и записывает в регистре хранения управляющие данные. Поэтому, чтобы избежать вывода случайной информации, ее используют перед загрузкой инструкций типа EXTEST или INTEST.

При загрузке инструкции EXTEST выходы регистра хранения определяют состояние выходов чипа, т.е. управляют выходом и его третьим состоянием. Таким образом можно протестировать внешние межсоединения. Инструкция INTEST, напротив, подменяет сигнал вводимый внутрь чипа и служит для проверки самого чипа. Часто обходятся одной инструкцией EXTEST, используя бит входа (I) для ввода в чип как в инструкции INTEST.

Инструкция IDCODE подключает встроенный 32-битный регистр с идентификаторами производителя, модели и версии устройства. Формат регистра представлен в табл. 2.

Таблица 2.

|

Version |

Part Number |

Manufacturer Identity |

Fixed "1" |

|

Биты 31-28 |

Биты 27-12 |

Биты 11-1 |

Бит 0 |

Выводы

Итак, стандарт IEEE 1149.1, известный как Test Access Port and Boundary Scan Architecture, явил собой новое слово в технике тестирования и контроля высокотехнологичных современных полупроводниковых устройств. Он воплотил в себя теоретические разработки группы компаний и отдельных инженеров, организовавших специальную организацию JTAG. В самых общих словах, стандарт устанавливает следующие положения:

Любое полупроводниковое устройство, совместимое с JTAG, включает в себя, помимо основной логики, специальные Boundary Scan соты, которые в нормальном режиме не влияют на работу схемы, а в активном – являются генераторами и приемниками тестовых сигналов.

По возможности, каждый логический вывод микросхемы должен иметь свою Boundary Scan соту.

Boundary Scan соты управляются ТАР – контроллером, имеющим всего четыре ножки управления, а опционально – пять.

ТАР – контроллер имеет стандартный минимум команд, поступающих на его входы в последовательном коде от персональной ЭВМ либо другого устройства, позволяющий организовать различные режимы работы Boundary Scan соты.

Таким образом, для устройств, собранных на элементах, отвечающих рекомендациям стандарта IEEE 1149.1, значительно упрощаются процедуры, связанные с тестированием, контролем и диагностикой. Не требуется разрушать связи на печатной плате, подключать внешние схемы контроля (тестеры, осциллографы и т.д.). Достаточно лишь через специальный разъем подключить ЭВМ и, воспользовавшись готовой или самостоятельно написанной программой, снимать и устанавливать любые логические значения и режимы работы микросхем в проверяемом устройстве. В результате диагностики, к примеру, можно получить данные не только о том, какой элемент неисправен, но и какой его логический выход (либо цепь, являющаяся для него нагрузкой).