- •Вступление

- •Основные задачи технической диагностики

- •Системы диагноза технического состояния

- •Диагностические системы управления

- •Объекты диагноза

- •Математические модели объектов диагноза

- •Функциональные схемы систем тестового и функционального диагноза

- •Методы и технические средства диагностирования элементов и устройств вычислительной техники и систем управления Общие сведения

- •Тестовое тестирование узлов, блоков и устройств.

- •Структуры автоматизированных систем.

- •Программное обеспечение процессов диагностирования.

- •Логические анализаторы.

- •Микропроцессорные анализаторы (ма).

- •Способы запуска.

- •Подключающие устройства.

- •Ввод начальных данных.

- •Проверка отдельных триггеров.

- •Проверка содержимого постоянных запоминающих устройств (пзу).

- •Проверка оперативных запоминающих устройств (озу).

- •Проверка работы линии коллективного пользования (лкп).

- •Проверка аналого-цифровых преобразователей (ацп).

- •Проверка печатных плат.

- •Проверка микропроцессорной системы.

- •Сигнатурные анализаторы

- •Процесс формирования сигнатур.

- •Аппаратурная реализация сигнатурного анализатора.

- •Тестовое диагностирование устройств в составе эвм.

- •Диагностирование оборудования процессоров.

- •Способы диагностирования периферийных устройств.

- •Диагностирование упу/пу с помощью процессора.

- •Проверки упу/пу с помощью диагностических приказов.

- •Диагностирование упу/пу с помощью тестеров.

- •Способы тестирования зу.

- •Принципы построения стандартных проверяющих тестов полупроводниковых зу.

- •Аппаратурные средства функционального диагностирования узлов и блоков. Основные принципы построения.

- •Кодовые методы контроля.

- •Контроль передач информации.

- •Контроль по запрещенным комбинациям.

- •Самопроверяемые схемы контроля.

- •Контроль по модулю

- •Организация аппаратурного контроля озу.

- •Организация аппаратурного контроля внешних зу.

- •Средства функционального диагностирования в составе эвм.

- •Контроль методом двойного или многократного счета

- •Экстраполяционная проверка

- •Контроль по методу усеченного алгоритма (алгоритмический контроль).

- •Способ подстановки.

- •Проверка предельных значений или метод "вилок".

- •Проверка с помощью дополнительных связей.

- •Метод избыточных переменных

- •Контроль методом обратного счета.

- •Метод избыточных цифр.

- •Метод контрольного суммирования.

- •Контроль методом счета записи.

- •Контроль по меткам

- •Метод обратной связи

- •Метод проверки наличия формальных признаков (синтаксический метод, метод шаблонов).

- •Метод проверки запрещенных комбинаций.

- •Метод an-кодов

- •Методы на основе циклических кодов и кодов Хэмминга и др.

- •Структурные методы обеспечения контролепригодности дискретных устройств.

- •Введение контрольных точек.

- •Размножение контактов.

- •Использование блокирующей логики.

- •Применение параллельных зависимых проверок

- •Замена одним элементом состояний группы элементов памяти.

- •Методы улучшения тестируемой бис. Сокращение числа тестовых входов.

- •Двухуровневое сканирование.

- •Микропроцессорные встроенные средства самотестирования.

- •Контроль и диагностирование эвм Характеристики систем диагностирования

- •Системы контроля в современных эвм

- •Применение аналоговых сигнатурных анализаторов

- •Работа локализатора неисправностей pfl780 в режиме "Pin by Pin"

- •Работа в режиме Pin by Pin

- •Работа с торцевыми разъемами

- •Среда тестирования

- •Индивидуальное тестирование или режим Pin by Pin?

- •Тестирование специальных устройств

- •Устранение ложных отказов путем использования эталонных сигнатур компонентов от разных производителей

- •Тестирование цифровых компонентов методом asa

- •Вариации сигнатур.

- •Входные цепи защиты

- •Набор альтернативных сигнатур

- •Тестирование подключенных к общей шине компонентов путем их изоляции специальными блокирующими напряжениями.

- •Системы с шинной архитектурой

- •Устройства с тремя логическими состояниями

- •Разрешение работы и блокирование компонентов

- •Применение "блокирующих" напряжений

- •Отключение тактовых импульсов.

- •Отключение шинных буферов.

- •Опция Loop until Pass

- •Локализация дефектных компонентов в системах с шинной архитектурой без их удаления из испытываемой цепи

- •Поиск неисправностей методами asa и ict в системах с шинной архитектурой

- •Сравнение шинных сигнатур

- •Шинные сигнатуры

- •Изоляция устройств.

- •Локализация коротких замыканий шины и неисправностей нагрузки прибором toneohm 950 в режиме расширенного обнаружения неисправностей шины

- •Типы шинных неисправностей

- •Короткие замыкания с низким сопротивлением

- •Измерение протекающего через дорожку тока.

- •Измерение напряжения на дорожке печатной платы

- •Обнаружение кз и чрезмерных токов нагрузки в труднодоступных для тестирования местах

- •Короткие замыкания на платах

- •Обнаружение сложных неисправностей тестируемой платы путем сравнения импедансных характеристик в режиме asa

- •Импедансные сигнатуры

- •Локализация неисправностей методом Аналогового сигнатурного анализа

- •Методы сравнения

- •Основы jtag Boundary Scan архитектуры

- •АрхитектураBoundaryScan

- •Обязательные инструкции

- •Как происходитBoundaryScanтест

- •Простой тест на уровне платы

- •Граф состояний тар – контроллера

- •Мониторинг сети Управление сетью

- •Предупреждение проблем с помощью планирования

- •Утилиты мониторинга сети

- •Специальные средства диагностики сети

- •Источники информации по поддержке сети

- •Искусство диагностики локальных сетей

- •Организация процесса диагностики сети

- •Методика упреждающей диагностики сети

- •Диагностика локальных сетей и Интернет Диагностика локальных сетей

- •Ifconfig le0

- •Сетевая диагностика с применением протокола snmp

- •Диагностика на базеIcmp

- •Применение 6-го режима сетевого адаптера для целей диагностики

- •Причины циклов пакетов и осцилляции маршрутов

- •Конфигурирование сетевых систем

- •Методы тестирования оптических кабелей для локальных сетей.

- •Многомодовый в сравнении с одномодовым

- •Нахождение разрывов

- •Измерение потери мощности

- •Использование тестовOtdRдля одномодовых приложений

- •Источники

- •Словарь терминов а

Тестирование подключенных к общей шине компонентов путем их изоляции специальными блокирующими напряжениями.

В системах с шинной архитектурой все составляющие компоненты подключаются к шине параллельно. Такое построение затрудняет локализацию дефектных ИМС при тестировании. Выход из создавшегося положения заключается в применении метода изоляции испытываемых компонентов с помощью специальных "блокирующих" напряжений высокого и низкого логического уровней.

Системы с шинной архитектурой

В микропроцессорных системах с шинной архитектурой входящие в них компоненты пересылают данные и сигналы управления по общим шинам - линиям адресов, данных и управления. Шинные цепи проектируются таким образом, чтобы в любое время лишь одно, подключенное к шине устройство, могло помещать в нее свои данные. Таким образом, при поиске неисправностей в микросхемах RAM, ROM, портах и т.д. прибором PFL в режиме ICT (внутрисхемного тестирования) возникают трудности, связанные с параллельным подключением этих устройств к общим шинам. Если локализатор обнаруживает ситуацию неисправности, то трудно с точностью сказать какой из подключенных к шине параллельно компонентов вызывает ее. Очевидно, что должно существовать средство способное изолировать подсоединенное к общей шине устройство от других компонентов во время тестирования методом ICT.

Устройства с тремя логическими состояниями

К омпоненты,

входящие в системы с шинной архитектурой

и способные обмениваться с ее помощью

данными, помимо обычных высокого и

низкого логических уровней имеют, так

называемое, "третье" состояние.

При наличии этого логического уровня

выхода такого компонента принимают

высокоимпедансное состояние (открытое

состояние цепи). Компоненты, поддерживающие

три логических уровня, имеют один или

более входов, которые управляют его

выходами - т.е. от них зависит, будет ли

оно функционировать как обычное

устройство или находиться в

высокоимпедансном, по отношению к общей

шине, состоянии.

омпоненты,

входящие в системы с шинной архитектурой

и способные обмениваться с ее помощью

данными, помимо обычных высокого и

низкого логических уровней имеют, так

называемое, "третье" состояние.

При наличии этого логического уровня

выхода такого компонента принимают

высокоимпедансное состояние (открытое

состояние цепи). Компоненты, поддерживающие

три логических уровня, имеют один или

более входов, которые управляют его

выходами - т.е. от них зависит, будет ли

оно функционировать как обычное

устройство или находиться в

высокоимпедансном, по отношению к общей

шине, состоянии.

Разрешение работы и блокирование компонентов

Разрешающий работу вход компонента обычно подсоединяется (зачастую косвенно - через декодирующую логику) к одной из управляющих линий системного микропроцессора. Сигнал разрешения обычно имеет низкий логический уровень, а при его переходе в состояние логической единицы выхода этого устройства принимают высокоимпедансное состояние, т.е. отсоединяются от общей шины.

Применение "блокирующих" напряжений

Локализаторы неисправностей PFL имеют выходные клеммы, с которых на тестируемое устройство могут подаваться специальные "блокирующие" напряжения (guard яvoltage) высокого и низкого логических уровней. Точное размещение блокирующих напряжений на тестируемом устройстве разрешает работу испытываемого компонента и блокирует функционирование других. Рассмотрим это положение на примере представленной ниже цепи - предположим, что в наличии дефекта подозревается чип ОЗУ - U3.

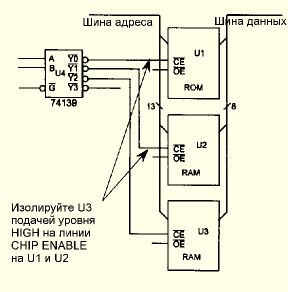

Изолируйте U3 подачей блокирующих напряжений на входа CHIP ENABLE ИМС - U1 и U2. Микросхемы U1, U2 и U3 являются параллельно подключенными к шинам адреса и данных чипами ОЗУ. В случае нормальной работы дешифратор U4 имеет лишь один выходной контакт, на котором присутствует уровень логического нуля, разрешая работу чипам U1, U2 и U3.

Для испытания ИМС с помощью локализатора неисправностей в режиме внутрисхемного тестирования к компоненту U3 подсоединяется тестовая клипса. Когда локализатор PFL испытывает устройство, на него в течение нескольких миллисекунд подается напряжение питания и испытательные сигналы. В связи с тем, что чипы U2 и U3 соединены с тестируемым компонентом параллельно, они также активизируются локализатором. Мы можем блокировать их работу, подавая на их входа СЕ блокирующее напряжение высокого логического уровня - в результате этого, эти чипы будут находиться в высокоимпедансном, по отношению к общей шине, состоянии. Локализатор неисправностей PFL имеет клеммы, с которых на тестируемое устройство могут подаваться блокирующие напряжения высокого и низкого логических уровней, причем, эти уровни не будут изменяться в течение всего теста.

Аналогичным образом могут быть отключены и другие подсоединенные к шине компоненты - вы можете блокировать любое, необходимое для изоляции тестируемого элемента, количество компонентов. Другими словами, для корректного тестирования, подсоединенного к общей шине компонента, необходимо блокировать работу всех элементов, подключенных к нему параллельно.