- •Вступление

- •Основные задачи технической диагностики

- •Системы диагноза технического состояния

- •Диагностические системы управления

- •Объекты диагноза

- •Математические модели объектов диагноза

- •Функциональные схемы систем тестового и функционального диагноза

- •Методы и технические средства диагностирования элементов и устройств вычислительной техники и систем управления Общие сведения

- •Тестовое тестирование узлов, блоков и устройств.

- •Структуры автоматизированных систем.

- •Программное обеспечение процессов диагностирования.

- •Логические анализаторы.

- •Микропроцессорные анализаторы (ма).

- •Способы запуска.

- •Подключающие устройства.

- •Ввод начальных данных.

- •Проверка отдельных триггеров.

- •Проверка содержимого постоянных запоминающих устройств (пзу).

- •Проверка оперативных запоминающих устройств (озу).

- •Проверка работы линии коллективного пользования (лкп).

- •Проверка аналого-цифровых преобразователей (ацп).

- •Проверка печатных плат.

- •Проверка микропроцессорной системы.

- •Сигнатурные анализаторы

- •Процесс формирования сигнатур.

- •Аппаратурная реализация сигнатурного анализатора.

- •Тестовое диагностирование устройств в составе эвм.

- •Диагностирование оборудования процессоров.

- •Способы диагностирования периферийных устройств.

- •Диагностирование упу/пу с помощью процессора.

- •Проверки упу/пу с помощью диагностических приказов.

- •Диагностирование упу/пу с помощью тестеров.

- •Способы тестирования зу.

- •Принципы построения стандартных проверяющих тестов полупроводниковых зу.

- •Аппаратурные средства функционального диагностирования узлов и блоков. Основные принципы построения.

- •Кодовые методы контроля.

- •Контроль передач информации.

- •Контроль по запрещенным комбинациям.

- •Самопроверяемые схемы контроля.

- •Контроль по модулю

- •Организация аппаратурного контроля озу.

- •Организация аппаратурного контроля внешних зу.

- •Средства функционального диагностирования в составе эвм.

- •Контроль методом двойного или многократного счета

- •Экстраполяционная проверка

- •Контроль по методу усеченного алгоритма (алгоритмический контроль).

- •Способ подстановки.

- •Проверка предельных значений или метод "вилок".

- •Проверка с помощью дополнительных связей.

- •Метод избыточных переменных

- •Контроль методом обратного счета.

- •Метод избыточных цифр.

- •Метод контрольного суммирования.

- •Контроль методом счета записи.

- •Контроль по меткам

- •Метод обратной связи

- •Метод проверки наличия формальных признаков (синтаксический метод, метод шаблонов).

- •Метод проверки запрещенных комбинаций.

- •Метод an-кодов

- •Методы на основе циклических кодов и кодов Хэмминга и др.

- •Структурные методы обеспечения контролепригодности дискретных устройств.

- •Введение контрольных точек.

- •Размножение контактов.

- •Использование блокирующей логики.

- •Применение параллельных зависимых проверок

- •Замена одним элементом состояний группы элементов памяти.

- •Методы улучшения тестируемой бис. Сокращение числа тестовых входов.

- •Двухуровневое сканирование.

- •Микропроцессорные встроенные средства самотестирования.

- •Контроль и диагностирование эвм Характеристики систем диагностирования

- •Системы контроля в современных эвм

- •Применение аналоговых сигнатурных анализаторов

- •Работа локализатора неисправностей pfl780 в режиме "Pin by Pin"

- •Работа в режиме Pin by Pin

- •Работа с торцевыми разъемами

- •Среда тестирования

- •Индивидуальное тестирование или режим Pin by Pin?

- •Тестирование специальных устройств

- •Устранение ложных отказов путем использования эталонных сигнатур компонентов от разных производителей

- •Тестирование цифровых компонентов методом asa

- •Вариации сигнатур.

- •Входные цепи защиты

- •Набор альтернативных сигнатур

- •Тестирование подключенных к общей шине компонентов путем их изоляции специальными блокирующими напряжениями.

- •Системы с шинной архитектурой

- •Устройства с тремя логическими состояниями

- •Разрешение работы и блокирование компонентов

- •Применение "блокирующих" напряжений

- •Отключение тактовых импульсов.

- •Отключение шинных буферов.

- •Опция Loop until Pass

- •Локализация дефектных компонентов в системах с шинной архитектурой без их удаления из испытываемой цепи

- •Поиск неисправностей методами asa и ict в системах с шинной архитектурой

- •Сравнение шинных сигнатур

- •Шинные сигнатуры

- •Изоляция устройств.

- •Локализация коротких замыканий шины и неисправностей нагрузки прибором toneohm 950 в режиме расширенного обнаружения неисправностей шины

- •Типы шинных неисправностей

- •Короткие замыкания с низким сопротивлением

- •Измерение протекающего через дорожку тока.

- •Измерение напряжения на дорожке печатной платы

- •Обнаружение кз и чрезмерных токов нагрузки в труднодоступных для тестирования местах

- •Короткие замыкания на платах

- •Обнаружение сложных неисправностей тестируемой платы путем сравнения импедансных характеристик в режиме asa

- •Импедансные сигнатуры

- •Локализация неисправностей методом Аналогового сигнатурного анализа

- •Методы сравнения

- •Основы jtag Boundary Scan архитектуры

- •АрхитектураBoundaryScan

- •Обязательные инструкции

- •Как происходитBoundaryScanтест

- •Простой тест на уровне платы

- •Граф состояний тар – контроллера

- •Мониторинг сети Управление сетью

- •Предупреждение проблем с помощью планирования

- •Утилиты мониторинга сети

- •Специальные средства диагностики сети

- •Источники информации по поддержке сети

- •Искусство диагностики локальных сетей

- •Организация процесса диагностики сети

- •Методика упреждающей диагностики сети

- •Диагностика локальных сетей и Интернет Диагностика локальных сетей

- •Ifconfig le0

- •Сетевая диагностика с применением протокола snmp

- •Диагностика на базеIcmp

- •Применение 6-го режима сетевого адаптера для целей диагностики

- •Причины циклов пакетов и осцилляции маршрутов

- •Конфигурирование сетевых систем

- •Методы тестирования оптических кабелей для локальных сетей.

- •Многомодовый в сравнении с одномодовым

- •Нахождение разрывов

- •Измерение потери мощности

- •Использование тестовOtdRдля одномодовых приложений

- •Источники

- •Словарь терминов а

Замена одним элементом состояний группы элементов памяти.

На рис. 25,а показана логическая сеть, в которую помещен триггер, реализованный на элементе И-НЕ. Его состояние заменяет состояние части логической сети и обеспечивает проведение теста для последующей части сети. Подобный же вариант реализации показан на рис. 25,б.В логическую сеть помещается логический элемент, который генерирует сигналы, заменяющие много входных сигналов.

Рассмотренные выше специализированные методы синтеза контролепригодных устройств были разработаны для интегральных схем средней степени интеграции (СИС) ,затем модифицированы . для БИС и СБИС и используются обычно на уровне плат и кристаллов.

Методы улучшения тестируемой бис. Сокращение числа тестовых входов.

Основной проблемой контроля БИС является сложность доступа к наиболее важным в процессе контроля точкам принципиальной схемы,характеризующим основные логические связи внутри ИС. В ИС малой и средней степени интеграции такие контрольные точки могут быть выведены на границы кристалла, а следовательно, и на выходные контакты; в БИС же это практически невозможно, так как один внешний вывод приходится как минимум на 10—20логических вентилей. В значительной степени усложняется процесс контроля БИС, содержащей последовательное соединение вентилей, так как при этомна внешние контакты микросхемы выводятся лишь входные и выходные сигналытакой цепи, что обусловливает значительное увеличение количества тактов контроля.

Сокращения числа тестовых входов можно добитьсяпри использовании одного или нескольких тестовых входов для образования нескольких контрольных точекиспользованием последовательно-параллельного способа обработки контрольной информации (рис. 26,а). Входной сигнал по контрольному входу Твх поступает на счетчик, а затем дешифратором преобразуется вnтестовых сигналов, которые поступают на контрольные точки проверяемой логики.

Д ля

решения проблемы сокращения числа

тестовых входов и выходов удобно

использовать различные типы мультиплексоров

и демультиплексоровсоответственно.Демультиплексор подключают к тестовому

входу БИС. Он улучшает управляемость

контрольными точками схемы, подключенными

к выходам демультиплексора, выполняет

как бы размножение тестового сигнала

на определенное количество контрольных

точек БИС.Для съема информации с

нескольких контрольных точек на один

тестовый выход используют мультиплексоры,

введение которых в схему БИС в этом

случае улучшает наблюдаемость

соответствующих точек контроля.

ля

решения проблемы сокращения числа

тестовых входов и выходов удобно

использовать различные типы мультиплексоров

и демультиплексоровсоответственно.Демультиплексор подключают к тестовому

входу БИС. Он улучшает управляемость

контрольными точками схемы, подключенными

к выходам демультиплексора, выполняет

как бы размножение тестового сигнала

на определенное количество контрольных

точек БИС.Для съема информации с

нескольких контрольных точек на один

тестовый выход используют мультиплексоры,

введение которых в схему БИС в этом

случае улучшает наблюдаемость

соответствующих точек контроля.

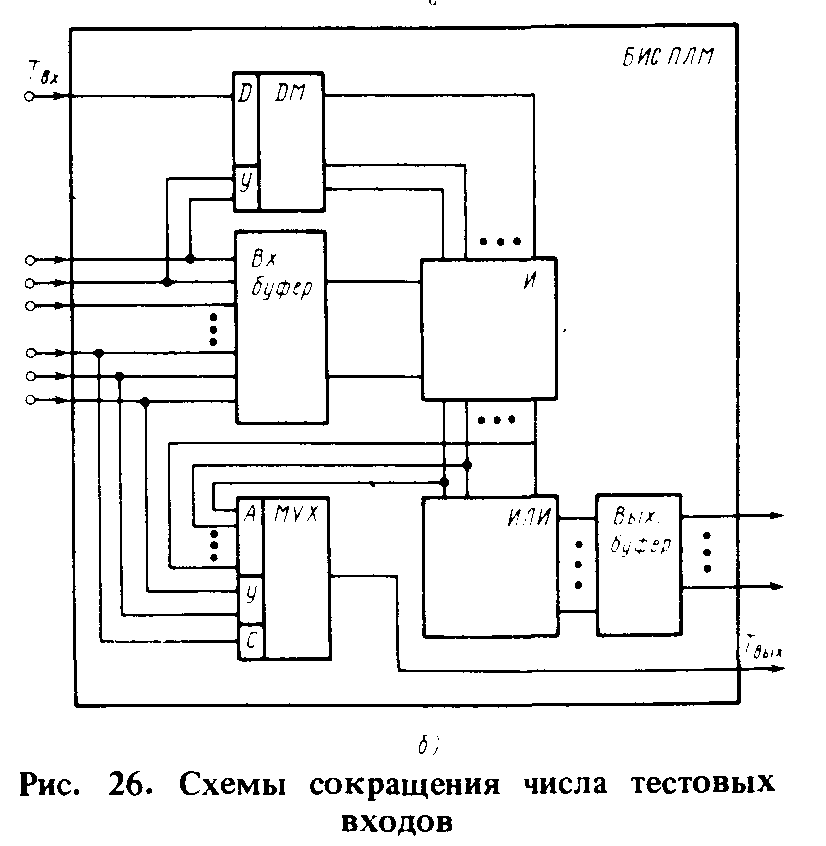

На рис. 26,б дан пример использования демультиплексора и мультиплексора для сокращения числа тестовых входов и выходов в БИС программируемой логической матрицы ПЛМ комбинационной логики с однобитными декодерами входных сигналов. Для улучшения наблюдаемости сигналов вертикальных шин ПЛМ введен мультиплексор. Для улучшения управляемости вертикальными шинами ПЛМ — демультиплексор, что способствует разбиению схемы БИС ПЛМ на три части (входной буфер, матрицаИ,матрицаИЛИс выходным буфером) и дает возможность тестироватьБИС ПЛМпо частям короткими тест-наборами.

При подаче сигнала Смультиплексор выбирает один из своих входов (вертикальную шинуПЛМ),адрес которого задается двоичным кодом на адресных входах мультиплексора, подключенных к входам ПЛМ, и передает сигнал с выбранной вертикальной шины на тестовый выход.. Таким образом просматриваются сигналы на всех вертикальных шинахПЛМ(улучшается их наблюдаемость).

Если на вход Dдемультиплексора подать значение логической единицы, то на выбранном в соответствии с адресом, заданным на управляющих входах, подключенных ко входамПЛМ,выходе демультиплексора будет значение логической единицы, на остальных —значение логического нуля. Так как выходы демультиплексора подключены к вертикальным шинамПЛМ,то осуществляется управление значениями сигналов на них. Для обеспечения рабочего режима в приведенной на рис. 26,бсхеме необходимо предусмотреть еще дополнительные средства, которые здесь не приводятся.

Для сокращения числа тестовых входов в схеме БИСможно выделить выход, соединенный не только с выходом элемента, но и со входом хотя бы одного элемента. Тогда возможны два режима работы: выходов (основное назначение) и входов (дополнительное значение) .Примерами таких схем являются счетчики, триггеры, регистры и др. Выходы БИС должны обеспечивать проводное ИЛИ.