- •Вступление

- •Основные задачи технической диагностики

- •Системы диагноза технического состояния

- •Диагностические системы управления

- •Объекты диагноза

- •Математические модели объектов диагноза

- •Функциональные схемы систем тестового и функционального диагноза

- •Методы и технические средства диагностирования элементов и устройств вычислительной техники и систем управления Общие сведения

- •Тестовое тестирование узлов, блоков и устройств.

- •Структуры автоматизированных систем.

- •Программное обеспечение процессов диагностирования.

- •Логические анализаторы.

- •Микропроцессорные анализаторы (ма).

- •Способы запуска.

- •Подключающие устройства.

- •Ввод начальных данных.

- •Проверка отдельных триггеров.

- •Проверка содержимого постоянных запоминающих устройств (пзу).

- •Проверка оперативных запоминающих устройств (озу).

- •Проверка работы линии коллективного пользования (лкп).

- •Проверка аналого-цифровых преобразователей (ацп).

- •Проверка печатных плат.

- •Проверка микропроцессорной системы.

- •Сигнатурные анализаторы

- •Процесс формирования сигнатур.

- •Аппаратурная реализация сигнатурного анализатора.

- •Тестовое диагностирование устройств в составе эвм.

- •Диагностирование оборудования процессоров.

- •Способы диагностирования периферийных устройств.

- •Диагностирование упу/пу с помощью процессора.

- •Проверки упу/пу с помощью диагностических приказов.

- •Диагностирование упу/пу с помощью тестеров.

- •Способы тестирования зу.

- •Принципы построения стандартных проверяющих тестов полупроводниковых зу.

- •Аппаратурные средства функционального диагностирования узлов и блоков. Основные принципы построения.

- •Кодовые методы контроля.

- •Контроль передач информации.

- •Контроль по запрещенным комбинациям.

- •Самопроверяемые схемы контроля.

- •Контроль по модулю

- •Организация аппаратурного контроля озу.

- •Организация аппаратурного контроля внешних зу.

- •Средства функционального диагностирования в составе эвм.

- •Контроль методом двойного или многократного счета

- •Экстраполяционная проверка

- •Контроль по методу усеченного алгоритма (алгоритмический контроль).

- •Способ подстановки.

- •Проверка предельных значений или метод "вилок".

- •Проверка с помощью дополнительных связей.

- •Метод избыточных переменных

- •Контроль методом обратного счета.

- •Метод избыточных цифр.

- •Метод контрольного суммирования.

- •Контроль методом счета записи.

- •Контроль по меткам

- •Метод обратной связи

- •Метод проверки наличия формальных признаков (синтаксический метод, метод шаблонов).

- •Метод проверки запрещенных комбинаций.

- •Метод an-кодов

- •Методы на основе циклических кодов и кодов Хэмминга и др.

- •Структурные методы обеспечения контролепригодности дискретных устройств.

- •Введение контрольных точек.

- •Размножение контактов.

- •Использование блокирующей логики.

- •Применение параллельных зависимых проверок

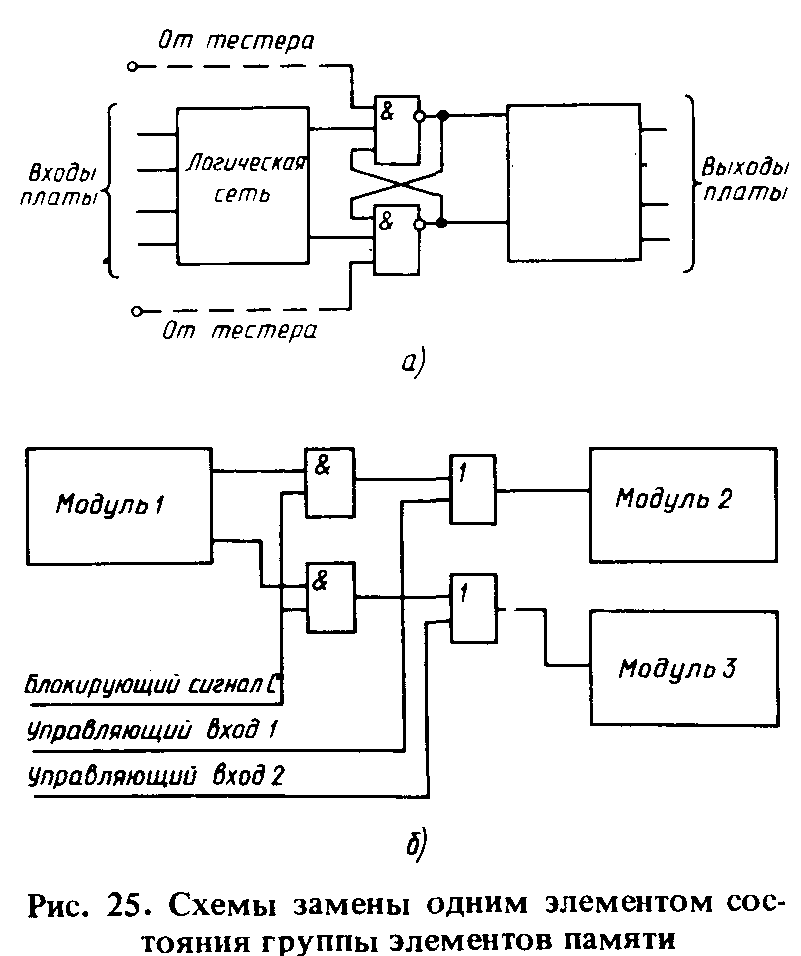

- •Замена одним элементом состояний группы элементов памяти.

- •Методы улучшения тестируемой бис. Сокращение числа тестовых входов.

- •Двухуровневое сканирование.

- •Микропроцессорные встроенные средства самотестирования.

- •Контроль и диагностирование эвм Характеристики систем диагностирования

- •Системы контроля в современных эвм

- •Применение аналоговых сигнатурных анализаторов

- •Работа локализатора неисправностей pfl780 в режиме "Pin by Pin"

- •Работа в режиме Pin by Pin

- •Работа с торцевыми разъемами

- •Среда тестирования

- •Индивидуальное тестирование или режим Pin by Pin?

- •Тестирование специальных устройств

- •Устранение ложных отказов путем использования эталонных сигнатур компонентов от разных производителей

- •Тестирование цифровых компонентов методом asa

- •Вариации сигнатур.

- •Входные цепи защиты

- •Набор альтернативных сигнатур

- •Тестирование подключенных к общей шине компонентов путем их изоляции специальными блокирующими напряжениями.

- •Системы с шинной архитектурой

- •Устройства с тремя логическими состояниями

- •Разрешение работы и блокирование компонентов

- •Применение "блокирующих" напряжений

- •Отключение тактовых импульсов.

- •Отключение шинных буферов.

- •Опция Loop until Pass

- •Локализация дефектных компонентов в системах с шинной архитектурой без их удаления из испытываемой цепи

- •Поиск неисправностей методами asa и ict в системах с шинной архитектурой

- •Сравнение шинных сигнатур

- •Шинные сигнатуры

- •Изоляция устройств.

- •Локализация коротких замыканий шины и неисправностей нагрузки прибором toneohm 950 в режиме расширенного обнаружения неисправностей шины

- •Типы шинных неисправностей

- •Короткие замыкания с низким сопротивлением

- •Измерение протекающего через дорожку тока.

- •Измерение напряжения на дорожке печатной платы

- •Обнаружение кз и чрезмерных токов нагрузки в труднодоступных для тестирования местах

- •Короткие замыкания на платах

- •Обнаружение сложных неисправностей тестируемой платы путем сравнения импедансных характеристик в режиме asa

- •Импедансные сигнатуры

- •Локализация неисправностей методом Аналогового сигнатурного анализа

- •Методы сравнения

- •Основы jtag Boundary Scan архитектуры

- •АрхитектураBoundaryScan

- •Обязательные инструкции

- •Как происходитBoundaryScanтест

- •Простой тест на уровне платы

- •Граф состояний тар – контроллера

- •Мониторинг сети Управление сетью

- •Предупреждение проблем с помощью планирования

- •Утилиты мониторинга сети

- •Специальные средства диагностики сети

- •Источники информации по поддержке сети

- •Искусство диагностики локальных сетей

- •Организация процесса диагностики сети

- •Методика упреждающей диагностики сети

- •Диагностика локальных сетей и Интернет Диагностика локальных сетей

- •Ifconfig le0

- •Сетевая диагностика с применением протокола snmp

- •Диагностика на базеIcmp

- •Применение 6-го режима сетевого адаптера для целей диагностики

- •Причины циклов пакетов и осцилляции маршрутов

- •Конфигурирование сетевых систем

- •Методы тестирования оптических кабелей для локальных сетей.

- •Многомодовый в сравнении с одномодовым

- •Нахождение разрывов

- •Измерение потери мощности

- •Использование тестовOtdRдля одномодовых приложений

- •Источники

- •Словарь терминов а

Размножение контактов.

Для более полного использования имеющихся штырьковИС целесообразно применятьдемультиплексор на входе, мультиплексор — на выходе.В режиме контроля тестовый вход подсоединяется не к обычным элементам схемы, а к испытываемым узлам с помощью демультиплексора. Мультиплексор обеспечивает наблюдаемость внутреннего состояния схемы на ее выходных штырьках.

Кроме того, выходы испытываемых узлов могут просто подключаться к древовидной схеме контроля по четности, выход которой делается наблюдаемым на выходном контакте.Недостатокданного метода связан с возможностью появлениязадержек сигналов.

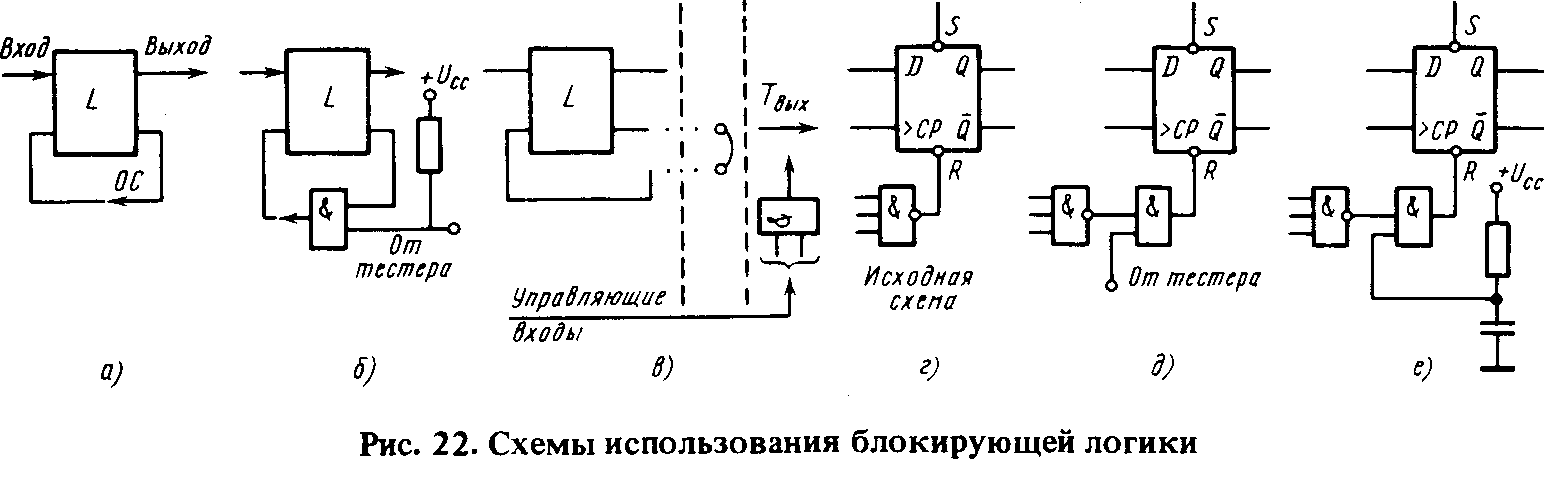

Использование блокирующей логики.

Блокирующие

вентили используют для разрыва обратных

связей (ОС), особенно

при гонках, для разделения расходящихся

путей и для блокировки триггеров.Обратные связи, как известно, затрудняют

постр оение

тестов.Их разрыв превращает схему

в достаточно простую с точки зрения

построения для нее тестовых наборов.

Разрыв обратных связей, например, для

схемы, изображенной на рис.

22,а, выполняется физически путем

вывода ее на контакты разъема и исключения

перемычек (рис. 22,в) или

логически с использованием вентиля

(рис. 22,б).

оение

тестов.Их разрыв превращает схему

в достаточно простую с точки зрения

построения для нее тестовых наборов.

Разрыв обратных связей, например, для

схемы, изображенной на рис.

22,а, выполняется физически путем

вывода ее на контакты разъема и исключения

перемычек (рис. 22,в) или

логически с использованием вентиля

(рис. 22,б).

Проблемой при тестировании последовательных схем является установка их в определенное состояние.Реализация осуществляется путем установки в нуль от тестера схемы типа триггера. На рис 22,гпоказана исходная схема. Установка в нуль триггера осуществляется через вентиль И (рис. 22,д),для установки в нуль используетсяRС-цепь (рис.22,е).

Э тот

метод требует дополнительных входов,

выходов и модулей, поэтому применение

его оправдано в том случае,

если другие методы проверки

неэффективны.

тот

метод требует дополнительных входов,

выходов и модулей, поэтому применение

его оправдано в том случае,

если другие методы проверки

неэффективны.

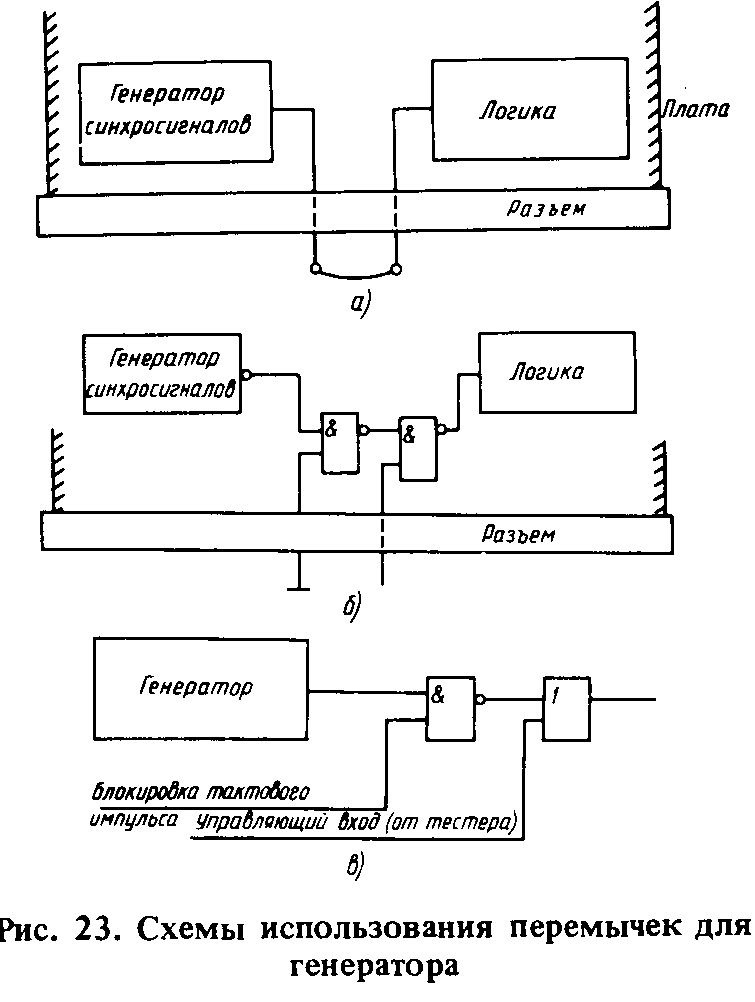

На практике обычно трудно проверить схему с генератором колебаний из-за невозможности синхронизации с тестером. Блокирующая логика, синхронизируемая от тестера, позволяет выполнить синхронное тестирование всей логической схемы на плате (рис. 23,а).

Наличие магистральной структуры в некоторых микропроцессорах (МП) позволяет без дополнительных затрат разделять и комбинировать части схемы с целью упрощения контроля.

Применение

перемычек дает возможность тестовому

генератору непосредственно управлять

испытываемым устройством и наблюдать

за ним. Применение соединительных

перемычек оправдано в особо ответственных

случаях, например, частовозникает

необходимость согласовать частоту

генератора с частотой работы тестируемого

устройства или просто обеспечить внешнюю

(от тестера) синхронизацию. На рис.

23,a соединение

генератора и логики, на которую он

работает, осуществляется с помощью двух

контактов разъема, на рис.

23,б,в — спомощью одного контакта разъема в

совокупности с блокирующими вентилями.Перемычки позволяют отключать или

включать генератор в опредёленные

моменты времени и фиксировать приход

определенного сигнала.Этот способ

дает в озможность

свободно изменять частоту синхронизации,

что облегчает проведение процедур

локализации.

озможность

свободно изменять частоту синхронизации,

что облегчает проведение процедур

локализации.

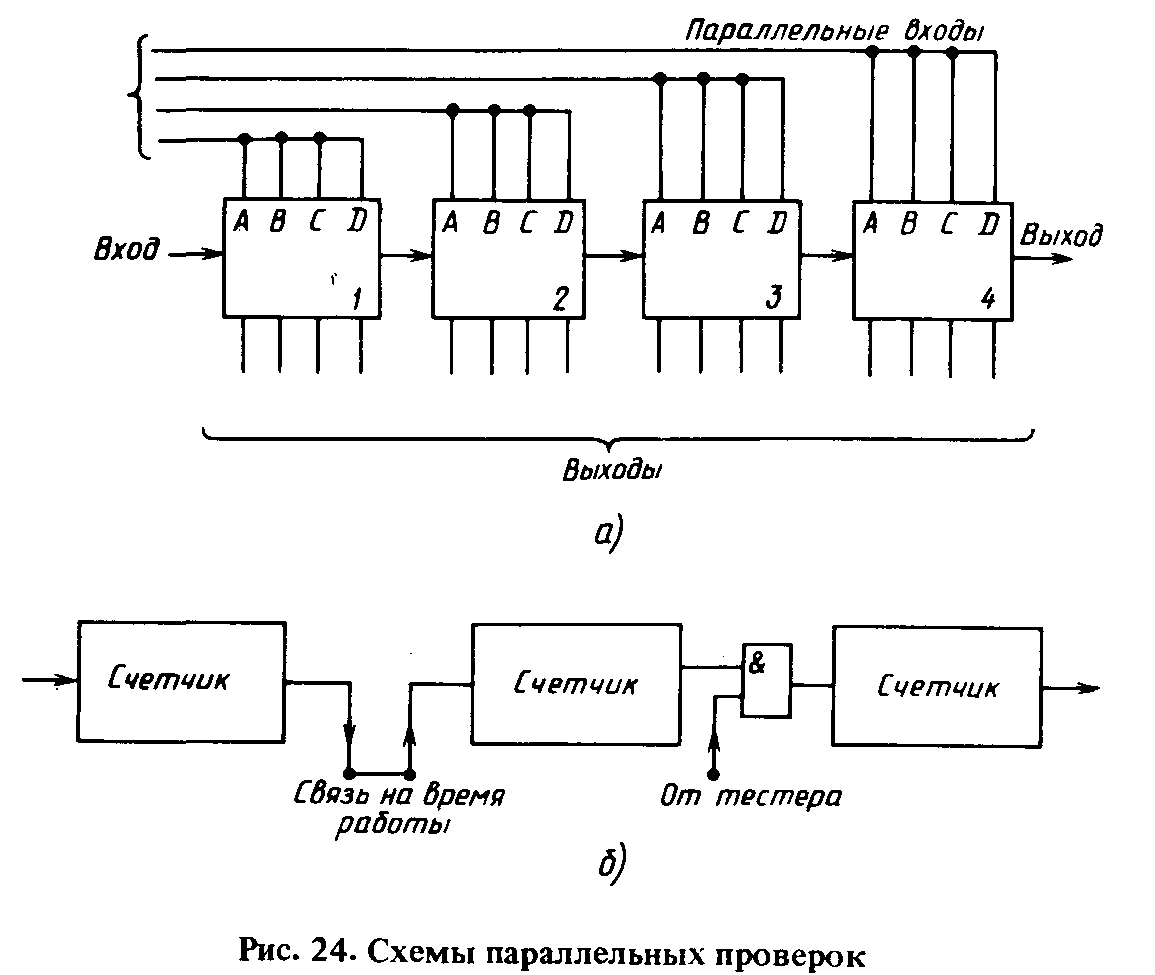

Применение параллельных зависимых проверок

З аключается

в том, что предварительнов структуре

последовательной схемы находятся

цепочки последовательно связанных

элементов памяти.Цепочки разъединяются

с помощью блокирующих вентилей, а для

равенства задержек сигналов к отдельным

цепочкам затем добавляются избыточные

элементы памяти.Для преобразованной

таким образом структурной схемы применяютспособы проверки, разработанные для

счетчиков:

аключается

в том, что предварительнов структуре

последовательной схемы находятся

цепочки последовательно связанных

элементов памяти.Цепочки разъединяются

с помощью блокирующих вентилей, а для

равенства задержек сигналов к отдельным

цепочкам затем добавляются избыточные

элементы памяти.Для преобразованной

таким образом структурной схемы применяютспособы проверки, разработанные для

счетчиков:

введение параллельного входа в счетчик, например, при котором 16-битовый счетчик устанавливается в определенное состояние с помощью 4входов вместо16,что обеспечивает установку определенных комбинаций (рис. 24,а);

применение связей между группами элементов счетчика(рис. 24,б).

Рассматриваемые способы зависят от уровня локализации неисправностей. При этом следует обеспечить параллельную подачу входных сигналов на все цепочки и их параллельный анализ. Такой способ эффективен для одновременной проверки нескольких микропроцессоров, так как позволяет сократить время проверки и обеспечить ее полноту.