- •Вступление

- •Основные задачи технической диагностики

- •Системы диагноза технического состояния

- •Диагностические системы управления

- •Объекты диагноза

- •Математические модели объектов диагноза

- •Функциональные схемы систем тестового и функционального диагноза

- •Методы и технические средства диагностирования элементов и устройств вычислительной техники и систем управления Общие сведения

- •Тестовое тестирование узлов, блоков и устройств.

- •Структуры автоматизированных систем.

- •Программное обеспечение процессов диагностирования.

- •Логические анализаторы.

- •Микропроцессорные анализаторы (ма).

- •Способы запуска.

- •Подключающие устройства.

- •Ввод начальных данных.

- •Проверка отдельных триггеров.

- •Проверка содержимого постоянных запоминающих устройств (пзу).

- •Проверка оперативных запоминающих устройств (озу).

- •Проверка работы линии коллективного пользования (лкп).

- •Проверка аналого-цифровых преобразователей (ацп).

- •Проверка печатных плат.

- •Проверка микропроцессорной системы.

- •Сигнатурные анализаторы

- •Процесс формирования сигнатур.

- •Аппаратурная реализация сигнатурного анализатора.

- •Тестовое диагностирование устройств в составе эвм.

- •Диагностирование оборудования процессоров.

- •Способы диагностирования периферийных устройств.

- •Диагностирование упу/пу с помощью процессора.

- •Проверки упу/пу с помощью диагностических приказов.

- •Диагностирование упу/пу с помощью тестеров.

- •Способы тестирования зу.

- •Принципы построения стандартных проверяющих тестов полупроводниковых зу.

- •Аппаратурные средства функционального диагностирования узлов и блоков. Основные принципы построения.

- •Кодовые методы контроля.

- •Контроль передач информации.

- •Контроль по запрещенным комбинациям.

- •Самопроверяемые схемы контроля.

- •Контроль по модулю

- •Организация аппаратурного контроля озу.

- •Организация аппаратурного контроля внешних зу.

- •Средства функционального диагностирования в составе эвм.

- •Контроль методом двойного или многократного счета

- •Экстраполяционная проверка

- •Контроль по методу усеченного алгоритма (алгоритмический контроль).

- •Способ подстановки.

- •Проверка предельных значений или метод "вилок".

- •Проверка с помощью дополнительных связей.

- •Метод избыточных переменных

- •Контроль методом обратного счета.

- •Метод избыточных цифр.

- •Метод контрольного суммирования.

- •Контроль методом счета записи.

- •Контроль по меткам

- •Метод обратной связи

- •Метод проверки наличия формальных признаков (синтаксический метод, метод шаблонов).

- •Метод проверки запрещенных комбинаций.

- •Метод an-кодов

- •Методы на основе циклических кодов и кодов Хэмминга и др.

- •Структурные методы обеспечения контролепригодности дискретных устройств.

- •Введение контрольных точек.

- •Размножение контактов.

- •Использование блокирующей логики.

- •Применение параллельных зависимых проверок

- •Замена одним элементом состояний группы элементов памяти.

- •Методы улучшения тестируемой бис. Сокращение числа тестовых входов.

- •Двухуровневое сканирование.

- •Микропроцессорные встроенные средства самотестирования.

- •Контроль и диагностирование эвм Характеристики систем диагностирования

- •Системы контроля в современных эвм

- •Применение аналоговых сигнатурных анализаторов

- •Работа локализатора неисправностей pfl780 в режиме "Pin by Pin"

- •Работа в режиме Pin by Pin

- •Работа с торцевыми разъемами

- •Среда тестирования

- •Индивидуальное тестирование или режим Pin by Pin?

- •Тестирование специальных устройств

- •Устранение ложных отказов путем использования эталонных сигнатур компонентов от разных производителей

- •Тестирование цифровых компонентов методом asa

- •Вариации сигнатур.

- •Входные цепи защиты

- •Набор альтернативных сигнатур

- •Тестирование подключенных к общей шине компонентов путем их изоляции специальными блокирующими напряжениями.

- •Системы с шинной архитектурой

- •Устройства с тремя логическими состояниями

- •Разрешение работы и блокирование компонентов

- •Применение "блокирующих" напряжений

- •Отключение тактовых импульсов.

- •Отключение шинных буферов.

- •Опция Loop until Pass

- •Локализация дефектных компонентов в системах с шинной архитектурой без их удаления из испытываемой цепи

- •Поиск неисправностей методами asa и ict в системах с шинной архитектурой

- •Сравнение шинных сигнатур

- •Шинные сигнатуры

- •Изоляция устройств.

- •Локализация коротких замыканий шины и неисправностей нагрузки прибором toneohm 950 в режиме расширенного обнаружения неисправностей шины

- •Типы шинных неисправностей

- •Короткие замыкания с низким сопротивлением

- •Измерение протекающего через дорожку тока.

- •Измерение напряжения на дорожке печатной платы

- •Обнаружение кз и чрезмерных токов нагрузки в труднодоступных для тестирования местах

- •Короткие замыкания на платах

- •Обнаружение сложных неисправностей тестируемой платы путем сравнения импедансных характеристик в режиме asa

- •Импедансные сигнатуры

- •Локализация неисправностей методом Аналогового сигнатурного анализа

- •Методы сравнения

- •Основы jtag Boundary Scan архитектуры

- •АрхитектураBoundaryScan

- •Обязательные инструкции

- •Как происходитBoundaryScanтест

- •Простой тест на уровне платы

- •Граф состояний тар – контроллера

- •Мониторинг сети Управление сетью

- •Предупреждение проблем с помощью планирования

- •Утилиты мониторинга сети

- •Специальные средства диагностики сети

- •Источники информации по поддержке сети

- •Искусство диагностики локальных сетей

- •Организация процесса диагностики сети

- •Методика упреждающей диагностики сети

- •Диагностика локальных сетей и Интернет Диагностика локальных сетей

- •Ifconfig le0

- •Сетевая диагностика с применением протокола snmp

- •Диагностика на базеIcmp

- •Применение 6-го режима сетевого адаптера для целей диагностики

- •Причины циклов пакетов и осцилляции маршрутов

- •Конфигурирование сетевых систем

- •Методы тестирования оптических кабелей для локальных сетей.

- •Многомодовый в сравнении с одномодовым

- •Нахождение разрывов

- •Измерение потери мощности

- •Использование тестовOtdRдля одномодовых приложений

- •Источники

- •Словарь терминов а

Принципы построения стандартных проверяющих тестов полупроводниковых зу.

При проверке дешифратора адреса учитывают реальные неисправности, которые приводят к отсутствию выборки определенного элемента памяти, многоадресную выборку, одновременную выборку элемента памяти одним адресом (неоднозначность выборки). В частности, проверка выборки осуществляется с помощью теста "Бег 1(0)".При прохождении этого теста за один прогон выбирается "1" из одного элемента памяти, и "О" из других элементов, т.е. подтверждается, что по правильному адресу осуществляется выборка только одного элемента памяти (с правильно записанной информацией).Длительность теста пропорциональна N2 циклам (N — число ячеек памяти).Для одновременного контроля дешифраторов столбцов и строк можно использовать считывание "1", записанной в диагональ матрицы.

При испытании матрицы элементов памяти проверяют следующие возможные неисправности: отсутствие записи "О" или "1", искажение информации в элементе памяти при записи в соседние ячейки, ложное считывание.Проверка записи элементов памяти выявляется с помощью простого теста последовательной записи и считывания "О" и "1".Отказы соседних элементов, содержащих неодинаковую информацию, выявляет тест типа "Шахматный". Для выявления отказов ложной записи и считывания часто используют тест "Бег 1(0)", а также считывание из каждого элемента столбца "О" (1) на фоне всех "1" или всех "О" в других элеиентах столбца.

Среди динамических параметров ЗУ важнейшим является время выборки адреса, проверка которого обеспечиваетсяобращениями по прямому и дополнительному адресам.

Экспериментальные исследования и анализ работоспособности некоторых микросхем БИС ОЗУ позволили сделать предположение о том, что проявлению неисправностей способствует в первую очередь характер последовательности обращений к ЗУ, т.е. тип операции (запись или считывание), информация и адрес выбранного запоминающего элемента. С учетом этого были разработаны алгоритмы проверяющих тестов, которые предусматривают проведение всевозможных адресных переходов в матрице между каждыми двумя ячейками с различными изменениями информации и типа операций и которые получили название тестов "попарного обращения".

Такая организация тестов позволяет осуществлять проверку tвыб в виде "попарного считывания с модификацией", а значение параметровtBOCиtзп- в виде "попарной записи - считывания". Кроме того, считают, что тесты "попарного обращения" эффективно проверяют НВЛ в матрице ячеек памяти. Для ЗУ с высокой информационной емкостью из-за значительной длительности тестов приходится сокращать поля текущих адресов по строкам или столбцам, сохраняя характер обращения.

О тсутствие

корректного математического описания

характерных неисправностей полупроводниковых

БИС ОЗУ и количественных оценок

обнаруживающей способности проверяющих

тестов приводит к тому, что на практике

осуществляют диагностирование при

помощи некоторого множества тестовых

последовательностей. При этом время

тестового диагностирования БИС ОЗУ,

даже при обеспечении минимально

допустимого для потребителя уровня

достоверности результатов диагностирования,

становится экономически неприемлемым.

тсутствие

корректного математического описания

характерных неисправностей полупроводниковых

БИС ОЗУ и количественных оценок

обнаруживающей способности проверяющих

тестов приводит к тому, что на практике

осуществляют диагностирование при

помощи некоторого множества тестовых

последовательностей. При этом время

тестового диагностирования БИС ОЗУ,

даже при обеспечении минимально

допустимого для потребителя уровня

достоверности результатов диагностирования,

становится экономически неприемлемым.

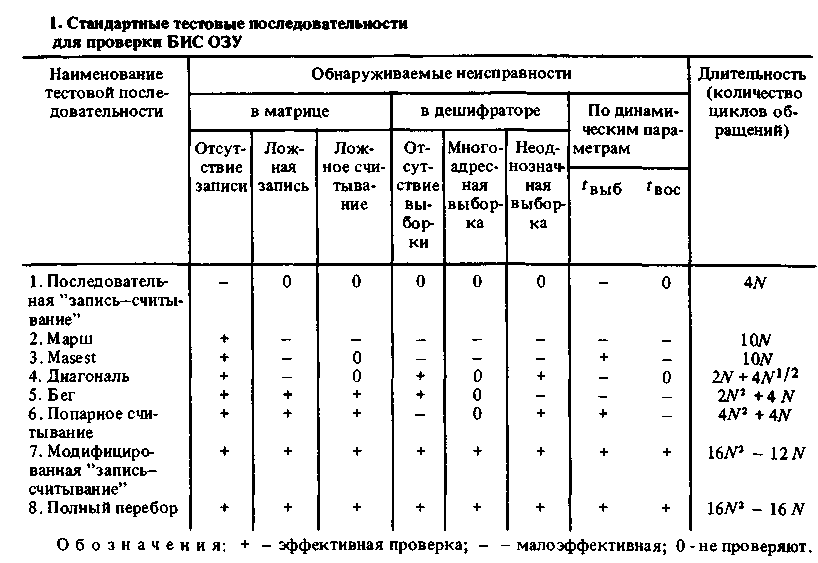

В табл. 1 приведены сравнительные качественные оценки полноты основных алгоритмов структурного синтеза проверяющих тестов.

Широкое применение в промышленности нашли тестеры со сменными платами и структурой, описанной ниже. Это, прежде всего, установки функционального контроля "Элекон-ФЗУ" и установка контроля памяти "УКП-1" (СССР), тестер "МД104" фирмы Macrodate(США), установка модели "1610" фирмыMinato(Япония) , тестерMTS-01 (ЧССР) , установкаICOMAT(ВНР).

Преимущества указанных автоматизированных тестеров для диагностирования БИС ОЗУ следующие: низкая стоимость в сочетании с достаточной универсальностью, которая обеспечивается специальным процессором; малые габариты и потребляемая мощность, что позволяет использовать их в виде автономных настольных приборов; высокое быстродействие, достигающее 10—12 мГц.