2629

.pdf

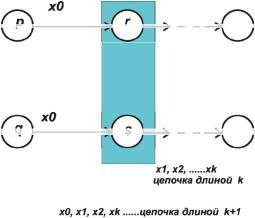

Рис. 1.12. Пояснение теоремы о (k + 1) эквивалентности

Пример минимизации автомата [7, 10]

Дана таблица переходов-выходов в форме обобщённой таблицы (табл. 1.1).

Таблица 1 . 1

Переходы-выходы минимизируемого автомата

с 9 состояниями, с 2 входными символами (сигналами) а,b

|

|

Функции переходов и выходов |

|

|

|||

№ y(t) π 0 |

|

y(t + 1) |

ψ |

|

|

||

|

|

|

z(t) |

|

|

||

|

|

|

|

|

|

||

|

а |

|

b |

а |

|

b |

π 1 |

1 |

3 |

|

6 |

1 |

|

0 |

А1 |

2 |

4 |

|

8 |

0 |

|

1 |

В1 |

3 |

1 |

|

4 |

1 |

|

0 |

А1 |

4 |

7 |

|

9 |

0 |

|

1 |

В1 |

5 |

9 |

|

1 |

1 |

|

0 |

А1 |

6 |

3 |

|

5 |

1 |

|

0 |

А1 |

7 |

4 |

|

3 |

0 |

|

1 |

В1 |

8 |

4 |

|

2 |

1 |

|

0 |

А1 |

9 |

5 |

|

7 |

1 |

|

0 |

А1 |

21

Начальное разбиение – это один блок, включающий все состояния, поскольку входные цепочки длиной 0 (пустая цепочка ε) не различают состояний. Независимо от того, в каком состоянии находился автомат, при подаче пустой цепочки ε выходом тоже будет пустая цепочка ε.

π0 = {А0 = <1,2,3,4,5,6,7,8,9>}.

Строим π 1 – те состояния, которые не различаются цепочкой длиной 1, т.е. символом либо а, либо b.

Видим, что состояния разбиваются на два блока – в первом реакции 1,0, во втором – 0,1:

π 1 = {А1 = <1,3,5,6,8,9>; В2 = <2,4,7>}.

Добавим к таблице переходов-выходов столбец для π 1. Теперь смотрим, в какие блоки переходит автомат из бло-

ков π1 под воздействием символов а либо b.

Строимтаблицу переходовизблоковразбиенияπ1 (табл. 1.2).

|

|

|

|

|

|

|

|

|

Таблица 1 . 2 |

|

|

Таблица переходов из разбиения π1 |

|

||||||||

|

|

|

|

|

|

|

|

|

||

|

Функции переходов и выходов |

|

π1 |

|

||||||

№ y(t) |

y(t + 1) |

|

|

ψ |

y(t + 1) |

|

||||

|

|

|

|

z(t) |

|

|

|

|

||

|

а |

|

|

|

|

|

|

|

||

|

|

b |

а |

|

b |

а |

|

b |

π 2 |

|

1 |

3 |

|

6 |

1 |

|

0 |

А1 |

|

А1 |

А2 |

2 |

4 |

|

8 |

0 |

|

1 |

В1 |

|

А1 |

В2 |

3 |

1 |

|

4 |

1 |

|

0 |

А1 |

|

В1 |

С2 |

4 |

7 |

|

9 |

0 |

|

1 |

В1 |

|

А1 |

В2 |

5 |

9 |

|

1 |

1 |

|

0 |

|

|

|

|

|

|

А1 |

|

А1 |

А2 |

|||||

6 |

3 |

|

5 |

1 |

|

0 |

А1 |

|

А1 |

А2 |

7 |

4 |

|

3 |

0 |

|

1 |

В1 |

|

А1 |

В2 |

8 |

4 |

|

2 |

1 |

|

0 |

В1 |

|

В1 |

D2 |

9 |

5 |

|

7 |

1 |

|

0 |

А1 |

|

В1 |

С2 |

Итак, в первой строчке под воздействием «а» осуществляется переход в состояние 3 – это блок А1, под воздействием «b»

22

осуществляется переход в состояние 6, это тоже блок А1. Так и записываем.

Во второй строчке под воздействием «а» осуществляется переход в состояние 4 – это блок В1, под воздействием «b» осуществляется переход в состояние 6, это блок А1.

Втретьей строчке под воздействием «а» осуществляется переход в состояние 1 – это блок А1, под воздействием «b» осуществляется переход в состояние 4, это блок В1.

Вчетвёртой строчке под воздействием «а» осуществляется переход в состояние 7 – это блок В1, под воздействием «b» осуществляется переход в состояние 9, это блок А1.

Действуя аналогично, получаем всю таблицу (см. табл. 1.2). Выделяем в табл. 1.2 эквивалентные состояния.

Получаем разбиение:

π2= {А2 = <1,5,6>;В2 = <2,4,7>; С2 = <3,9>; D2 = <8>}.

Строим π3. При его построении уже не нужно анализировать, в какой блок π2 переходит автомат из состояния 8, поскольку оно единственное в π2 и дальше дробиться не будет. Получаем табл. 1.3.

|

|

|

|

|

|

|

Таблица 1 . 3 |

|||

|

|

Таблица переходов из разбиения π2 |

|

|

||||||

|

|

|

|

|

|

|

|

|

||

|

Функции переходов и выходов |

π2 |

|

|

||||||

№ y(t) |

y(t + 1) |

|

ψ |

y(t + 1) |

|

|

||||

|

|

|

|

z(t) |

|

|

|

|

||

|

а |

|

|

|

|

|

|

|

||

|

|

b |

а |

|

b |

а |

|

b |

π3 |

|

1 |

3 |

|

6 |

1 |

|

0 |

С2 |

|

А2 |

А3 |

2 |

4 |

|

8 |

0 |

|

1 |

В2 |

|

D2 |

В3 |

3 |

1 |

|

4 |

1 |

|

0 |

А2 |

|

В2 |

D3 |

4 |

7 |

|

9 |

0 |

|

1 |

В2 |

|

С2 |

С2 |

5 |

9 |

|

1 |

1 |

|

0 |

С2 |

|

А2 |

А3 |

6 |

3 |

|

5 |

1 |

|

0 |

С2 |

|

А2 |

А3 |

7 |

4 |

|

3 |

0 |

|

1 |

В2 |

|

С2 |

С2 |

8 |

4 |

|

2 |

1 |

|

0 |

В2 |

|

В2 |

Е3 |

9 |

5 |

|

7 |

1 |

|

0 |

А2 |

|

В2 |

D3 |

23

Получаем разбиение:

π3 = {А3 = <1,5,6>; В3 = <2>; С3 = <4,7>; D3 = <3,9>; Е3 = <8>}.

Строим π4 (табл. 1.4).

Таблица 1 . 4 Таблица переходов из разбиения π4

№ y(t) |

Функции переходов и выходов |

|

π4 |

|

||||||

|

|

y(t+1) |

|

ψ |

y(t+1) |

|

||||

|

а |

|

|

|

z(t) |

|

|

|

|

|

|

|

b |

а |

|

b |

а |

|

b |

|

|

1 |

3 |

|

6 |

1 |

|

0 |

D3 |

|

А3 |

А4 |

2 |

4 |

|

8 |

0 |

|

1 |

С3 |

|

Е3 |

В4 |

3 |

1 |

|

4 |

1 |

|

0 |

А3 |

|

С3 |

С4 |

4 |

7 |

|

9 |

0 |

|

1 |

С3 |

|

D3 |

D4 |

5 |

9 |

|

1 |

1 |

|

0 |

D3 |

|

А3 |

А4 |

6 |

3 |

|

5 |

1 |

|

0 |

D3 |

|

А3 |

А4 |

7 |

4 |

|

3 |

0 |

|

1 |

С3 |

|

D3 |

D4 |

8 |

4 |

|

2 |

1 |

|

0 |

С3 |

|

В3 |

Е4 |

9 |

5 |

|

7 |

1 |

|

0 |

А3 |

|

С3 |

С4 |

Получаем разбиение:

π4 = {А4 = <1,5,6>; В4 = <2>; С4 = <4,7>; D 4 = <3,9>; Е4 = <8>}.

Поскольку π4 = π3, искомое разбиение найдено. Минимальный автомат имеет 5 состояний, а его функции

переходов и выходов определяются так (берём за основу разбиение π3):

(А3,а) = D3, ψ (А3,а) = 1 и т.д.

1.3. Модель логического элемента ПЛИС FPGA

Широко используемые в настоящее время программируемые логические интегральные схемы (ПЛИС) позволяют строить автоматы, реально используемые в системах управления, в распределенных компьютерных информационно-управляющих системах.

24

Программируемые логические интегральные схемы (ПЛИС, PLD) типа FPGA (field-programmable gate array) содержат конфи-

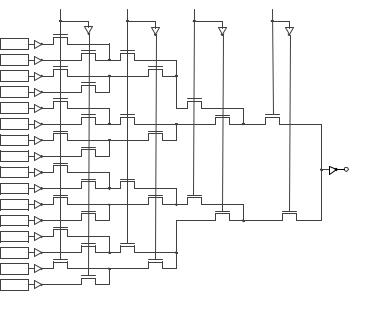

гурируемые логические блоки (КЛБ), состоящие из логических элементов ЛЭ. Логический элемент LUT ПЛИС типа FPGA – это постоянное запоминающее устройство ПЗУ (в источниках именуется LUT – Look Up Table), представляет собой мультиплексор (дерево передающих транзисторов), входы данных которого настраиваются так называемыми конфигурируемыми ячейками памяти SRAM. Обычно используются LUT на 4,5 переменных, уже применяются LUT на 6 и даже на 7 переменных. На рис. 1.13 изображен логический элемент ПЛИС типа FPGA на 4 входных переменных, SRAM – ячейки конфигурационной памяти, в которую записывается таблица истинности требуемой логической функции, А, В, С, D – входные переменные, которые, как и выход, коммутируются с помощью конфигурируемых матриц межсоединений, не изображённых нарис. 1.13:

Рис. 1.13. Транзисторная схема LUT

с числом входов n = 4 (мультиплексор 16–1)

25

Моделирование логического элемента LUT на одну переменную

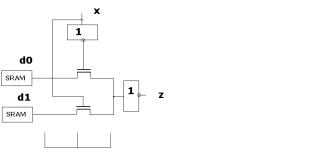

Основой структуры ЛЭ ПЛИС FPGA (см. рис. 1.13) является мультиплексор LUT на одну переменную. Рассмотрим такой элементарный мультиплексор, как селектор на 2 канала –

MS 2-1 (рис. 1.14).

аб

Рис. 1.14. Мультиплексор селектор MS 2-1 на 2 канала:

а– (УГО) элементарного мультиплексора – селектора на 2 канала;

б– реализация MS 2-1 на передающих МОП транзисторах

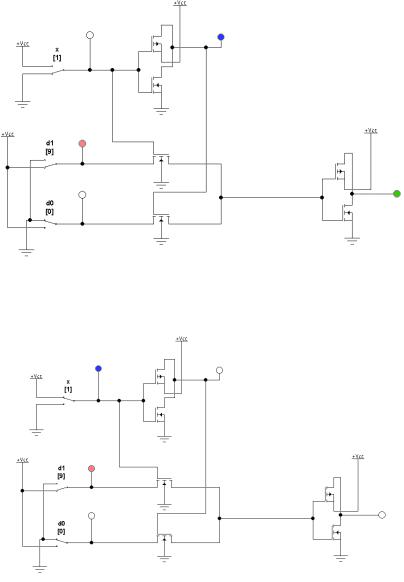

Выполним моделирование LUT для n = 1 в системе схемотехнического моделирования NI Multisim 10 фирмы National Instruments Electronics Workbench Group (рис. 1.15, 1.16). Таким образом, модель LUT на одну переменную «работает».

В настоящее время уже используются LUT с числом входов n = 5, 6 и даже n = 7. Сложной задачей является проверка работоспособности (диагностирование) LUT в процессе производства и эксплуатации ПЛИС. Дело в том, что необходимо в общем

случае проверить активирование всех 2n цепочек передающих

транзисторов для всех 22n значений настроек конфигурационной памяти, т.е. требуется подать на соответствующий LUT комби-

национный автомат, имеющий 2n n входов 22n n двоичных наборов, что очень много уже для n = 5. Все эти наборы надо

26

Рис. 1.15. Моделирование LUT на одну переменную в системе схемотех-

нического моделирования NI Multisim 10 фирмы National Instruments Electronics Workbench Group (передачаснулевогоканала– d0 = 0, х= 0)

Рис. 1.16. Моделирование LUT на одну переменную в системе схемотех-

нического моделирования NI Multisim 10 фирмы National Instruments Electronics Workbench Group (передачаспервогоканала– d1 = 1, х= 1)

27

загружать и оценивать выходную реакцию LUT. Поэтому задача диагностирования такой логики является сложной комбинаторной проблемой, при решении которой применяются методы исследования операций.

1.4. Моделирование и минимизация автомата в системе схемотехнического моделирования

NI Multisim 10 фирмы National Instruments Electronics Workbench Group

Рассмотрим в качестве примера моделирование и минимизацию автомата распознавателя заданной последовательности.

Пусть необходимо распознать последовательность 0232 двоичного двухразрядного сигнала.

Правильная последовательность будет передана 4 тактами, и еще 3 такта передают неправильную последовательность: продемонстрируем, как получилось такое количество тактов, сведем их в табл. 1.5.

Таблица 1 . 5 Сведение тактов

a |

0 |

1 |

1 |

1 |

b |

0 |

0 |

1 |

0 |

|

| |

| |

| |

|

a |

0 |

0 |

0 |

|

b |

1 |

0 |

1 |

|

Как видно из таблицы, верхние строки показывают правильную передачу последовательности, а нижние – последовательность с нарушениями.

По этим данным построим первичную таблицу (табл. 1.6) переходов, в которую сведем все эти такты, она будет соответствовать конечному автомату-распознавателю последовательно-

сти 0232.

28

|

|

|

|

|

|

|

|

Таблица |

1 . 6 |

|

|

|

Первичная таблица переходов |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

№ такта |

|

|

|

ab |

|

|

z1 |

|

z2 |

|

00 |

|

01 |

|

11 |

10 |

|

|

|||

|

|

|

|

|

|

|

||||

1 |

(1) |

|

5 |

|

|

2 |

|

0 |

|

0 |

2 |

6 |

|

|

|

3 |

(2) |

|

0 |

|

0 |

3 |

|

|

7 |

|

(3) |

4 |

|

0 |

|

0 |

4 |

|

|

|

|

|

(4) |

|

1 |

|

0 |

5 |

(6) |

|

(5) |

|

|

|

|

0 |

|

1 |

6 |

|

|

|

|

|

|

0 |

|

1 |

|

7 |

|

|

(7) |

|

|

|

|

0 |

|

1 |

Получим минимизированную таблицу переходов (табл. 1.7).

Таблица 1 . 7 Минимизированная таблица переходов

№ группы |

|

|

|

|

|

|

|

ab |

|

|

|

|

|

строк |

|

00 |

|

|

01 |

|

|

|

11 |

10 |

|

||

I (1+5) |

|

(1) |

|

|

(5) |

|

|

|

3 |

2 |

|

||

II(2+6) |

|

(6) |

|

|

|

|

|

|

|

(2) |

|

||

III(3+4+7) |

|

|

|

|

(7) |

|

|

|

(3) |

(4) |

|

||

Теперь получим таблицу переходов-выходов (табл. 1.8). |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

Таблица 1 . 8 |

|||

|

|

Таблица переходов-выходов |

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

у2у1(t) |

|

|

|

|

|

ab |

|

|

|

|

|

|

|

|

00 |

|

01 |

|

|

11 |

|

10 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|||||

|

|

0 |

|

1 |

|

|

3 |

2 |

|

y2 y1 t 1 |

|

||

00 |

|

00 |

|

00 |

|

|

|

|

01 |

|

|||

|

|

~ |

|

|

z1z2 |

||||||||

|

|

|

|

|

|

|

|

|

00 |

|

|||

|

|

00 |

|

01 |

|

|

|

|

|

|

|

||

|

|

4 |

|

5 |

|

|

7 |

6 |

|

|

|

||

01 |

01 |

|

|

|

|

|

11 |

|

01 |

|

|

|

|

|

|

01 |

|

~ |

|

|

00 |

|

00 |

|

|

|

|

|

|

12 |

|

13 |

|

|

15 |

14 |

|

|

|

||

11 |

|

~ |

11 |

|

11 |

11 |

|

|

|

||||

|

|

|

|

01 |

|

|

00 |

10 |

|

|

|

||

10 |

|

8 |

|

9 |

|

|

11 |

10 |

|

y2 y1 t 1 |

|||

|

~ |

|

~ |

|

|

~ |

|

~ |

|

|

|

||

|

|

|

|

|

|

z1z2 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

||

29

На основании таблицы переходов – выходов получаем все переключательные функции, описывающие наш автомат в символической форме:

y2 t 1 7,13,14,15 0,1, 2, 4, 6 ,y1 t 1 2, 4, 6, 7,13,14,15 0,1 ,

z1 14 0,1, 2, 4, 6, 13,15 ,z2 1, 4,13 0, 2, 4, 6, 7,14,15 .

Данный вид переключательных функций понадобится нам для моделирования автомата на мультиплексоре и дешифраторе.

Для реализации автомата на «гибкой» логике необходимы переключательные функции, записанные в буквенной форме. Поэтому для каждой переключательной функции составим таблицу и сразу минимизируем по карте Карно.

|

|

|

|

Таблица 1 . 9 |

|

Карта Карно минимизации функции у2(t + 1) |

|||||

|

ab |

|

|

|

|

у2у1(t) |

|

11 |

|

|

|

|

00 |

01 |

|

10 |

|

00 |

0 |

0 |

~ |

|

0 |

01 |

0 |

~ |

1 |

|

0 |

11 |

~ |

1 |

1 |

|

1 |

10 |

~ |

~ |

~ |

|

~ |

На основании данной таблицы функция для у2 будет выглядеть следующим образом:

y2 t 1 by1 t Vay2 t

На основании данной таблицы функция для у1 будет выглядеть следующим образом:

y1 t 1 y1 t Vab.

30