- •2.5 Режим стабилизации

- •2.6. Режим управления

- •3 Анализ надежности

- •3.1 Количественный анализ надежности

- •3.1.1 Группировка данных

- •3.2 Выбор теоретического закона распределения

- •3.3 Определение параметров закона распределения

- •3.4 Проверка правильности принятой гипотезы

- •3.5 Определение точности оценок параметров распределения

- •3.6 Построение графиков теоретического распределения

- •3.7 Оценка уровня надежности

- •4 Разработка функциональной схемы кпа

- •4.1 Анализ существующего технического процесса

- •4.2 Разработка функциональной схемы кпа ап-34б

- •4.2.1 Контроль отдельных агрегатов ап

- •4.2.2 Проверка блоков питания четырех каналов агрегата управления

- •4.2.3 Проверка компенсационных датчиков крена и тангажа

- •4.2.4 Проверка пульта управления

- •4.2.5 Проверка блока усилителей

- •4.2.6 Проверка датчиков угловых скоростей и корректора высоты

- •5 Разработка принципиальной схемы кпа ап-34б

- •5.1 Обоснование выбора элементной базы

- •5.1.1 Выбор микроконтроллера

- •5.1.2 Выбор модулей цап и ацп

4.2.6 Проверка датчиков угловых скоростей и корректора высоты

Проверка датчиков угловых скоростей крена, тангажа, рысканья (блоки 24-26) и корректора высоты (блок 28) производится без подключения к основному комплекту автопилота. Такое решение позволяет упростить схему проверки и исключить возможность появления погрешностей, вызванных использованием, в качестве имитаторов сигналов от датчиков, вакуумный насос и поворотную платформу.

Датчики угловых скоростей крена, тангажа и рысканья (блоки 24-26) устанавливаются на поворотную платформу (блок 33). Поворотная платформа предназначена для имитации угловых скоростей вращения вертолета вокруг 3-х пространственных осей. Сигналы угловых скоростей снимаются с датчиков и поступают на блок согласования уровней. Далее схема проверки осуществляется, так же, как в случае с остальными контролируемыми параметрами автопилота.

В корректоре высоты (блок 28) датчиком, измеряющим изменение барометрической высоты полета, является блок анероидных коробок. Вследствие чего, для имитации изменения давления атмосферы с набором высоты, мною принято решение использовать вакуумный вентилятор со схемой его управления (блок 2) и управляемый игольчатый клапан. Вакуумный насос, согласно программе вычислительного устройства, создает нужное разряжение, а с корректора высоты (блок 28) снимается сигнал, соответствующей этому давлению, и подается на блок согласования уровней (блок 29). Для обеспечения возможности контроля величины разряжения используются цифровой манометр (блок 27), с которого, в вычислитель (блок 1) поступает цифровой сигнал, соответствующий давлению. Далее схема проверки осуществляется, так же, как в случае с остальными контролируемыми параметрами автопилота.

5 Разработка принципиальной схемы кпа ап-34б

5.1 Обоснование выбора элементной базы

5.1.1 Выбор микроконтроллера

При разработке принципиальной схемы КПА АП-34Б (чертеж ДП 2010.363.001.004 Э3) основными критериями выбора микроконтроллера стали: быстродействие - так как стоит задачи генерации и анализа большого количества сигналов переменного тока с частотой 400Гц, и достаточное количество портов ввода-вывода для осуществления параллельного контроля и управления блоками КПА. Из представленного ассортимента микроконтроллеров на рынке, предъявленным требованиям удовлетворяет ATMega128.

Характеристики ATMega128 8 битный AVR микроконтроллеры со 128 КБ внутрисистемно программируемой Flash памяти:

- Высококачественный низко потребляющий 8- битный AVR микроконтроллер;

- передовая RISC архитектура:

- 133 команд, большинство которых выполняется за один тактовый цикл;

- 32 8-битных рабочих регистра общего применения;

- полностью статическая архитектура;

- производительность до 16 MIPS при тактовой частоте 16 МГц;

- встроенный двухцикловый умножитель;

- энергонезависимая память программ и данных;

-128 КБ внутрисистемно программируемой Flash памяти программы, способной выдержать 10 000 циклов записи/стирания;

- вспомогательная секция загрузочной программы с независимым битом защиты:

выбираемый размер загрузочной памяти: 1, 2, 4 или 8 КБ;

реальная функция считывания при программировании;

- 4 КБ EEPROM, способной выдержать 100 000 циклов записи/стирания;

- 4 КБ встроенной SRAM памяти (статическое ОЗУ);

- возможность работы с внешней памятью объемом до 64 КБ;

- программируемая защита от считывания ;

- JTAG (IEEE 1149.1 совместимый) интерфейс;

- возможности граничного сканирования в соответствии со стандартом JTAG;

- программирование битов защиты Flash и EEPROM;

- поддержка встроенной отладки;

- 15 полных сообщений объектов с раздельными метками и масками;

- режимы передачи, приема, автоматического ответа и приема кадров;

- максимальная скорость передачи 1 МБит/с при рабочей частоте 1 МГц;

- характеристики периферии:

- программируемый сторожевой таймер со встроенным генератором;

- 8- битный синхронный таймер/счетчик 0;

-10 – разрядный предварительный делитель;

- внешний счетчик событий;

- выход сравнения или 8 – битного ШИМ сигнала;

- 8- битный синхронный таймер/счетчик 2;

- 10 – разрядный предварительный делитель;

- внешний счетчик событий;

- выход сравнения или 8 – битного ШИМ сигнала;

- 32 кГц генератор для выполнения функций часов реального времени;

- два 16- битных синхронных таймера/счетчика 1 и 3;

- 10 – разрядный делитель;

- вход захвата с подавителем шумов;

- внешний счетчик событий;

- три выхода сравнения или 16- битного сигнала с ШИМ;

- выход модулятора сравнении;

- 8 канальный 10 битный SAR АЦП;

- 8 несимметричных каналов;

- 7 дифференциальных каналов;

- 2 дифференциальных канала с программируемым коэффициентом усиления 1, 10 или 100;

- встроенный аналоговый компаратор;

- байт- ориентированный последовательный 2- проводный интерфейс;

- двойной программируемый последовательный USART;

- ведущий/ведомый SPI интерфейс;

- специальные характеристики микроконтроллера:

- сброс при включении питания и детектор кратковременных пропаданий питания;

- встроенный откалиброванный генератор;

- пять режимов пониженного потребления: Idle, ADC Noise Reduction, Power-Save, Power-down и Standby;

- программное переключение рабочей частоты;

- отключение всех подтягивающих транзисторов;

- порты ввода - вывода и корпусное исполнение:

- 53 программируемых линии портов ввода-вывода;

- 64 выводные TQFP, QFN и CA-BGA корпуса ;

- диапазон напряжения питания от 2.7 до 5.5 В;

- индустриальный и автомобильный рабочие температурные диапазоны;

- максимальная рабочая частота:

- 8 МГц при 2.7 В питании у микроконтроллеров с индустриальным диапазоном;

- 16 МГц при 4.5 В питании у микроконтроллеров с индустриальным диапазоном;

- 0.5 мкА при напряжении питания 1.8 В.

Общее описание AT Mega 128:

AT Mega 128 – низкопотребляющий 8 битный КМОП микроконтроллер с AVR RISC архитектурой. Выполняя команды за один цикл, AT Mega 128 достигает производительности 1 MIPS при частоте задающего генератора 1 МГц, что позволяет разработчику оптимизировать отношение потребления к производительности.

AVR ядро объединяет богатую систему команд и 32 рабочих регистра общего назначения. Все 32 регистра непосредственно связаны с арифметико-логическим устройством (АЛУ), что позволяет получить доступ к двум независимым регистрам при выполнении одной команды. В результате эта архитектура позволяет обеспечить в десятки раз большую производительность, чем стандартная CISC архитектура.

AT Mega 128 имеет следующие характеристики: 128 КБ внутрисистемно программируемой Flash память программы, 4 КБ EEPROM память данных, 4 КБ SRAM (статическое ОЗУ), 53 линии ввода - вывода общего применения, 32 рабочих регистра общего назначения, часы реального времени, четыре гибких таймера/счетчика со схемой сравнения и генератором сигнала с ШИМ, 2 USART, байт- ориентированный последовательный 2-х проводный интерфейс, 8 канальный АЦП, программируемый сторожевой таймер со встроенным генератором, SPI порт, JTAG порт с поддержкой внутрисистемной отладки и пять программно инициализируемых режима пониженного потребления.

В режиме Idle останавливается ядро, а SRAM, таймеры/счетчики, SPI порт и система прерываний продолжают функционировать. В Power-down режиме содержимое регистров сохраняется, но останавливается задающий генератор и отключаются все внутренние функции микропроцессора до тех пор, пока не произойдет прерывание или аппаратный сброс. В режиме Power-save асинхронные таймеры продолжают функционировать, позволяя отсчитывать временные интервалы в то время, когда микропроцессор находится в режиме сна. В режиме ADC Noise Reduction останавливается вычислительное ядро и все модули ввода-вывода, за исключением асинхронного таймера и самого АЦП, что позволяет минимизировать шумы в течение выполнения аналого-цифрового преобразования. В Standby режиме задающий генератор работает, в то время как остальная часть прибора бездействует. Это позволяет быстро сохранить возможность быстрого запуска приборов при одновременном снижении потребления.

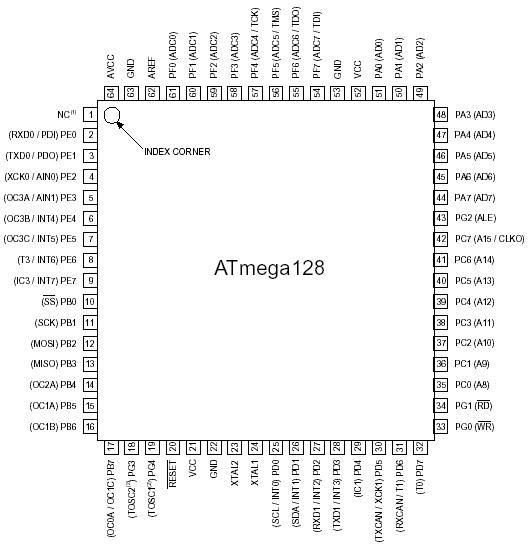

Рисунок 17 - Структурная схема AT Mega 128

Рисунок 18 – Цоколевка корпуса AT Mega 128

Прибор изготовлен по высокоплотной энергонезависимой технологии изготовления памяти компании Atmel. Встроенная ISP Flash позволяет перепрограммировать память программы в системе через последовательный SPI интерфейс программой-загрузчиком, выполняемой в AVR ядре, или обычным программатором энергонезависимой памяти. Программа-загрузчик способна загрузить данные по любому интерфейсу, имеющегося у микроконтроллера. Программа в загрузочном секторе продолжает выполняться даже при загрузке области памяти прикладной программы, обеспечивая реальный режим "считывания при записи". Объединив 8- битное RISK ядро и самопрограммирующейся внутри системы Flash памятью корпорация Atmel сделала прибор AT Mega128 мощным микроконтроллером, обеспечивающим большую гибкость и ценовую эффективность широкому кругу управляющих устройств.

AT Mega 128 поддерживается различными программными средствами и интегрированными средствами разработки, такими как компиляторы C, макроассемблеры, программные отладчики/симуляторы, внутрисхемные эмуляторы и ознакомительные наборы.