- •Раздел 1. Архитектура микропроцессоров 22 ч., 6 ч., пз.

- •Тема 1.1 История развития и классификация микропроцессоров.

- •1.1.1 Основные определения

- •1.1.2 История развития микропроцессоров

- •1.1.3 Принципы построения процессорных эвм

- •1.1.4 Классификация мп

- •По назначению.

- •Тема 1.2 Структура микропроцессора (6 час). (можно 4 час)

- •Устройство управления уу (Кузин , Жаворонков с. 100-102-106)

- •Тема 1.3 Поколения микропроцессоров (Корнеев, Киселёв, с. 114-118)

- •Тема 1.4 Система команд микропроцессора

- •Тема 1.2 Структура микропроцессора Альбом л. 31; (1) с. 151-166;

- •1.2.1 Структура и назначение устройств эвм (Калабеков с. 193-196)

- •Функционирование процессора (микропроцессора) (Калабеков, с.200-202)

- •Внутренняя структура микропроцессора (Калабеков с. 235)

- •1.2.4 Функциональное обозначение и технические данные мп кр580 вм80а

- •Тема 1.4 Система команд микропроцессора

- •1.4.1 Формат команд и данных (Калабеков с. 238)

- •1.4.2 Способы адресации

- •1.4.3 Система команд микропроцессора

- •Тема 1.3 Поколения микропроцессоров

- •1.3.1 История развития вычислительной техники

- •1.3.2 Классификация компьютеров

- •1.3.3 Основные характеристики микропроцессоров

- •1.3.4 Классификация микропроцессоров

- •1.3.5 Микропроцессорные комплекты

- •1.3.6 Направления и этапы развития мп

- •Практическая работа № 1

- •Пр № 2,3 Программирование циклических и разветвлённых процессов

- •1. Апгоритм перемножения двоичных чисел без знака

- •3. Кодирование команд на языке ассемблера

- •4. Программирование с использованием регистра признаков

- •Тема 1.4 Режимы работы микропроцессоров

- •1.4.1 Состав и назначение узлов микропроцессорной системы

- •1.4.2 Функционирование микропроцессорной системы

- •1.4.3 Пример выполнения микропрограммы

- •1.4.4 Информация о состоянии процессора

- •1.4.5 Режимы работы микропроцессора

- •1.4.6 Система прерываний (Угрюмов, с. 270)

- •Раздел 2 Принципы функционирования микропроцессоров

- •Тема 2.1 Память как функциональны узел микропроцессорной системы мпс

- •2.1.1 Назначение, параметры и классификация запоминающих устройств зу

- •2.1.2 Статические оперативные запоминающие устройства созу (Угрюмов, с. 221)

- •2.1.3 Динамические оперативные запоминающие устройства дозу

- •2.1.4 Масочные постоянные запоминающие устройства пзу (м)

- •2.1.5 Однократно программируемые ппзу (prom)

- •2.1.6 Репрограммируемые (мнгократнопрограммируемые) рпзу с электрическим стиранием (эсппзу)

- •Тема 2.2 Принципы доступа мп к адресному пространству

- •2.2.1 Память с адресным доступом

- •2.2.2 Память с последовательным доступом

- •2.2.4 Организация кэш-памяти

- •Тема 2.3 Принципы формирования адресного пространства

- •2.3.1 Разбиение адресного пространства на блоки озу, пзу, увв, внешних зу.

- •2.3.2 Сигналы управления памятью и внешними устройствами

- •2.3.3 Входные и выходные сигналы микросхем памяти

- •2.3.4 Абсолютная и неабсолютная адресация модулей памяти

- •Практическая работа 4

- •Практическая работа №5

- •2.3.5 Виртуальная память

- •2.3.4 Расслоение памяти

- •Тема 2.4 Память как функциональный узел (2 часа)

- •2.4. 2 Накопители на жёстких магнитных дисках нжмд

- •2.4.3 Характеристики накопителей на жёстких дисках

- •2.4.4 Технологии чтения-записи

- •2.4.5 Лазерные диски cd

- •2.4.6 Лазерные диски dvd

- •2.4.7 Магнитооптические технологии

- •Раздел 4 Микропроцессорные системы

- •Тема 4.1 Организация функционирования систем

- •4.1.1 Назначение и классификация интерфейсов, сигналы взаимодействия

- •Шинные формирователи

- •Буферные регистры

- •Параллельный периферийный адаптер ппа

- •Программируемый последовательный интерфейс кр580вв51а

- •Тема 4.2 Система прерываний (Угрюмов, с. 270)

- •4.2.1 Назначение и принципы организация прерываний

- •4.2.2 Средства обслуживания прерываний микропроцессора к1821вм85

- •4.2.3 Сигналы блока управления прерываниями и ввода/вывода

- •4.2.4 Контроллеры прерываний

- •4.2.5 Функционирование мп при обслуживании прерываний

- •Тема 4.3 Прямой доступ к памяти

- •Раздел 3. Микроконтроллеры

- •Тема 3.1. Назначение и принцип работы микроконтроллеров

- •3.1.1 Общие сведения о микроконтроллерах

- •3.1.2 Микроконтроллеры 8051 (к1816ве51 и к1830ве51)

- •3.1.3 Структурные схемы и назначение выводов мк 8051 (к1816ве51 и к1830ве51)

- •Программирование микроконтроллеров мк 8051 ( к1816ве51 и к1830ве51)

- •Тема 3.2 Микроконтроллеры серии avr фирмы Atmel.

- •3.2.1 Общая характеристика микроконтроллеров avr

- •3.2.2 Состав и организация микроконтроллеров avr

- •3.2.3 Система команд микроконтроллера avr фирмы Atmel

- •Тема 3.3 Принципы программирования микроконтроллеров на языке Ассемблера

- •3.3.1 Состав и форма записи программы

- •3.3.2 Директивы

- •3.3.3 Операторы

- •3.3.4 Простейшая задача

- •3.3.5 Описание программы

- •Практическая работа 7

- •Описание программы

- •3.3.6 Трансляция и отладка программы микроконтроллеров avr (Белов, с. 303)

- •3.3.7 Программа управления программатором мк avr

- •3.3.8 Программатор микроконтроллеров avr (Белов, с. 323)

- •3.3.9 Модуль программатора basic stamp 2 (вs-2)

- •Микропроцессорный контроллер мпк радиостанции рс-46м Назначение радиостанции рс-46м

- •Функционирование микропроцессорного контроллера.

- •Распределение адресного пространства мпк радиостанции рс-46м

- •Устройство приёмник-генератор сигналов пгс

- •Структурная схема устройства пгс

- •Плата ввода-вывода сигналов ввс

- •Плата приёмника-генератора сигналов пгс

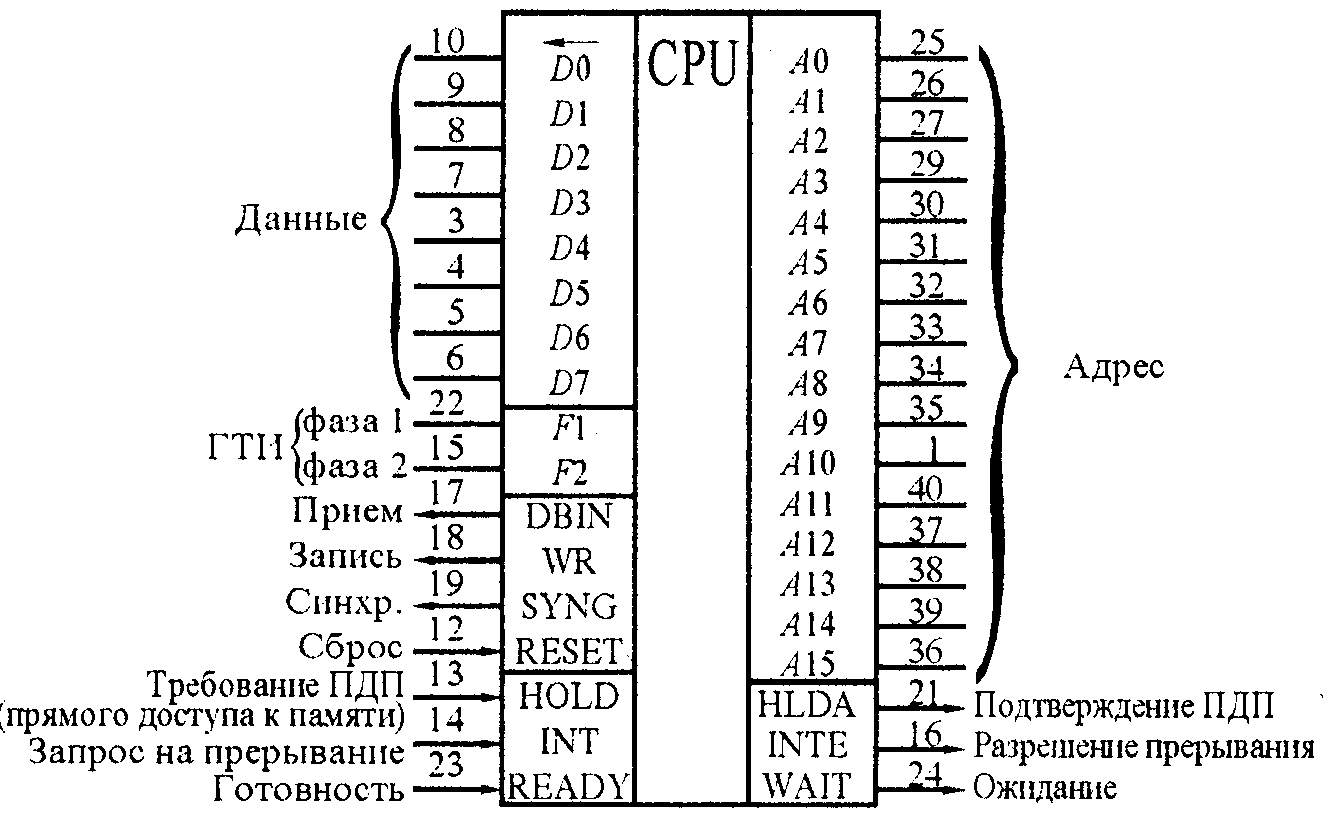

1.2.4 Функциональное обозначение и технические данные мп кр580 вм80а

МП КР580 ВМ80А предназначен для параллельной обработки 8-разрядных слов и имеет фиксированную систему команд. Выполнен по п –МОП технологии, выпускает-ся в 40-контактном пластмассовом корпусе (см. рисунок 1.4).

Параметры. Длина обрабатываемого слова – 8 бит; объём адресуемой памяти – 64 Кбайт; число базовых команд – 78; время выполнения команд – от 2 до 8 мкс; произ-водительность – 625000 операций в секунду; тактовая частота – 2 МГц; потребляемая мощность – 1,5 Вт; максимальное число подключаемых внешних УВВ – 256.

Условное графическое обозначение УГО и назначение выводов микропроцессора КР580ВМ80А приведено на рисунке 1.4.

Рисунок 1.4 – УГО и назначение выводов МП КР580 ВМ80А

Назначение выводов. А0… А15 – адресные; 0…7 – информационные (данные); F1, F2 – для подключения ГТИ; WR - строб записи, при его низком уровне адресованная ячейка памяти или ВУ выполняют операцию записи; SYNG – синхронизация; RESET – выходной сигнал сброса для внешних модулей системы; HOLD – сигнал захвата шин, требование прямого доступа к памяти ПДП, формируется внешним устройством; READY – готовность памяти или внешних устройств к обмену с МП, если готовности нет, МП находится в состоянии ожидания; HLDA – сигнал подтверждения захвата, ответ на сигнал HOLD; INTE, WAIT, INT, DBIN – назначение указано на рисунке 1.4.

Тема 1.4 Система команд микропроцессора

1.4.1 Формат команд и данных (Калабеков с. 238)

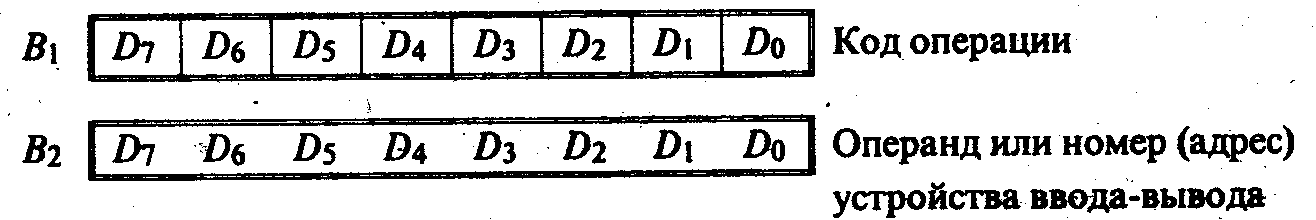

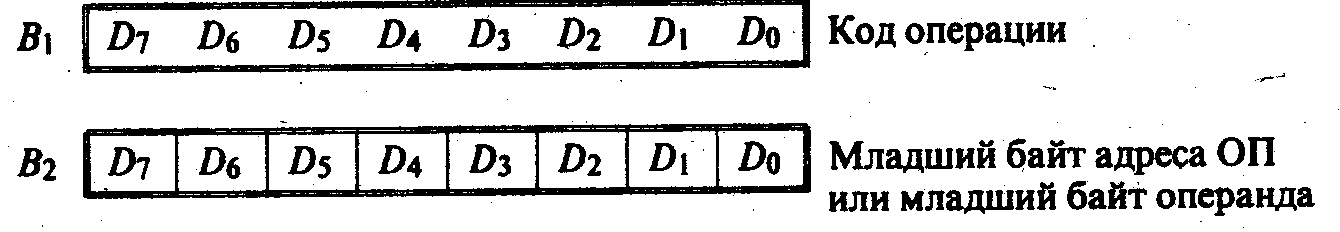

Обрабатываемые данные и результаты обработки хранятся в ОП в виде 8-разряд-ных чисел (байтов) и имеют формат, приведённый на рисунке 1.5, а.

9

Для команд применяются однобайтовые (рисунок 1.5, б), двухбайтовые (рисунок 1.5, в) и трёхбайтовые (рисунок 1.5, г) форматы.

В первом байте двухбайтовой команды указывается вид выполняемой операции, во втором – приводится число, являющееся операндом при выполнении операции, либо адрес устройства ввода или вывода при обмене данными с периферийными устройствами.

а)

![]()

б)

![]()

в)

Г)

Рисунок 1.5 – форматы а) данных; б)однобайтовой команды;

в)двухбайтовой команды; г) трёхбайтовой команды

В первом байте трёхбайтовой команды указывается вид исполняемой операции, второй и третий байты используются для указания двухбайтового адреса команды (при выполнении условных и безусловных переходов и обращении к подпрограммам), или адреса ячейки ОП, содержимое которой является операндом, или двухбайтового операнда. Байт В2 – младший, В3 – старший.

1.4.2 Способы адресации

Команда должна содержать указания: о виде операции, об адресах источников и приёмнике операндов. Различают несколько способов адресации.

Прямая адресация. Адресом операнда является указанный в коде операции адрес регистра МП (см. рисунок 1.3). Адреса регистров приведены в таблице. М – это ячейка оперативной памяти, адресом которой служит содержимое пары регистров Н L.

Таблица 1.1 – Адреса регистров при прямой адресации

Регистр |

В |

С |

D |

Е |

Н |

L |

М |

А |

Адрес регистра |

000 |

001 |

010 |

011 |

100 |

101 |

110 |

111 |

10

Примеры команд с прямой адресацией.

В кодовой комбинации команды 01 001 010 два старших разряда (01) определяют вид операции (пересылка содержимого одного регистра в другой). В разрядах 6, 5, 4 (001) и 3, 2, 1 (010) указаны адреса регистров С и D. По этой команде содержимое регистра D пересылается в регистр С.

В команде 10 000 010 в разрядах 8, 7, 6, 5, 4 (10000) указан код операции (суммирование), в разрядах 3, 2, 1 указан адрес источника операндов (регистр D). При выполнении операции суммирования источником другого операнда и приёмником результата является аккумулятор (регистр А).

Непосредственная адресация. При этом способе адресации операнды (один или два) задаются непосредственно в команде вслед за кодом операции во втором или во

втором и третьем байтах.

Примеры команд с непосредственной кадресацией.

1. АDI В1 11 000 110 А ← (А) + <В2>

В2 01 001 100

По команде АDI суммируется содержимое аккумулятора с содержимым второго байта команды (01 001 100).

2. МVI D В1 00 010 110 D ← <В2>

В2 01 001 110

По команде МVI содержимое второго байта команды (01 001 110) пересылается в регистр D, адрес которого (010) приведён в разрядах 6, 5, 4 первого байта команды.

3. LХI D В1 00 010 001 D ← <В3>; E ← <В2>

В2 01 100 101

B3 10 100 101

По команде LХI содержимое второго и третьего байтов команды пересылается, соответственно, в младший и старший регистры пары регистров DЕ. Пара регистров DЕ указана адресом (010) первого из них в разрядах 6, 5, 4 первого байта команды.

Косвенная адресация. При этом способе адресации в команде отмечается пара регистров общего назначения РОН (указанием первого из них), содержимое которой служит адресом, по которому в ОП находится операнд.

Примеры команд с косвенной адресаций.

1. LDAX B 00 001 010 A ← [(BC)]

По команде LDAX В в аккумулятор загружается содержимое ячейки ОП, адресом которой служит содержимое пары регистров ВС (эта пара указывается адресом регистра С (001), в разрядах 6, 5, 4).

2. STAX B 00 000 010 [(BC)] ← (A)

По команде STAX В содержимое аккумулятора запоминается в ячейке, адресом которой служит содержимое пары регистров ВС ((эта пара указывается адресом регистра В (000), в разрядах 6, 5, 4).