- •Бийский технологический институт (филиал)

- •Техника двоичной переработки информации Курс лекций

- •Содержание

- •1 Сопряжение аналоговых и цифровых устройств

- •1.1 Процесс аналого-цифрового преобразования

- •1.2 Процесс цифро-аналогового преобразования

- •1.3 Основные характеристики цап и ацп

- •1.4.1 Цап со взвешивающей резистивной матрицей

- •1.4.2 Цап с матрицей r-2r

- •1.5.1 Ацп последовательного счёта

- •1.5.2 Ацп поразрядного кодирования

- •1.5.3 Ацп параллельного действия

- •1.6 Основное уравнение для цап и ацп

- •Литература

- •Ссылки в интернете

- •Контрольные вопросы к разделу

- •2 Запоминающие устройства

- •2.1 Основные параметры зу

- •2.1.1 Емкость зу

- •2.1.2 Организация зу

- •2.1.3 Время выборки зу

- •2.1.4 Время цикла адреса зу

- •2.2 Зу с одномерной адресацией

- •2.3 Зу с двумерной адресацией

- •2.4 Увеличение объёма памяти зу

- •2.4.1 Построение блока зу требуемой разрядности

- •2.4.2 Увеличение числа хранимых слов зу

- •2.4.3 Увеличение разрядности и числа хранимых слов зу

- •2.5 Аппаратные особенности построения статических озу

- •2.6 Аппаратные особенности построения динамических озу

- •2.7 Аппаратные особенности построения пзу

- •2.7.1 Масочные пзу

- •2.7.2 Программируемые пзу

- •2.7.3 Репрограммируемые пзу

- •Литература

- •Ссылки в интернете

- •Контрольные вопросы к разделу

- •3 Программируемые логические интегральные схемы

- •3.1 Обобщённая структурная схема плис

- •3.2 Применение ппзу в качестве плис

- •3.3 Программируемая матричная логика

- •3.4 Программируемые логические матрицы

- •Литература

- •Ссылки в интернете

- •Контрольные вопросы к разделу

- •4 Основные понятия микропроцессорной техники

- •4.1 Микропроцессор. Основные термины и определения

- •4.2 Классификация мп

- •4.3 Структура типового мп

- •4.3.1 Арифметико-логические устройства

- •4.4 Режимы работы мп

- •4.4.1 Нормальный режим работы мп

- •4.4.2 Режим прерывания

- •4.4.3 Режим ожидания

- •4.4.4 Режим прямого доступа к памяти

- •4.5 Система команд однокристального микропроцессора

- •4.6 Периферийные устройства микропроцессорных систем

- •4.6.1 Универсальный синхронно-асинхронный приёмо-передатчик

- •4.6.2 Таймер-счётчик

- •4.6.3 Устройство ввода/вывода параллельной информации

- •4.6.4 Контроллер прямого доступа к памяти

- •4.6.5 Контроллер прерываний

- •4.6.6 Динамическая индикация

- •4.6.7 Динамическая клавиатура

- •Литература

- •Ссылки в интернете

- •Контрольные вопросы к разделу

- •Техника двоичной переработки информации

1.4.1 Цап со взвешивающей резистивной матрицей

В простейшем случае для получения эталонных источников тока I02i можно к источнику напряжения Uref подключить ряд резисторов, сопротивления которых пропорциональны весовым коэффициентам входного кода (см. рисунок 5б). Такие резисторы называют взвешенными. Так как из логики работы ОУ вытекает равенство Ua = Uь = 0, то токи резисторов схемы будут обратно пропорциональны их сопротивлениям

Ii = UREF 2i/R=Ii 2i ,

где

![]() ,

,

и для выходного напряжения устройства справедливо выражение (1).

Недостатком такого решения является широкий диапазон изменения сопротивлений взвешенных резисторов, используемых для формирования разрядных токов. К тому же для обеспечения точности преобразования абсолютные значения сопротивлений этих резисторов должны выдерживаться с прецизионной точностью. Так, в случае 12-разрядного ЦАП сопротивления разрядных резисторов должны отличаться в 211=2048 раз, что весьма трудно выполнить технологически, особенно при производстве ЦАП в виде интегральной микросхемы. Кроме того, данная схема накладывает достаточно жесткие требования на стабильность источника напряжения UREF, так как его ток будет меняться в достаточно широких пределах в зависимости от подаваемого на вход ЦАП значения кода.

1.4.2 Цап с матрицей r-2r

Для преодоления недостатков ЦАП с взвешивающей резистивной матрицей часто используют резистивные R-2R матрицы, выполненные только на резисторах двух номиналов R и 2R.

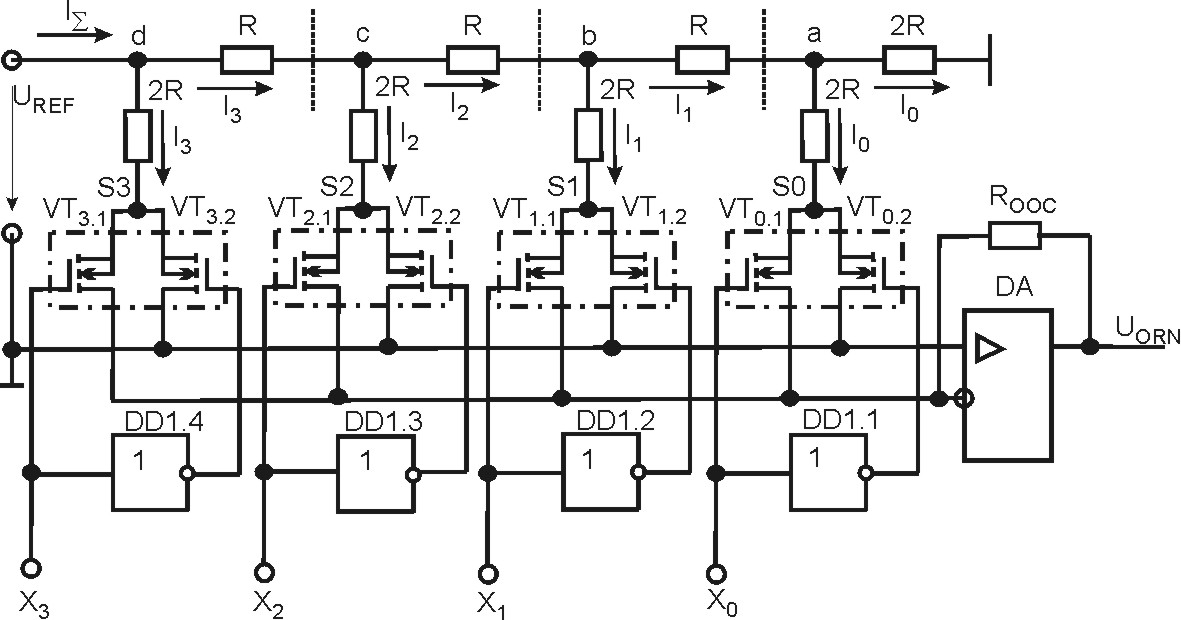

В качестве примера рассмотрим приведенную на рисунке 6 схему 4-разрядного ЦАП с матрицей R-2R. Схема включает R-2R матрицу, четыре переключателя S3, S2, S1, S0 на МДП-транзисторы VT3,1, …, VT0,1 и VT3,2, … , VT0,2, четыре инвертора DD1.4, ... , DD1.1 и ОУ DA1 с цепью отрицательной обратной связи. На входы инвертора подаются сигналы разрядов входного кода X3, …, X0, а на вход матрицы R-2R – напряжение от эталонного источника Uref.

Рисунок 6 – Структурная схема 4-разрядного ЦАП с матрицей R-2R

Рассмотрим сначала работу матрицы R-2R. Для удобства предположим, что на вход ЦАП подан нулевой код (0000).

Тогда выходными сигналами инверторов DD1.4,..., DD1.1 включены транзисторы VT3,2, …, VT0,2 переключателей S3,..., S0, и нижние выводы всех резисторов 2R матрицы подключены к общей шине.

Работа матрицы R-2R основана на том, что выходное сопротивление любой отсекаемой от нее правой части схемы (на рисунке 6 возможные места отсечения показаны пунктирными линиями), содержащей целое число R-2R звеньев определяется параллельным соединением двух цепей, сопротивления каждой из которых равно 2R. Поэтому выходное сопротивление матрицы относительно узла «a» равно R. Аналогично сопротивление матрицы относительно узла «b» также равно R.

Согласно сказанному полное выходное сопротивление матрицы, измеренное относительно узла «d», равно R, и ток, отбираемый матрицей от источника Uref,

![]()

Так как сопротивления ветвей матрицы, подключенных к точке «d» равны, то

![]()

Ток I3,

втекающий в узел «с», также разделится

пополам, то есть

![]() и т.д.

и т.д.

Из приведенного анализа видно, что через переключатели S3, ... , S0 протекают токи, значения которых пропорциональны весовым коэффициентам двоичного кода.

Если на входы некоторых инверторов поданы сигналы лог. 1, то в соответствующих переключателях Si включены транзисторы VTi1 и токи, пропорциональные весовым коэффициентам данных разрядов, попадают на инвертирующий вход ОУ. В этом случае, согласно принципу суперпозиции, для входного тока ОУ справедливо выражение (1), а для выходного напряжения усилителя – выражение (2).

В общем случае для b-разрядного кода можно записать

|

(3) |

|

Если на вход ЦАП подать максимально большое число (все разряды входного кода равны лог. 1), то из выражения (3) легко получить значение максимального напряжения на выходе ЦАП

|

(4) |

На практике для получения простой функции преобразования обычно делают величины RООС и R равными. В результате выражения (3) и (4) приобретают вид выражений (5) и (6) соответственно

|

(5) |

|

(6) |

Полученные выражения показывают, что в ЦАП рассматриваемого типа максимальное выходное напряжение всегда на 1ЕМР меньше опорного напряжения Uref.

При выполнении рассмотренного устройства в виде интегральной схемы (ИС) из нее иногда исключают источник эталонного напряжения Uref и ОУ. Это позволяет расширить функциональные возможности устройства. В частности, если Uref изменяется по заданному закону, схема может быть использована в качестве умножающего преобразователя.

Точность и стабильность параметров устройства в основном зависят от точности выполнения и стабильности сопротивлений его резисторов. Резистор Rooc=R обычно вводится в состав ИС. В самой схеме все резисторы выполнены в виде идентичных по геометрическим размерам областей, одинаково ориентированных относительно осей кристалла. В качестве материала для резисторов используют пленку поликремния, обладающую высокой стабильностью собственного сопротивления.

Погрешность выходных параметров также зависит от падений напряжения на транзисторах токовых переключателей Si. Для компенсации этих погрешностей площади транзисторов выполняются пропорциональными протекающему через них току. Этим достигается равенство падений напряжения на токовых переключателях всех разрядов.

1.5 АЦП

Основная задача при построении АЦП – это обеспечить квантование по уровню по заданному алгоритму. Рассмотрим некоторые возможные аппаратные реализации АЦП.