- •Бийский технологический институт (филиал)

- •Техника двоичной переработки информации Курс лекций

- •Содержание

- •1 Сопряжение аналоговых и цифровых устройств

- •1.1 Процесс аналого-цифрового преобразования

- •1.2 Процесс цифро-аналогового преобразования

- •1.3 Основные характеристики цап и ацп

- •1.4.1 Цап со взвешивающей резистивной матрицей

- •1.4.2 Цап с матрицей r-2r

- •1.5.1 Ацп последовательного счёта

- •1.5.2 Ацп поразрядного кодирования

- •1.5.3 Ацп параллельного действия

- •1.6 Основное уравнение для цап и ацп

- •Литература

- •Ссылки в интернете

- •Контрольные вопросы к разделу

- •2 Запоминающие устройства

- •2.1 Основные параметры зу

- •2.1.1 Емкость зу

- •2.1.2 Организация зу

- •2.1.3 Время выборки зу

- •2.1.4 Время цикла адреса зу

- •2.2 Зу с одномерной адресацией

- •2.3 Зу с двумерной адресацией

- •2.4 Увеличение объёма памяти зу

- •2.4.1 Построение блока зу требуемой разрядности

- •2.4.2 Увеличение числа хранимых слов зу

- •2.4.3 Увеличение разрядности и числа хранимых слов зу

- •2.5 Аппаратные особенности построения статических озу

- •2.6 Аппаратные особенности построения динамических озу

- •2.7 Аппаратные особенности построения пзу

- •2.7.1 Масочные пзу

- •2.7.2 Программируемые пзу

- •2.7.3 Репрограммируемые пзу

- •Литература

- •Ссылки в интернете

- •Контрольные вопросы к разделу

- •3 Программируемые логические интегральные схемы

- •3.1 Обобщённая структурная схема плис

- •3.2 Применение ппзу в качестве плис

- •3.3 Программируемая матричная логика

- •3.4 Программируемые логические матрицы

- •Литература

- •Ссылки в интернете

- •Контрольные вопросы к разделу

- •4 Основные понятия микропроцессорной техники

- •4.1 Микропроцессор. Основные термины и определения

- •4.2 Классификация мп

- •4.3 Структура типового мп

- •4.3.1 Арифметико-логические устройства

- •4.4 Режимы работы мп

- •4.4.1 Нормальный режим работы мп

- •4.4.2 Режим прерывания

- •4.4.3 Режим ожидания

- •4.4.4 Режим прямого доступа к памяти

- •4.5 Система команд однокристального микропроцессора

- •4.6 Периферийные устройства микропроцессорных систем

- •4.6.1 Универсальный синхронно-асинхронный приёмо-передатчик

- •4.6.2 Таймер-счётчик

- •4.6.3 Устройство ввода/вывода параллельной информации

- •4.6.4 Контроллер прямого доступа к памяти

- •4.6.5 Контроллер прерываний

- •4.6.6 Динамическая индикация

- •4.6.7 Динамическая клавиатура

- •Литература

- •Ссылки в интернете

- •Контрольные вопросы к разделу

- •Техника двоичной переработки информации

1.2 Процесс цифро-аналогового преобразования

Процесс цифро-аналогового преобразования предполагает последовательное выполнение следующих операций:

а) формирование в заданном диапазоне изменения выходного сигнала М его дискретных значений U*M, отличающихся на некоторое значение α, и постановка каждому сформированному уровню в соответствие некоторого конкретного значения кода Ki. Таким образом, каждому конкретному значению Ki из принятого кода ставится в соответствие значение выходного U*Mi сигнала. Обычно используется простой алгоритм присвоения значений кодов уровням – сформированные уровни нумеруются в порядке возрастания их величин, начиная с нуля, целыми положительными числами. Так же как и при квантовании (см. п. 1.1), параметр α обычно является константой, но может изменяться по любому закону, если это обусловлено какими-либо практическими соображениями;

б) последовательное, с заданным временным интервалом Tl присвоение выходному сигналу значений выделенных уровней, соответствующих входной последовательности кодов Ki. Так же как и Tд, может изменяться по любому произвольному закону, но обычно является константой.

Если предположить, что α = h и Tl = Tд, то результатом цифро-аналогового преобразования полученной ранее последовательности кодов Кn будет показанная на рисунке 1 ступенчатая функция U*n. Эта функция, хотя и непрерывна во времени, но остается дискретной по уровню, что является результатом погрешности, обусловленной шумом квантования. Сам процесс цифро-аналогового преобразования не вносит собственных принципиальных погрешностей, а лишь материализует погрешности, полученные в АЦП. Реально возникающие при преобразовании погрешности носят чисто инструментальный характер.

Подводя итог, отметим, что погрешности, обусловленные самим алгоритмом работы, возникают только на этапе аналого-цифрового преобразования, и их уменьшение требует уменьшения периода дискретизации Tд и шага квантования h.

1.3 Основные характеристики цап и ацп

Рассмотрим основные электрические характеристики ЦАП и АЦП. Они подразделяются на статические, которые задают конечную точность преобразования, и динамические, характеризующие быстродействие данного класса устройств. Статические характеристи-ки преобразователей определяются видом характеристики преобразования, которая устанавливает соответствие между значениями аналоговой величины и цифрового кода.

Статические свойства ЦАП и АЦП обычно характеризуют следующими параметрами.

– Число разрядов (b) – число разрядов кода, отображающего исходную аналоговую величину, которое может формироваться на выходе АЦП или подаваться на вход ЦАП. При использовании двоичного кода под b понимают двоичный логарифм от максимального числа кодовых комбинаций (уровней квантования) на выходе АЦП или входе ЦАП.

– Абсолютная разрешающая способность – среднее значение минимального изменения сигнала на выходе ЦАП (α), обусловленное увеличением или уменьшением кода на входе на единицу. Для АЦП это среднее значение минимального изменения сигнала на входе (m), приводящее к увеличению или уменьшению выходного кода на единицу. Значение абсолютной разрешающей способности является мерой измерения всех основных статических характеристик данного класса устройств и часто обозначается как ЕМР (единица младшего разряда), или просто МР (младший разряд).

– Абсолютная погрешность преобразования в конечной точке шкалы (δFs) – отклонение реальных максимальных значений входного для АЦП (UIRN) и выходного для ЦАП (UORN) аналоговых сигналов от значений, соответствующих конечной точке идеальной характеристики преобразования (UIRNmax и UIRNmax) (рисунок 2).

1 – идеальная характеристика преобразования;

2 – реальная характеристика преобразования

Рисунок 2 – Иллюстрация абсолютной погрешности преобразования в конечной точке шкалы, напряжения смещения нуля и нелинейности для ЦАП и АЦП

Применительно к АЦП наличие δFs означает, что максимальный выходной код будет сформирован на выходе устройства при входном сигнале Uвх = UIRNmax ± δFs. По аналогии для ЦАП можно сказать, что при подаче на вход максимального кода его выходное напряжение будет отличаться от UORNmax на величину δFs. Обычно δFs измеряется в ЕМР. В технической литературе δFs иногда называют мультипликативной погрешностью.

– Напряжение смещения нуля U0 – для АЦП – это напряжение (UВХ0), которое необходимо приложить к его входу для получения нулевого выходного кода (см. величину U0 на рисунке 2). Для ЦАП – это напряжение, присутствующее на его выходе (UВЫХ0) при подаче на вход нулевого кода. Величина U0 обычно выражается в ЕМР.

– Нелинейность (δL) – отклонение действительной характеристики преобразования от оговоренной линейной, то есть это разность реального напряжения, соответствующего выбранному значению кода и напряжения, которое должно соответствовать этому коду в случае идеальной характеристики преобразования устройства (см. δ'L на рисунке 2). Для ЦАП это напряжение измеряется относительно центров ступеней указанных характеристик (δ'L на рисунке 3).

1 – идеальная характеристика преобразования;

2 – реальная характеристика преобразования

Рисунок 3 – Иллюстрация нелинейности и дифференциальной нелинейности для ЦАП

В качестве оговоренной линейной характеристики используют либо прямую, проведенную через точки (0; Umax), либо прямую, обеспечивающую минимизацию δL, например, среднеквадратическое отклонение всех точек которой от реальной характеристики минимально. Величину δL измеряют в ЕМР

δL= δ'L/h,

или в процентах

δL=100δ'L/Umax,

где δ'L – абсолютное значение нелинейности (см. рисунки 2, 3).

В справочной литературе обычно задается максимально возможная величина δL.

– Дифференциальная нелинейность (δLд). Это отклонение действительного шага квантования δ'Lд от его среднего значения (h) (см. рисунок 3). Величина δLд измеряется либо в ЕМР

δLд=(δ' Lд – h)/h,

либо в процентах

δLд=(δ'

Lд –

h)![]() 100/Umax.

100/Umax.

Величина дифференциальной нелинейности однозначно связана с понятием монотонности характеристик ЦАП и АЦП. Если δLд>lEMP, то приращение выходного сигнала в данной точке характеристики может быть как положительным, так и отрицательным (см. рисунок 3). В последнем случае характеристика преобразования перестает быть монотонной.

Динамические свойства ЦАП и АЦП обычно характеризуют следующими параметрами.

– Максимальная частота преобразования (fC MAX) – наибольшая частота дискретизации для АЦП или максимальная частота изменения кодов на входе ЦАП, при которой заданные параметры преобразователей соответствуют установленным нормам.

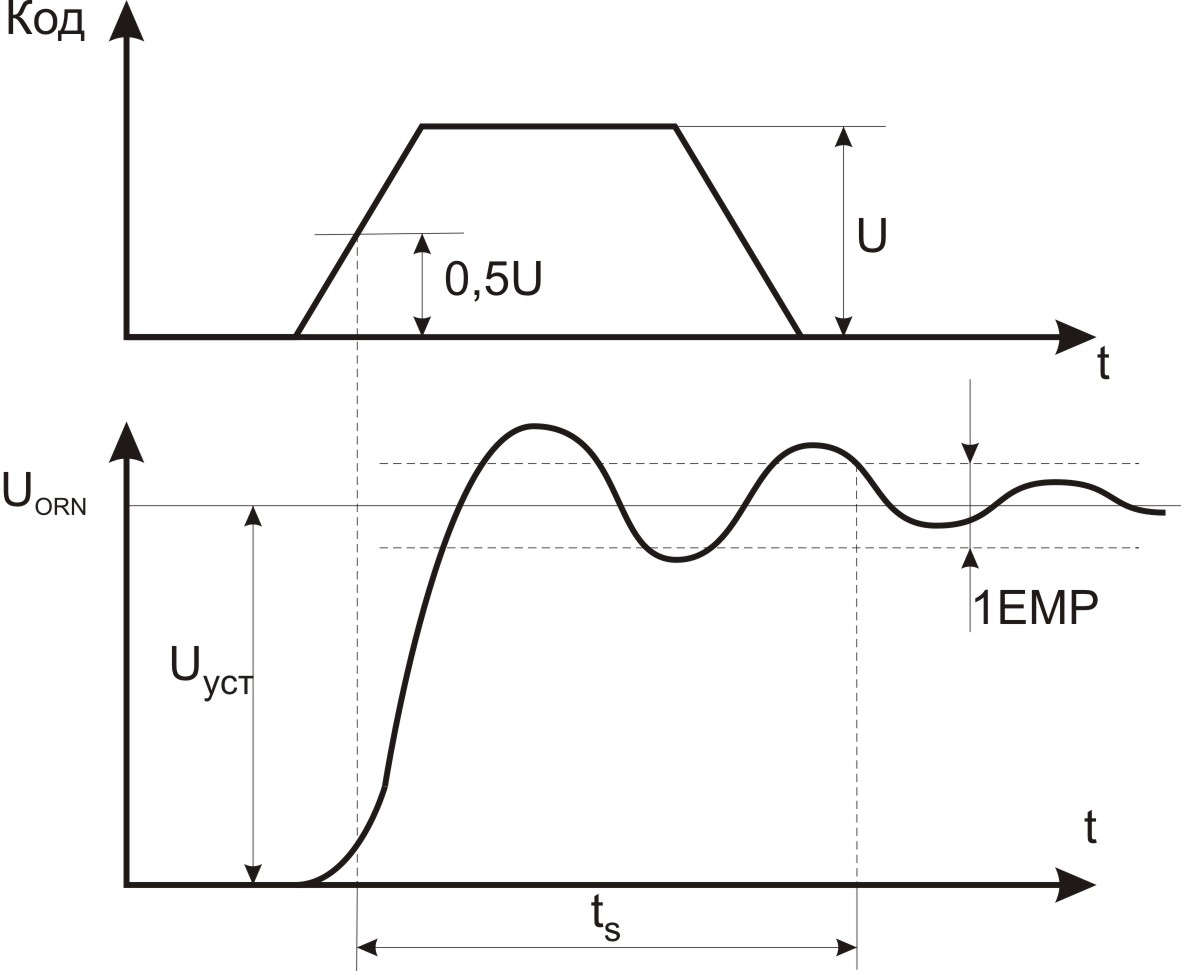

– Время установления выходного сигнала (tS) – интервал от момента заданного изменения кода на входе ЦАП до момента, при котором выходной аналоговый сигнал окончательно войдет в зону заданной ширины, симметрично расположенную относительно установив-шегося значения Uуст. Обычно ширина этой зоны задается равной 1ЕМР (рисунок 4). Отсчет времени tS ведется от момента достижения входным сигналом значения половины логического перепада (точка 0,5U на рисунке 4). Очевидно, значение tS связано с fCmax условием fCmax < 1/(2tS). Аналогичный параметр для АЦП называют временем преобразования (tC).

Рисунок 4 – Иллюстрация к определению времени установления выходного сигнала ЦАП

1.4 ЦАП

При построении ЦАП чаще всего реализуется метод суммирования нескольких различных эталонов, в качестве таких эталонов можно использовать источники напряжения или тока.

На практике наибольшее применение нашли схемы с эталонными источниками тока. Поэтому ниже остановимся только на особенностях построения устройств данного типа.

Принцип построения ЦАП, реализующих метод суммирования токов, иллюстрируется рисунком 5а.

Данное устройство в общем случае содержит b (по числу раз-рядов входного позиционного кода X) источников тока и b управ- ляемых разрядами этого кода переключателей S. Если в i-м разряде входного кода X присутствует сигнал лог. 1 (xi = 1), соответствующий переключатель Si подключает эталонный источник тока I02i к сопротивлению нагрузки Rн (узел «а» схемы). В противном случае (xi = 1) переключатель Si закорачивает соответствующий источник и ток I02i не протекает через нагрузку.

а)

б)

Рисунок 5 – Структурная схема ЦАП с суммированием токов (а) и её реализация с использованием матрицы взвешенных резисторов (б)

В результате ток резистора Rн равен

|

(1) |

и пропорционален значению входного кода. При условии Rн = const выходное напряжение схемы UORN = IORN Rн также пропорционально входному коду.

На практике для получения напряжения, пропорционального входному коду, к выводам «a», «b» подключают операционный усилитель (ОУ) (рисунок 5б) в режиме преобразователя тока в напряжение. Легко увидеть, что для рассматриваемой схемы

UORN = IORN RООС, |

(2) |

то есть выходное напряжение ОУ прямо пропорционально выходному току ЦАП и сопротивлению ROOC и не зависит от сопротивления выходной нагрузки ОУ.

Большинство серийно выпускаемых интегральных схем ЦАП реализуют именно этот принцип. Их отличие состоит лишь в способе получения разрядных токов и используемой схемотехнике.