- •Бийский технологический институт (филиал)

- •Техника двоичной переработки информации Курс лекций

- •Содержание

- •1 Сопряжение аналоговых и цифровых устройств

- •1.1 Процесс аналого-цифрового преобразования

- •1.2 Процесс цифро-аналогового преобразования

- •1.3 Основные характеристики цап и ацп

- •1.4.1 Цап со взвешивающей резистивной матрицей

- •1.4.2 Цап с матрицей r-2r

- •1.5.1 Ацп последовательного счёта

- •1.5.2 Ацп поразрядного кодирования

- •1.5.3 Ацп параллельного действия

- •1.6 Основное уравнение для цап и ацп

- •Литература

- •Ссылки в интернете

- •Контрольные вопросы к разделу

- •2 Запоминающие устройства

- •2.1 Основные параметры зу

- •2.1.1 Емкость зу

- •2.1.2 Организация зу

- •2.1.3 Время выборки зу

- •2.1.4 Время цикла адреса зу

- •2.2 Зу с одномерной адресацией

- •2.3 Зу с двумерной адресацией

- •2.4 Увеличение объёма памяти зу

- •2.4.1 Построение блока зу требуемой разрядности

- •2.4.2 Увеличение числа хранимых слов зу

- •2.4.3 Увеличение разрядности и числа хранимых слов зу

- •2.5 Аппаратные особенности построения статических озу

- •2.6 Аппаратные особенности построения динамических озу

- •2.7 Аппаратные особенности построения пзу

- •2.7.1 Масочные пзу

- •2.7.2 Программируемые пзу

- •2.7.3 Репрограммируемые пзу

- •Литература

- •Ссылки в интернете

- •Контрольные вопросы к разделу

- •3 Программируемые логические интегральные схемы

- •3.1 Обобщённая структурная схема плис

- •3.2 Применение ппзу в качестве плис

- •3.3 Программируемая матричная логика

- •3.4 Программируемые логические матрицы

- •Литература

- •Ссылки в интернете

- •Контрольные вопросы к разделу

- •4 Основные понятия микропроцессорной техники

- •4.1 Микропроцессор. Основные термины и определения

- •4.2 Классификация мп

- •4.3 Структура типового мп

- •4.3.1 Арифметико-логические устройства

- •4.4 Режимы работы мп

- •4.4.1 Нормальный режим работы мп

- •4.4.2 Режим прерывания

- •4.4.3 Режим ожидания

- •4.4.4 Режим прямого доступа к памяти

- •4.5 Система команд однокристального микропроцессора

- •4.6 Периферийные устройства микропроцессорных систем

- •4.6.1 Универсальный синхронно-асинхронный приёмо-передатчик

- •4.6.2 Таймер-счётчик

- •4.6.3 Устройство ввода/вывода параллельной информации

- •4.6.4 Контроллер прямого доступа к памяти

- •4.6.5 Контроллер прерываний

- •4.6.6 Динамическая индикация

- •4.6.7 Динамическая клавиатура

- •Литература

- •Ссылки в интернете

- •Контрольные вопросы к разделу

- •Техника двоичной переработки информации

2.3 Зу с двумерной адресацией

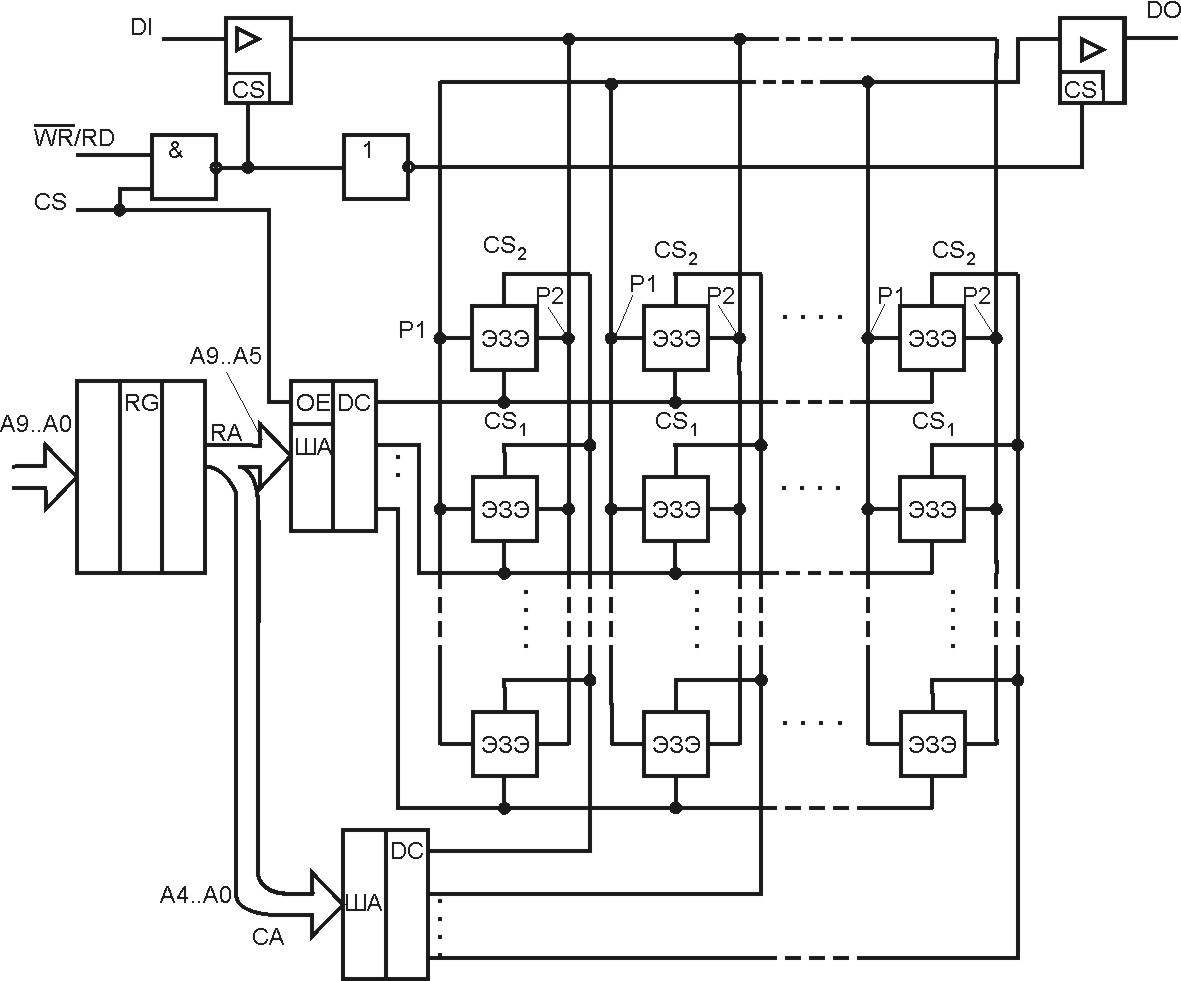

При необходимости побитовой записи-считывания информации применяют структуру памяти с двумерной адресацией (рисунок 16).

Рисунок 16 – Структурная схема ЗУ с двумерной адресацией

Данная структура содержит матрицу ЭЗЭ, статический регистр адреса, дешифраторы строки и столбца, входной и выходной буферные элементы. Однако в отличие от схемы на рисунке 14 каждый ЭЗЭ матрицы содержит не один, а два вывода разрешения работы (CS1 и CS2). При этом информационные выводы р1 и р2 являются обратимыми, то есть позволяют как записывать, так и считывать информацию. Для выбора нужной ячейки на оба входа CS необходимо подать активные логические уровни.

Цепи управления матрицей ЭЗЭ обеспечивают реализацию одного из трех режимов работы:

- хранения, при котором ЭЗЭ отключены от входа и выхода ИС;

- чтения, при котором информация из ЭЗЭ, выбранного по соответствующему адресу, выдается на выход ИС;

- записи, при которой информация со входа ИС записывается по указанному адресу.

Каждому ЭЗЭ матрицы присваивается определенный адрес, поиск которого производится указанием номеров соответствующих строки и столбца. Эти номера формируются на выходах дешифраторов. Адрес ЭЗЭ в виде двоичного числа принимается по адресной шине регистром адреса. Число разрядов регистра адреса однозначно связано с объемом памяти ИС. Число строк и столбцов матрицы ЭЗЭ обычно выбирается равным целой степени числа 2.

Разряды регистра адреса делятся на две группы: одна определяет двоичный адрес строки, другая – двоичный адрес столбца. Каждая группа разрядов адреса подается на соответствующий дешифратор (строк и столбца). Выходные сигналы дешифраторов выбирают требу-емый ЭЗЭ из матрицы.

При чтении (![]() )

содержимое этой ячейки через буферный

элемент выдаётся на шину данных.

)

содержимое этой ячейки через буферный

элемент выдаётся на шину данных.

Режим записи устанавливается путем подачи в усилитель записи сигнала разрешения записи ( ). Этот сигнал открывает входной буферный элемент, и бит входной информации поступает на внутреннюю шину ИС, с которой переписывается в выбранный по соответствующему адресу ЭЗЭ.

Указанные процессы считывания-записи могут осуществляться только в случае, если на вход CS подан разрешающий сигнал. При отсутствии этого сигнала работа дешифратора строки блокируется, что эквивалентно запрещению выборки ЭЗЭ по указанному адресу. В этом случае ИС находится в режиме хранения информации и ее выходы отключены от матрицы ЭЗЭ.

Рассмотренная

организация памяти обеспечивает хранение

![]() кодовых слов, то есть заданному адресу

соответствует один бит информации.

Использование метода двумерной адресации

позво-

ляет максимально упростить

схему ИС, что при заданной площади

кристалла является предпосылкой

получения максимально больших объемов

памяти.

кодовых слов, то есть заданному адресу

соответствует один бит информации.

Использование метода двумерной адресации

позво-

ляет максимально упростить

схему ИС, что при заданной площади

кристалла является предпосылкой

получения максимально больших объемов

памяти.

Для увеличения объёма накопителя можно развить принцип двумерной адресации и использовать трёхмерную, четырёхмерную и т.д. адресации. Соответственно необходимо использовать ЭЗЭ с тремя, четырьмя и т.д. входами CS.

2.4 Увеличение объёма памяти зу

С использованием описанных структур можно строить память с любым заданным объемом информации. Однако на практике приходится иметь дело со стандартным рядом ИС, организация и объем памяти которых заданы. Как правило, эти показатели не совпадают с требованиями конкретной аппаратуры, и встает задача построения на ИС ЗУ заданной организации блока ЗУ с требуемой организацией.