- •1. Однокристальные микро эвм (омэвм)

- •1.1. Общие особенности управляющих микроконтроллеров.

- •1.2 Структура мк-системы управления

- •1.3. Четырехразрядные микроконтроллеры.

- •2. Микроконтроллеры семейства mcs48

- •2.1. Состав семейства mcs-48

- •2.3. Формат слова состояния

- •2.4. Условия логических переходов

- •2.5. Память программ (пп)

- •2.6. Память данных (пд)

- •2.7. Организация ввода/вывода омэвм

- •2.9. Схема синхронизации и управления мк

- •2.10 Основные отладочные режимы работы

- •2.12. Система команд

- •2.12.1 Команды пересылок

- •2.12.4. Расширение адресного пространства ву

- •2.12.5. Команды передачи управления.

- •1. Коды условных переходов

- •2. Команды безусловного перехода

- •2.12.6. Команды управления режимом работы мк

- •3. Методы расширения адресного пространства.

- •Схемная реализация метода базовых регистров.

- •4. Семейство омэвм к1816ве31/51 (iMcs-51)

- •4.1. Назначение выводов

- •4.2. Структурная схема i8051

- •4.3.Арифметико-логическое устройство

- •4.4. Организация памяти

- •4.4.1. Память программ (пзу).

- •4.4.2. Память данных (озу).

- •4.5. Область регистров специального назначения (рсн).

- •4.6. Синхронизация омэвм

- •4.7. Порты ввода-вывода.

- •Устройство портов.

- •Особенности электрических характеристик портов.

- •4.8. Таймер-счетчики

- •Режимы работы т/с.

- •4.9. Система прерываний

- •Выполнение подпрограммы прерывания. Система прерываний формирует аппаратный вызов (lcall) соответствующей подпрограммы обслуживания, если она не заблокирована одним из следующих условий:

- •4.10. Последовательный канал.

- •Скорость приема-передачи.

- •4.11.Работа с внешней памятью микроконтроллера 8051.

- •4.12. Режимы микроконтроллера 8051 с пониженным энергопотреблением.

- •4.13. Система команд кр1816ве51

- •4.13.1. Общая характеристика.

- •4.13.2. Типы команд

- •4.13.3. Способы адресации

- •5 Старших разрядов адреса рсн

- •4.13.4. Команды логического процессора

- •4.13.5. Команды пересылок

- •4.13.6. Команды логической обработки

- •4.13.7. Команды арифметической обработки

- •4.13.8. Команда передачи управления

- •5. Расширения микропроцессоров семейства mcs-51/52.

- •5.5. Маркировка микроконтроллеров фирмы Intel.

- •5.6. Pca микроконтроллера 8051.

- •Регистр режимов pca таймера-счетчика cmod.

- •Регистр управления рса таймером-счетчиком ccon.

- •5.8. Модули сравнения-захвата pca микроконтроллеров mcs-51.

- •Регистр режимов модуля сравнения захвата ссарМn.

- •Режимы работы рса.

- •5.9. Режимы работы pca микроконтроллеров семейства mcs-51. Режим захвата.

- •Режим 16-разрядного программируемого таймера.

- •Режим скоростного вывода.

- •Режим сторожевого таймера (watchdog timer).

- •Режим генерации импульсов заданной скважности.

- •5.10 Аналого-цифровой преобразователь микроконтроллеров семейства mcs-51.

- •Adcon - Регистр управления преобразователем.

- •Addat - регистр результатав преобразования.

- •Dapr - регистр программирования опорных напряжений ацп.

- •Синхронизация ацп и время преобразования.

- •5.11. Таймер счетчик т/с2 микроконтроллера 8052.

- •Регистр управление таймера/счетчика 2 t2com.

- •Режимы работы таймера/счетчика 2.

- •Регистр режима таймера/счетчика 2 т2моd.

- •Дополнительный регистр приоритетов прерываний iрн.

- •6. Семейство mcs-251

- •7. Однокристальные микроконтроллеры Intel mcs-96.

- •7.1 Общая характеристика.

- •7.2. Структура микроконтроллера.

- •7.3. Периферийные устройства. Устройства ввода и вывода данных.

- •Устройство ввода и вывода дискретных сигналов.

- •Устройства ввода и вывода аналоговых сигналов

- •Устройства обмена данными с другими микроконтроллерами и центральным процессором.

- •Устройства приема и обслуживания запросов прерывания.

- •Устройства контроля правильности функционирования микроконтроллера.

- •7.4. Характеристики микроконтроллеров подсемейств.

- •7.5. Почему 80c196 быстрее, чем 8051?

Устройство портов.

Каждый из портов содержит регистр-защелку (SFR P0 — SFR P3), выходную цепь и входной буфер.

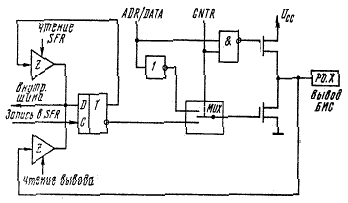

Рис.3.Порт P0

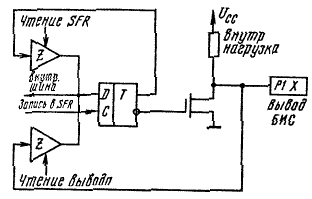

Рис.4.Порт P1

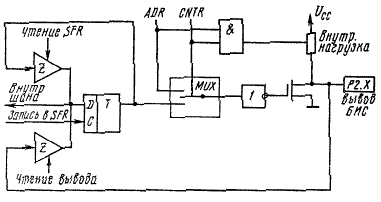

Рис.5.Порт P2

Рис.6.Порт P3

На рисунке изображены функциональные схемы регистров-защелок и буферов ввода-вывода всех портов микро-ЭВМ 8051. Каждый из разрядов регистра-защелки SFR является D-триггером, информация в который заносится с внутренней шины данных микроконтроллера по сигналу «Запись в SFR Pх» (х= 0, 1, 2, 3) от центрального процессорного элемента (CPU). С прямого выхода D-триггера информация мажет быть выведена на внутреннюю шину по сигналу «Чтение SFR Pх» от CPU, а с вывода микросхемы («из внешнего мира») по сигналу «Чтение выводов Pх». Одни команды активизируют сигнал «Чтение SFR PI», другие - «Чтение выводов РI».

Особенности электрических характеристик портов.

Выходные каскады триггеров SFR портов Р1 — РЗ выполнены на полевых транзисторах с внутренней нагрузкой, в то время как аналогичные каскады триггеров SFR P0—на транзисторах с открытым стоком. Каждая линия любого из портов может независимо использоваться как для ввода, так и для вывода информации (для линий портов P0 и Р2 это справедливо тогда, когда они не используются для обращения к внешней памяти).

Для перевода любой линии портов Р1 — РЗ в режим ввода информации необходимо в соответствующий разряд SFR занести 1. При этом выходной полевой транзистор отключается. Внутренний нагрузочный резистор как бы «подтягивает» потенциал вывода к напряжению питания, в то время как внешняя нагрузка может сделать его нулевым. Выходные каскады порта P0 имеют иную структуру. Нагрузочный полевой транзистор линии порта включен только тогда, когда порт выводит 1 при обращении к внешней памяти. В остальных случаях нагрузочный транзистор отключен. Таким образом, при работе в режиме обычного ввода-вывода информации (как, например, порт Р1) выходные каскады портов представляют собой ступени на транзисторах с открытым стоком. Запись 1 в соответствующий бит SFR отключает и второй транзистор, что приводит к тому, что вывод БИС оказывается под «плавающим» потенциалом. Это позволяет использовать линии порта P0 как выводы с высоко импедансным состоянием.

Поскольку выходные каскады портов P1 — P3 имеют внутреннюю нагрузку, при переводе в режим ввода информации они становятся источниками тока для микросхемы или транзистора, нагруженных на данный.

4.8. Таймер-счетчики

В базовых моделях семейства имеются два программируемых 16-битных таймера/счетчика (T/C0 и T/C1), которые могут быть использованы как в качестве таймеров, так и в качестве счетчиков внешних событий. В первом случае содержимое соответствующего таймера/счетчика (далее для краткости Т/С) инкрементируется в каждом машинном цикле, т.е. через каждые 12 периодов колебаний кварцевого резонатора, во втором оно инкрементируется под воздействием перехода из 1 в 0 внешнего входного сигнала, подаваемого на соответствующий (T0,T1) вывод микро-ЭВМ 8051. Так как на распознавание периода требуются два машинных цикла, максимальная частота подсчета входных сигналов равна 1/24 частоты резонатора. На длительность периода входных сигналов ограничений сверху нет. Для гарантированного прочтения входной сигнал должен удерживать значение 1, как минимум, в течение одного машинного цикла микро-ЭВМ.

Предназначены для работы в системах реального времени.

В МК строено 2 16-разрядныз таймер-счетчика, имеющих следующие адреса в области РСН:

TH0 – 8Ch

- TL0 – 8Ah

TH1 – 8Dh

TL1 – 8Bh

Т/с могут работать программно-независимо друг от друга.

Код величины начального счета заносится в регистры Т/С программно. В процессе счета содержимое регистров Т/С инкрементируется. Признаком окончания счета,' как правило, является переполнение регистра Т/С, т. е. переход его содержимого из состояния "все единицы" в состояние "все нули". Все регистры ТН0, ТН1, TL0, TL1 доступны по чтению, и, при необходимости, контроль достижения ребуемой величины счета может выполняться программно.

Режим работы задается управляющим словом TMOD, а управление – TCON.

Формат TMOD.

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

GATE |

C/T |

M1 |

M0 |

Gate |

C/T |

M1 |

M0 |

Т/С 0

Т/С 1

M1 |

0 |

0 |

1 |

1 |

M0 |

0 |

1 |

0 |

1 |

режим |

0 |

1 |

2 |

3 |

С/Т – выбор режима работы, устанавливается программно.

Если С/Т = 1 – режим счетчика. Входные сигналы поступают по Т0 (Т1), управление переходом 1 0.

Если С/Т = 0 – режим таймера. Входные сигналы поступают от внутреннего делителя опорной частоты fCR.

Gate – бит управления запуском таймера. Устанавливается программно.

Gate = 1 – запуск таймера осуществляется при TR0 (TR1) = 1 независимо от состояния по входу INT0 (INT1).

При работе в качестве таймера содержимое регистра Т/С инкрементируется в каждом машинном цикле, т. е. Т/С является счетчиком машинных циклов ОМЭВМ. Поскольку машинный цикл состоит из 12 периодов частоты синхронизации ОМЭВМ fXTAL, то частота счета в данном случае равна fXTAL/12.

При работе Т/С в качестве счетчика внешних событий содержимое регистра Т/С инкрементируется в ответ на переход из "1" в "0" сигнала на счетном входе ОМЭВМ. (вывод Т0 для Т/С 0 и вывод Т1 для Т/С 1). Счетные входы аппаратно проверяются в фазе S5P2 каждого машинного цикла. Когда проверки показывают высокий уровень на счетном входе в одном машинном цикле и низкий уровень в другом машинном цикле, регистр Т/С инкрементируется. Новое (инкрементированное) значение заносится в регистр Т/С в фазе S3P1 машинного цикла, непосредственно следующего за тем, в котором был обнаружен переход из "1" в "0" на счетном входе ОМЭВМ. Т. к. для распознавания такого перехода требуется два машинных цикла (24 периода частоты синхронизации ОМЭВМ fBQ), то максимальная частота счета Т/С в режиме счетчика равна fBQ/24.

Чтобы уровень сигнала на счетном входе был гарантировано зафиксирован, он должен оставаться неизменным в течение как минимум одного машинного цикла.

Формат TCON.

управление

прерываниями

управление

таймерами

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

TF1 |

TR1 |

TF0 |

TR0 |

IE1 |

IT1 |

IE0 |

IT0 |

Биты |

Наименование |

Назначение битов |

Примечание |

6 4 |

TR1 TR0 |

Биты выключения Т/С, отдельно для Т/С в и Т/С 1. TR=0 - выключен, TR=1 - включен. |

Биты устанавливаются и сбрасываются программно. Доступны по чтение |

7 5 |

TF1 TF0 |

Флаги переполнения Т/С |

Биты сбрасываются и устанавливаются аппаратно и программно. Доступны по чтению. |

2 0 |

IT1 IT0 |

Биты, определяющие вид прерывания по входам~tnt0, ~tnt1: IT=0 - прерывание по уровню (низкому) IT=1 - прерывание по фронту (переход из "1" в "О") |

Биты устанавливаются и сбрасываются программно Доступны по чтению |

3 1 |

IE1 1Е0 |

Флаги запроса внешних прерываний по входам INT0, INT1 |

Биты сбрасываются и устанавливаются аппаратно и программно Доступны по чтению. |

|

|

|

Биты 4,5 относятся к Т/С 0; биты 6, 7 -к Т/С 1. Биты 0,1 определяют внешние прерывания по входу ~INТ0, биты 2,3-по входу ~INT1 |

IT0 – разряд управления режимом прерывания. Устанавливается программно.

IT0 = 0 – запрос прерывания по входу INT0 обнаруживается по переходу 1 0 .

IT0 = 1 - запрос прерывания по входу INT0 обнаруживается по активному низкому статическому уровню.

IE0 – для запроса внешнего прерывания. Устанавливается аппаратно при обнаружении сигнала запроса внешнего прерывания. Сброс флага выполняется аппаратно при обслуживании прерывания только в том случае, когда прерывание было вызвано по фронту сигнала. Если прерывание было вызвано уровнем сигнала на входе ~INT0 (~INT1), то сброс флага IE должна выполнять программа обслуживания прерывания, воздействуя на источник прерывания для снятия им запроса

TR0 – разряд управления запуском таймера. Устанавливается или сбрасывается программно.

TF0 – флаг переполнения таймера. Устанавливается в 1 аппаратно при переполнении т/с, вызывая запрос прерывания от таймера. Сбрасывается после выполнения первой команды обслуживания прерывания.

Флаги TF0 и TF1, IE0 и IE1 программно доступны и могут быть установлены/сброшены программой. Используя этот механизм, прерывания по TF0 и TF1 могут быть вызваны (установка TF) и отменены (сброс TF) программой.

Схема инкремента предназначена:

- для увеличения на 1 в каждом машинном цикле содержимого регистров Т/С 0, Т/С 1, для которых установлен режим таймера и счет разрешен;

- для увеличения на 1 содержимого регистров Т/С 0, Т/С 1, для которых установлен режим счетчика, счет разрешен и на соответствующем входе ОМЭВМ (Т0 для Т/С 0 и Т1 для Т/С 1) зафиксирован счетный импульс.

Схема фиксации ~INT0, ~INT1, Т0, Т1 представляет собой четыре триггера. В каждом машинном цикле в момент S5P2 в них запоминается информация с выводов ОМЭВМ ~INT0, ~INT1, Т0, Т1.

Схема управления флагами вырабатывает и снимает флаги переполнения Т/С и флаги запросов внешних прерываний.

Логика управления Т/С синхронизирует работу регистров Т/С 0 и Т/С 1 в соответствии с запрограммированными режимами работы и синхронизирует работу блока Т/С с работой ОМЭВМ.

Аналогично для IT1 – TF1.