- •1. Однокристальные микро эвм (омэвм)

- •1.1. Общие особенности управляющих микроконтроллеров.

- •1.2 Структура мк-системы управления

- •1.3. Четырехразрядные микроконтроллеры.

- •2. Микроконтроллеры семейства mcs48

- •2.1. Состав семейства mcs-48

- •2.3. Формат слова состояния

- •2.4. Условия логических переходов

- •2.5. Память программ (пп)

- •2.6. Память данных (пд)

- •2.7. Организация ввода/вывода омэвм

- •2.9. Схема синхронизации и управления мк

- •2.10 Основные отладочные режимы работы

- •2.12. Система команд

- •2.12.1 Команды пересылок

- •2.12.4. Расширение адресного пространства ву

- •2.12.5. Команды передачи управления.

- •1. Коды условных переходов

- •2. Команды безусловного перехода

- •2.12.6. Команды управления режимом работы мк

- •3. Методы расширения адресного пространства.

- •Схемная реализация метода базовых регистров.

- •4. Семейство омэвм к1816ве31/51 (iMcs-51)

- •4.1. Назначение выводов

- •4.2. Структурная схема i8051

- •4.3.Арифметико-логическое устройство

- •4.4. Организация памяти

- •4.4.1. Память программ (пзу).

- •4.4.2. Память данных (озу).

- •4.5. Область регистров специального назначения (рсн).

- •4.6. Синхронизация омэвм

- •4.7. Порты ввода-вывода.

- •Устройство портов.

- •Особенности электрических характеристик портов.

- •4.8. Таймер-счетчики

- •Режимы работы т/с.

- •4.9. Система прерываний

- •Выполнение подпрограммы прерывания. Система прерываний формирует аппаратный вызов (lcall) соответствующей подпрограммы обслуживания, если она не заблокирована одним из следующих условий:

- •4.10. Последовательный канал.

- •Скорость приема-передачи.

- •4.11.Работа с внешней памятью микроконтроллера 8051.

- •4.12. Режимы микроконтроллера 8051 с пониженным энергопотреблением.

- •4.13. Система команд кр1816ве51

- •4.13.1. Общая характеристика.

- •4.13.2. Типы команд

- •4.13.3. Способы адресации

- •5 Старших разрядов адреса рсн

- •4.13.4. Команды логического процессора

- •4.13.5. Команды пересылок

- •4.13.6. Команды логической обработки

- •4.13.7. Команды арифметической обработки

- •4.13.8. Команда передачи управления

- •5. Расширения микропроцессоров семейства mcs-51/52.

- •5.5. Маркировка микроконтроллеров фирмы Intel.

- •5.6. Pca микроконтроллера 8051.

- •Регистр режимов pca таймера-счетчика cmod.

- •Регистр управления рса таймером-счетчиком ccon.

- •5.8. Модули сравнения-захвата pca микроконтроллеров mcs-51.

- •Регистр режимов модуля сравнения захвата ссарМn.

- •Режимы работы рса.

- •5.9. Режимы работы pca микроконтроллеров семейства mcs-51. Режим захвата.

- •Режим 16-разрядного программируемого таймера.

- •Режим скоростного вывода.

- •Режим сторожевого таймера (watchdog timer).

- •Режим генерации импульсов заданной скважности.

- •5.10 Аналого-цифровой преобразователь микроконтроллеров семейства mcs-51.

- •Adcon - Регистр управления преобразователем.

- •Addat - регистр результатав преобразования.

- •Dapr - регистр программирования опорных напряжений ацп.

- •Синхронизация ацп и время преобразования.

- •5.11. Таймер счетчик т/с2 микроконтроллера 8052.

- •Регистр управление таймера/счетчика 2 t2com.

- •Режимы работы таймера/счетчика 2.

- •Регистр режима таймера/счетчика 2 т2моd.

- •Дополнительный регистр приоритетов прерываний iрн.

- •6. Семейство mcs-251

- •7. Однокристальные микроконтроллеры Intel mcs-96.

- •7.1 Общая характеристика.

- •7.2. Структура микроконтроллера.

- •7.3. Периферийные устройства. Устройства ввода и вывода данных.

- •Устройство ввода и вывода дискретных сигналов.

- •Устройства ввода и вывода аналоговых сигналов

- •Устройства обмена данными с другими микроконтроллерами и центральным процессором.

- •Устройства приема и обслуживания запросов прерывания.

- •Устройства контроля правильности функционирования микроконтроллера.

- •7.4. Характеристики микроконтроллеров подсемейств.

- •7.5. Почему 80c196 быстрее, чем 8051?

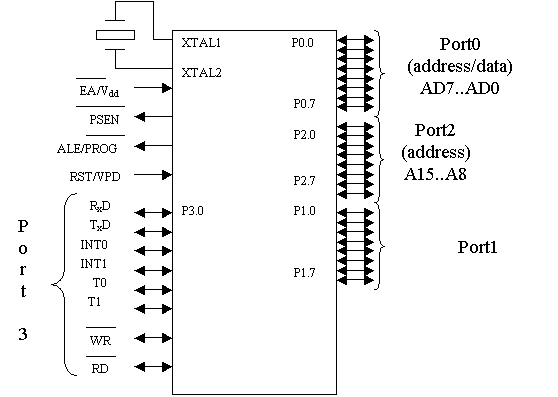

4.1. Назначение выводов

Микросхемы семейства КМ1816ВЕ751 конструктивно выполнены в металлокерамическом корпусе типа с прозрачной для ультрафиолетового излучения крышкой. Остальные рассматриваемые в данном описании ОМЭВМ семейства МК51 конструктивно выполнены в пластмассовых корпусах

32 линии вв/выв являются 32-мя индивидуально адресуемыми разрядами и объединяются в 4 8-разрядных порта.

Port 0 – восьми битный двунаправленный порт ввода-вывода информации: при работе с внешними ОЗУ и ПЗУ по линиям порта в режиме временного мультиплексирования выдается адрес внешней памяти, после чего осуществляется передача или прием данных. В первой части машинного цикла передает 8 мл.разр. А0-А7, во второй – данные

Port 2 – — восьми битный квази двунаправленный порт, аналогичный Р1; кроме того, выводы этого порта используются для выдачи адресной информации при обращении к внешней памяти программ или данных (если используется 16-битовая адресация последней). Выводы порта используются при программировании 8751 для ввода в микроконтроллер старших разрядов адреса:

Port 1 – восьми битный квази двунаправленный порт ввода/вывода: каждый разряд порта может быть запрограммирован как на ввод, так и на вывод информации, независимо от состояния других разрядов;

Port 3 – восьми битный квази двунаправленный порт, аналогичный. Р1; кроме того, выводы этого порта могут выполнять ряд альтернативных функций, которые используются при работе таймеров, порта последовательного ввода-вывода, контроллера прерываний, и внешней памяти программ и данных;

Если часть этих линий не используется, то они могут программироваться на ввод или вывод.

Входы управления

EA/VDD – вход выбора внешней памяти (EA = 1 – выполнение команды из внутренней памяти программ, EA = 0 – из внешней)

PSEN – сигнал разрешения памяти программ

ALE – строб записи адреса во внешний регистр-фиксатор

RST – начальная установка

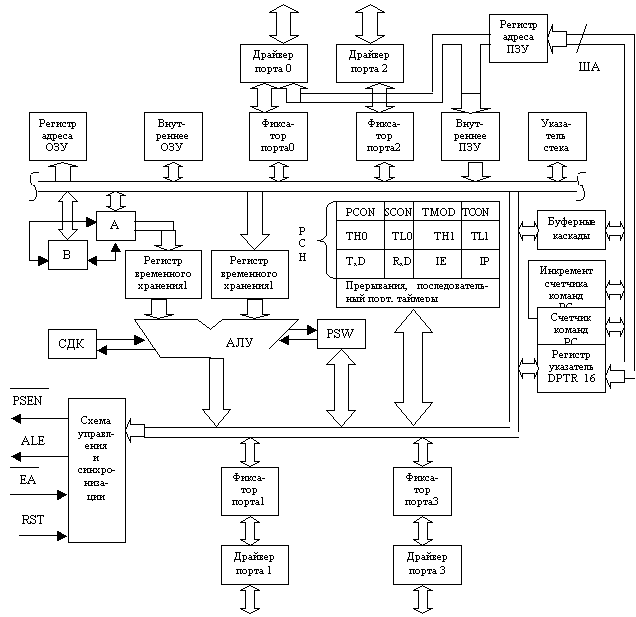

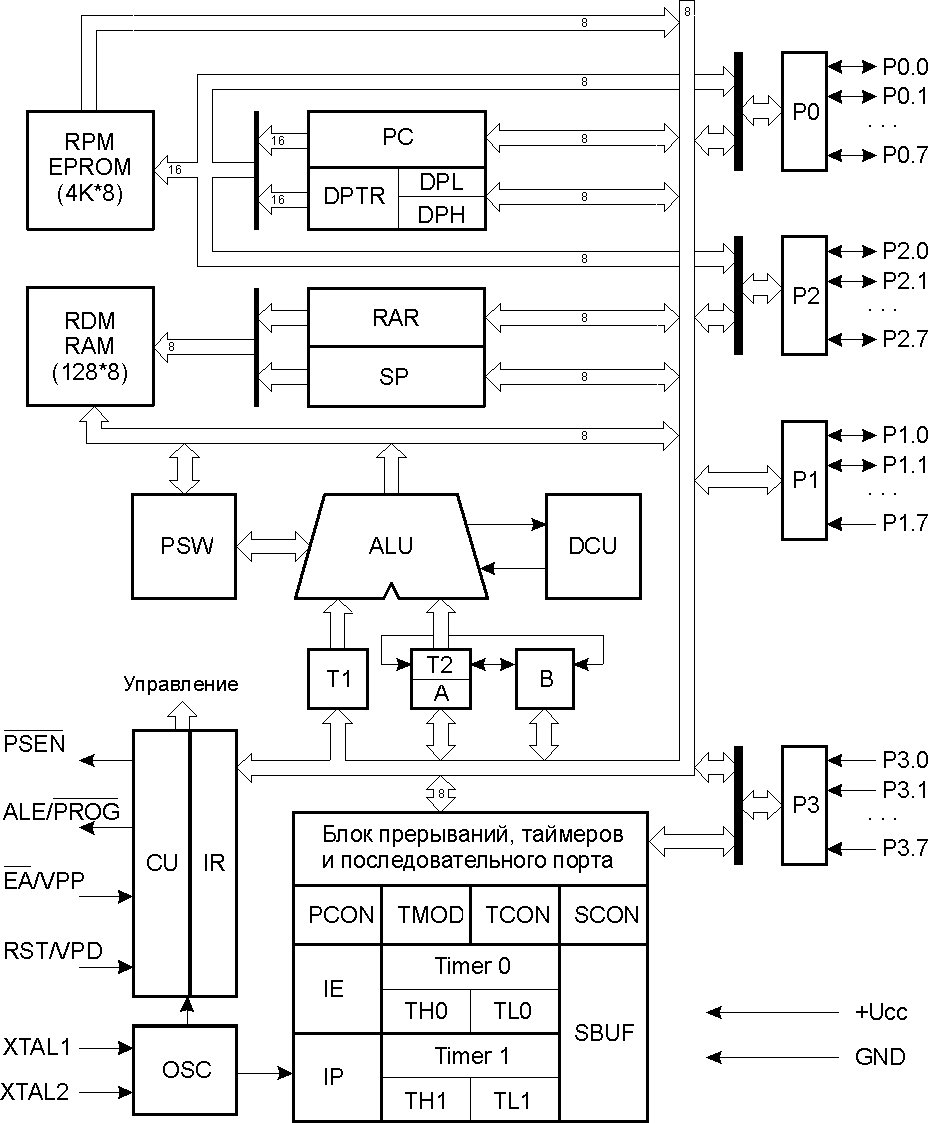

4.2. Структурная схема i8051

Другая структурная схема с указанием выводов

Логика ввода-вывода предназначена для приема и выдачи сигналов, обеспечивающих обмен информацией ОМЭВМ с внешними устройствами через порты ввода-вывода Р0-РЗ.

Регистр команд предназначен для записи и хранения 8-ми разрядного кода операции выполняемой команды, который с помощью дешифратора команд преобразовывается в 24-х разрядный код для ПЛМ, с помощью которой вырабатывается набор микроопераций в соответствии с микропрограммой выполнения команды. Регистр команд программно не доступен.

АЛУ представляет собой параллельное восьмиразрядное устройство, обеспечивающее выполнение арифметических и логических операций, а также операции логического сдвига, обнуления, установки и т. п.

АЛУ состоит из регистра аккумулятора, регистра временного хранения, ПЗУ констант, сумматора, дополнительного регистра (регистра В), аккумулятора, регистра состояния программы.

Аккумулятор А

ОМЭВМ относится к аккумуляторно-ориентированным архитектурам

А выполняет ряд дополнительных функций, специальных команд, вместе с тем ряд команд выполняются без участия аккумулятора.

Регистр-расширитель В.

Используется в операциях умножения и деления, в отдельных случаях – регистр общего назначения.

АЛУ комбинационное, поэтому для временного хранения операндов используется регистры временного хранения 1 и 2.

ПЗУ констант обеспечивает выработку корректирующего кода при двоично-десятичном представлении данных, кода маски при битовых операциях и кода констант.