- •1. Однокристальные микро эвм (омэвм)

- •1.1. Общие особенности управляющих микроконтроллеров.

- •1.2 Структура мк-системы управления

- •1.3. Четырехразрядные микроконтроллеры.

- •2. Микроконтроллеры семейства mcs48

- •2.1. Состав семейства mcs-48

- •2.3. Формат слова состояния

- •2.4. Условия логических переходов

- •2.5. Память программ (пп)

- •2.6. Память данных (пд)

- •2.7. Организация ввода/вывода омэвм

- •2.9. Схема синхронизации и управления мк

- •2.10 Основные отладочные режимы работы

- •2.12. Система команд

- •2.12.1 Команды пересылок

- •2.12.4. Расширение адресного пространства ву

- •2.12.5. Команды передачи управления.

- •1. Коды условных переходов

- •2. Команды безусловного перехода

- •2.12.6. Команды управления режимом работы мк

- •3. Методы расширения адресного пространства.

- •Схемная реализация метода базовых регистров.

- •4. Семейство омэвм к1816ве31/51 (iMcs-51)

- •4.1. Назначение выводов

- •4.2. Структурная схема i8051

- •4.3.Арифметико-логическое устройство

- •4.4. Организация памяти

- •4.4.1. Память программ (пзу).

- •4.4.2. Память данных (озу).

- •4.5. Область регистров специального назначения (рсн).

- •4.6. Синхронизация омэвм

- •4.7. Порты ввода-вывода.

- •Устройство портов.

- •Особенности электрических характеристик портов.

- •4.8. Таймер-счетчики

- •Режимы работы т/с.

- •4.9. Система прерываний

- •Выполнение подпрограммы прерывания. Система прерываний формирует аппаратный вызов (lcall) соответствующей подпрограммы обслуживания, если она не заблокирована одним из следующих условий:

- •4.10. Последовательный канал.

- •Скорость приема-передачи.

- •4.11.Работа с внешней памятью микроконтроллера 8051.

- •4.12. Режимы микроконтроллера 8051 с пониженным энергопотреблением.

- •4.13. Система команд кр1816ве51

- •4.13.1. Общая характеристика.

- •4.13.2. Типы команд

- •4.13.3. Способы адресации

- •5 Старших разрядов адреса рсн

- •4.13.4. Команды логического процессора

- •4.13.5. Команды пересылок

- •4.13.6. Команды логической обработки

- •4.13.7. Команды арифметической обработки

- •4.13.8. Команда передачи управления

- •5. Расширения микропроцессоров семейства mcs-51/52.

- •5.5. Маркировка микроконтроллеров фирмы Intel.

- •5.6. Pca микроконтроллера 8051.

- •Регистр режимов pca таймера-счетчика cmod.

- •Регистр управления рса таймером-счетчиком ccon.

- •5.8. Модули сравнения-захвата pca микроконтроллеров mcs-51.

- •Регистр режимов модуля сравнения захвата ссарМn.

- •Режимы работы рса.

- •5.9. Режимы работы pca микроконтроллеров семейства mcs-51. Режим захвата.

- •Режим 16-разрядного программируемого таймера.

- •Режим скоростного вывода.

- •Режим сторожевого таймера (watchdog timer).

- •Режим генерации импульсов заданной скважности.

- •5.10 Аналого-цифровой преобразователь микроконтроллеров семейства mcs-51.

- •Adcon - Регистр управления преобразователем.

- •Addat - регистр результатав преобразования.

- •Dapr - регистр программирования опорных напряжений ацп.

- •Синхронизация ацп и время преобразования.

- •5.11. Таймер счетчик т/с2 микроконтроллера 8052.

- •Регистр управление таймера/счетчика 2 t2com.

- •Режимы работы таймера/счетчика 2.

- •Регистр режима таймера/счетчика 2 т2моd.

- •Дополнительный регистр приоритетов прерываний iрн.

- •6. Семейство mcs-251

- •7. Однокристальные микроконтроллеры Intel mcs-96.

- •7.1 Общая характеристика.

- •7.2. Структура микроконтроллера.

- •7.3. Периферийные устройства. Устройства ввода и вывода данных.

- •Устройство ввода и вывода дискретных сигналов.

- •Устройства ввода и вывода аналоговых сигналов

- •Устройства обмена данными с другими микроконтроллерами и центральным процессором.

- •Устройства приема и обслуживания запросов прерывания.

- •Устройства контроля правильности функционирования микроконтроллера.

- •7.4. Характеристики микроконтроллеров подсемейств.

- •7.5. Почему 80c196 быстрее, чем 8051?

2.9. Схема синхронизации и управления мк

Назначение выводов (см. раньше)

2.10 Основные отладочные режимы работы

2.10.1 Сброс

USE для начальной установки

МК. Вход

![]() подключается в необслуживаемых системах

к к-ру, в обслуживаемых к кнопке.

подключается в необслуживаемых системах

к к-ру, в обслуживаемых к кнопке.

длительность 50 мс

длительность 50 мс

быстро разряжается и дольше заряжается.

Сбросы выполняют следующие функции:

Установка СК в 0;

Указатель стека в 0;

Выбирает банк регистров 0;

Выбирает банк памяти 0;

Устанавливает порт 0 в третье состояние;

Порт 1,2 – в режим ввода;

Запрещает внешние прерывания по входу INT и внутренние от таймера;

Останавливает таймер;

Отключает выходы синхроимпульсов от вывода Т0;

Очищает флаг таймера (сброс TF);

Сбрасывает F0, F1 – признаки пользователя.

Пошаговый режим

Предназначен для отладки программ с

остановкой после выполнения каждой

команды. Во время паузы адрес выдается

младшими разрядами

![]() по шине BUS (порт 0).

по младшим линиям

по шине BUS (порт 0).

по младшим линиям

![]() .

.

Работа в пошаговом режиме осуществляется

с помощью 2-х сигналов

![]() и ALE. Для перехода в

пошаговый режим по входу

устанавливается 0. Если команда состоит

из 2-х циклов, то после завершения второго

на выходе ALE устанавливается

единичный уровень, подтверждающий

состояние останова.

и ALE. Для перехода в

пошаговый режим по входу

устанавливается 0. Если команда состоит

из 2-х циклов, то после завершения второго

на выходе ALE устанавливается

единичный уровень, подтверждающий

состояние останова.

Переход в пошаговый режим и выход из него по уровням сигнала . Подтверждение останова по высокому уровню ALE.

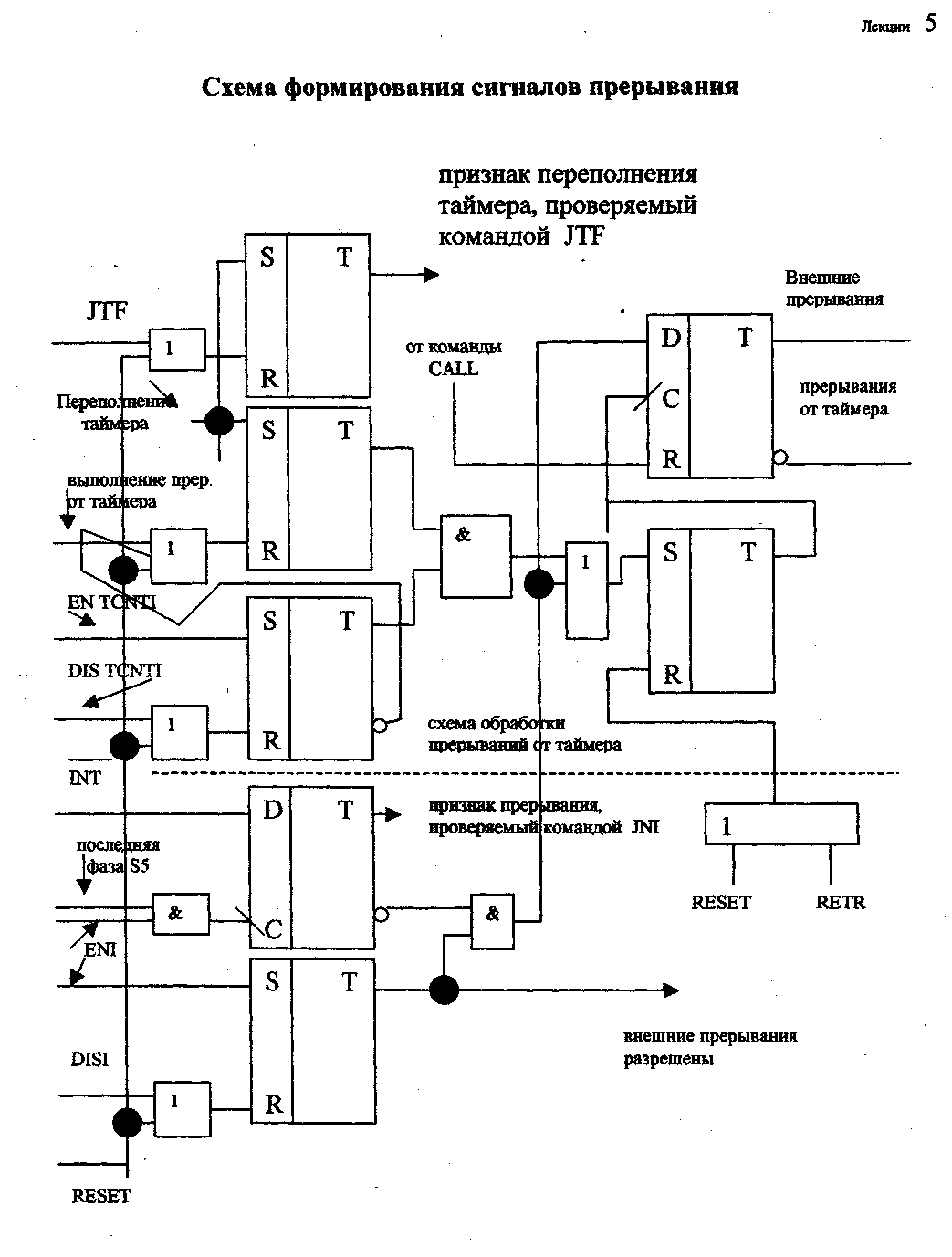

Система прерываний

одноуровневые, то есть новые запросы прерываний не воспринимаются до тех пор, пока не закончена обработка текущего прерывания и выполнена команда RETR. Источники прерывания внешние по входу INT и внутренние по переполнению таймер/счетчика с соответствующими адресами 0003, 0007.

Оба источника прерываний могут быть программно разрешены, запрещены.

Особенности системы прерываний.

Прерывания от внешних устройств могут объединяться через схему ИЛИ по входу INT , которая опрашивается в каждом машинном цикле во время действия сигнала ALE.

Прерывания от Т/С обрабатываются в той же последовательности. Программно разрешаются или запрещаются. Переход к точке 0007.

Независимо от маскирования прерываний, устанавливаются соответствующие триггеры признаков прерывания, которые анализируются командами условного перехода JTF и JNI. После выполнения команд триггеры сбрасываются. В самих процедурах обслуживания прерываний можно выделить следующие особенности:

если прерывание от таймера и внешние появились одновременно, то более высокий приоритет имеют внешние.

после обслуживания внешнего прерывания будет сразу же распознано прерывание от Т/С и выполнен переход в ячейку 0007.

Система прерываний имеет один внешний вывод, но искусственно можно создать второй, если предварительно в Т/С занести число FF и установить режим счетчика внешних событий, тогда перепадом 1/0 (Н/С) по входу Т1 можно организовать второй дополнительный источник запросов прерываний (вложений нет).

Прерывания разрешаются и запрещаются программно, но кроме того запрещаются сигналом RESET.

Для того чтобы процессор повторно не переходил на п/п обработки прерывания, после ее начала, необходимо снять сигнал сл входа INT, что должно быть обеспечено либо самими ВУ, либо программно от МК по одной из линий портов 1,2.